## UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

PROGRAMA DE MAESTRÍA Y DOCTORADO EN INGENIERÍA ELÉCTRICA – INSTRUMENTACIÓN

# LOW-VOLTAGE POWER SUPPLY DISTRIBUTION SYSTEM DEVELOPMENT IN A SCIENTIFIC SPACE MISSION

TESIS

QUE PARA OPTAR POR EL GRADO DE:

DOCTOR EN INGENIERÍA

PRESENTA: HÉCTOR HUGO SILVA LÓPEZ

TUTOR PRINCIPAL

Dr. GUSTAVO ADOLFO MEDINA TANCO, ICN-UNAM

COMITÉ TUTOR

Dr. AUGUSTO GARCÍA VALENZUELA, CCADET-UNAM

Dr. GABRIEL EDUARDO SANDOVAL ROMERO, CCADET-UNAM

#### **JURADO ASIGNADO:**

Presidente: Dr. Gabriel Eduardo Sandoval Romero

Secretario: Dr. Augusto García Valenzuela

Vocal: Dr. Gustavo Adolfo Medina Tanco

1 er. Suplente: Dr. Jorge Prado Molina

2 do. Suplente: Dr. Salvador Landeros Ayala

Lugar donde se realizó la tesis: INSTITUTO DE CIENCIAS NUCLEARES, UNAM

## TUTOR DE TESIS:

Dr. GUSTAVO ADOLFO MEDINA TANCO

FIRMA

#### ACKNOWLEDGMENT

This work was developed in the Detectors Laboratory at Nuclear Science Institute - UNAM, under the supervision of PhD. Gustavo Medina Tanco. The work was supported by the next projects associated to CONACyT: CONACyT 51843, the projects associated to RedCyTE: RedCyTE 51843, and the projects associated to PAPIIT-UNAM: PAPIIT 107413.

To my parents Antonio and Gustavo, who with their unconditional support have forged a platform of values and principles, which undoubtedly, had a huge impact throughout my professional career and as a human being. Thank you very much "I love you guys".

To my dear mothers María Elena & Irene, which with their words always encouraged me to give my best effort as well as meet my personal goals.

To my dear wife Angélica. For all her love, patience, advices and friendship without which this work had not been completed. Thank you my dear "You are my light, my love, my everything".

To my brother and sisters Iván, Yadira & Vero, who have shared with me all their life experiences making me feel a great confidence.

To my brothers in law Mauricio & Urso, for your patience and all those funny moments at sports.

To my mentors Gustavo, Lauro & Tsuno-san. Thank you very much for all the opportunities, expertise and friendship shared which undoubtedly meant strong tools to improve myself professional as well as personally.

To my tutors Eduardo, Augusto, Salvador and Jorge. Thank you for all your advices and confidence during very difficult moments throughout development of this work.

To my dear friends and colleagues Greta, Ivonne, Adrián, César, Javier, Sócrates & Leonardo. Thank you for sharing all your knowledge, support and friendship which meant a great opportunity to improve in many aspects of my life.

To my university. For the trust and support provided at anytime as well as all the resources and opportunities to be part of a select knowledge circle, that certainly makes me feel even more committed with the research field and technological development of this country.

## **C**ONTENTS

| Acronyms and Abbreviations                       |    |

|--------------------------------------------------|----|

| INTRODUCTION                                     |    |

| State of the art in the spacecraft power systems | 3  |

| I.1 Spacecraft Power Systems                     | 3  |

| I.2 Near-Earth Space Environment                 | 4  |

| I.3 Operational Spacecraft Environment           | 6  |

| I.4 State-of-the-art of Spacecraft EPS           | 10 |

| I.4.1 Direct Energy Transfer architecture        | 15 |

| I.4.2 Peak Power Transfer architecture           | 18 |

| I.4.3 Secondary power distribution               | 20 |

| I.4.3.a Low-voltage Power Supply                 | 22 |

| II. JEM-EUSO project                             | 29 |

| II.1 JEM-EUSO project                            | 29 |

| II.2 International Space Station                 | 31 |

| II.2.1 Utilization: JEM/Kibo-Exposure Facility   | 32 |

| II.2.2 Electrical Power System                   | 35 |

| II.3 JEM-EUSO instrument description             | 38 |

| II.3.1 Focal Surface                             | 39 |

| II.3.2 Elementary cell subsystem                 | 40 |

| II.3.3 High Voltage Power Supply subsystems      | 42 |

| II.3.4 Photo-detector Module subsystem           | 43 |

| II.3.5 Cluster Control Board subsystem           | 44 |

| II.3.6 Housekeeping subsystem                    | 45 |

| II.3.7 Central Processor Unit subsystem          | 46 |

| II.3.8 Data Storage subsystem                    | 46 |

| II.3.9 Clock Board subsystem                     | 47 |

| II.3.10 Global Position System Receiver                     | 48 |

|-------------------------------------------------------------|----|

| II.3.11 Atmospheric monitoring                              | 49 |

| II.4 Power distribution at JEM-EUSO instrument              | 49 |

| II.5 EUSO-Balloon instrument                                | 53 |

| III. Problem Statement                                      | 58 |

| III.1 Problem Statement                                     | 58 |

| III.2 Research objectives                                   | 59 |

| III.3 Significance of the research                          | 59 |

| IV. Low voltage power distribution at EUSO-Balloon          | 61 |

| IV.1 Requirements                                           | 61 |

| IV.1.1 Functional                                           | 62 |

| IV.1.2 Environmental                                        | 62 |

| IV.1.3 Interface                                            | 63 |

| IV.1.4 Schedule                                             | 63 |

| IV.2 Specifications                                         | 63 |

| IV.3 Constraints in the design                              | 64 |

| IV.4 Low-voltage power distribution architecture            | 65 |

| IV.5 Selecting appropriate power supply technology          | 68 |

| IV.5.1 Linear regulators                                    | 69 |

| IV.5.2 PWM Switching mode power supply                      | 69 |

| IV.5.3 High efficiency resonant switching mode power supply | 69 |

| IV.6 Developing power system design by specifications       | 70 |

| IV.6.1 Electrical parameters                                | 70 |

| IV.7 Low-voltage power supply module description            | 73 |

| IV.8 Low-voltage Power Supply design considerations         | 74 |

| IV.8.1 DC-DC converters selection                           | 75 |

| IV.8.2 Flectromagnetic compatibility                        | 79 |

| IV.8.3 Layout and grounding                      |  |

|--------------------------------------------------|--|

| IV.8.4 Thermal management                        |  |

| V. Tests and Results                             |  |

| V.1 Tests                                        |  |

| V.2 Electrical performance                       |  |

| V.2.1 Monitoring and activation of power modules |  |

| V.2.2 Mechanical assembly106                     |  |

| V.2.3 Subsystems weight                          |  |

| V.2.4 Heat dissipation                           |  |

| V.3 Thermo-vacuum                                |  |

| CONCLUSIONS                                      |  |

| WORK TO DO                                       |  |

| References                                       |  |

**APBUS** Attached Payload Bus

**ASIC** Application Specific Integrated Circuit

**AWG** American Wire Gauge

**BCDU** Battery Charge/Discharge Unit

**CAM** Camera

**CC** Contact Closure

**CCB** Cluster Control Board

**CLKB** Clock Board

**CMOS** Complementary Metal Oxide Semiconductor

CNES French Space AgencyCOTS Components Of The ShelfCPU Central Processor Unit

CW Cockcroft–Walton

dcEL DC Electronic Load

DC-DC Converter Unit

**DP** Data Processor

**DPA** Distributed Power Architecture

DPDT Dual Pole-Dual ThrowDSP Digital Signal Processor

**DST** Data Storage

**EAS** Extensive Air Shower

EC Elementary Cell Exposure Facility

**ELS** Electronics

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

EPS Electrical Power System

ESA European Space Agency

FEE Front End Electronic

**FPGA** Field Programmable Gate Array

FR Flame Retardant

**FSE** Focal Surface Electronics

GEO Geostationary Orbit

GND M Mechanical Ground

GON Gondola

**GPSR** Global Position System Receiver

**GRP** Ground Reference Point

**GTU** Gate Time Unit

**HEO** Highly Eccentric Orbit

**HK** House Keeping

**HL\_CMD** High Level Command

HVPS High Voltage Power Supply IBC Intermediate Bus Converter

IC Integrated Circuit

**IDAQ** Interface Data Acquisition Board

**IPBUS** Internal Power Bus

**IPC** Institute for Printed Circuits

IR Infrared

ISS International Space Station

JAXA Japanese Space Agency

**JEM-** Japanese Experiment Module – Extreme Universe Space

EUSO Observatory

LdReg Load Regulation

LEO Low Earth Orbit

**LIDAR** Light Detection and Ranging

LnReg Line RegulationLR Latching Relay

LVDS Low Voltage Differential SignalingLVPDS Low Voltage Power Distribution System

**LVPS** Low Voltage Power Supply

MAPMT Multi-Anode Photo Multiplier Tube

MBSU Main Bus Switching Unit

MCU Microcontroller Unit

MEO Medium Earth Orbit

Mfgr Manufacturer

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MPU Microprocessor Unit

NASA National Aeronautics and Space AdministrationNEMA National Electrical Manufacturers Association

niPOL non-isolated Point-Of-Load

**NOSYCA** New Operational System for the Control Aerostats

**Op-Amp** Operational Amplifier

**OPT** Optics

PCB Printed Circuit Board

**PCI** Peripheral Component Interconnect

PDMB Photo Detector Module Board

**PMMA** Polymethyl-methacrylate

PPBUS Primary Power Bus

PRM Pre-Regulator Module

**PSA** Pressure Sensitive Adhesive

**PWM** Pulse Width Modulation

**PWP** Power Pack

**PWS** Power

**RAID** Redundant Array of Independent Disks

RBI Remote Bus Isolator RF Radio Frequency

**RPC** Remote Power Controller

SATA Serial Advanced Technology Attachment SIREN Système d'Interface Reseau Nosyca

**SMD** Surface Mount Device

**SMPS** Switching Mode Power Supplies

**SPE** Single Photoelectron

**SPI** Serial Peripheral Interface

SSD Solid State Disk

**SSPC** Solid State Power Controller

SSU Sequential Shunt Unit

TDK TDK Lambda

TES Telescope

TH Through-Hole

TPW Traco Power

**UHECR** Ultra High Energy Cosmic Rays

**UV** Ultra Violet

**V&I** Voltage and Current

**VTM** Voltage Transformation Module

**XPP** XP Power

INTRODUCTION 1

A typical space flight system comprises three system segments which are coordinated and designed according to the mission objectives. These segments are related with: space, transfer and ground topics. The space segment comprises the spacecraft and its payload in orbit. The transfer section provides the transport for the spacecraft and its payload into space by a launcher (typically a rocket). Finally, a ground station is necessary in order to control and monitor the spacecraft and its payload as well as to distribute and process the payload data [1].

Mission types and payloads for spacecraft are many and varied. There are nine characteristic areas of applications for space flight missions: Earth and Weather observation, Technology testing, Fundamental research, Communication, Navigation, Military, Planetary exploration and Human space flight. Each one of these areas has its particular objectives which define the central application element of a space flight mission: the payload [1]. Successful payload operations open the door to mission success or put it in doubt. The sorts of payloads depend on the spacecraft mission, for example: radars, cameras, and sensors are essential in Earth and weather observations. But definitely, every payload needs power.

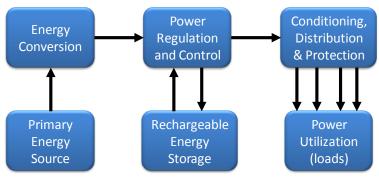

Electrical power is needed for the operation of all active spacecraft systems and subsystems. The electrical power system (EPS) of a spacecraft comprises power conversion, energy storage, regulation, power conditioning, protections, and power distribution to the various users via the on-board low-voltage power distribution (LVPD) system [1]. These stages are included in one of the following three sections: the *primary energy source* that basically converts a 'fuel' into electricity power, as an example a spacecraft that use a solar panel as the primary energy source, the 'fuel' in this case is the solar radiant energy; the *secondary energy source* that is required for storage and regulation of energy and subsequently deliver electrical power to spacecraft and its payload (when the primary system's energy is not available); and finally, the *power control and distribution network*, that is required to deliver appropriate voltage and current levels to all spacecraft loads when required [2].

The aim of this work is to describe the research, development and validation of a proposal of LVPD system for a sub-orbital particle physic instrument, which represents a fully operational prototype for the space instrument JEM-EUSO (Japanese Experiment Module – Extreme Universe Space Observatory).

The work is comprised by five chapters. In chapter one, it's given a concise background about near-earth space environment in order to establish the operational environmental conditions of a spacecraft. After that, is summarized the research about state-of-the-art of a spacecraft EPS.

2 Introduction

Finally, the research will focus on the advances of LVPS architectures at industrial and telecom applications. The latter, in order to propose an optimal solution for secondary power distribution section of a spacecraft instrument in the fundamental physics research field.

The second chapter is devoted to explain the complexity of JEM-EUSO project, giving a concise description of hierarchical architecture of the instrument, as well as a brief subsystems description. Therefore, it will be justified the necessity of a reduced version test bench of JEM-EUSO instrument: EUSO-Balloon. In the final section, are explained the objectives of EUSO-Balloon instrument as well as its main components.

In chapter three, it is defined the problem statement, the research objectives and the significance of research since fundamental physics point of view and technical development. Although the fourth chapter starts with EUSO-Balloon requirements and specifications, the purpose of this chapter is to describe the development of the LVPS strategy proposed for a sub-orbital scientific mission regarding functional, environmental and communication requirements.

On other hand, chapter five describes specific tests related to electrical, data management and thermo-vacuum performance of different modules that comprise the LVPS subsystem at EUSO-Balloon instrument. The tests performed have the purpose to guarantee the safe operation of the subsystem developed at low pressure conditions.

Finally, conclusions and to do work sections are stated for improving the development of LVPD subsystems in the near-Earth space field projects.

## I.1 Spacecraft Power Systems

In space, the EPS generates, stores, conditions, controls, and distributes power within the specified voltage levels to all bus and payload equipment. The protection of the power system components in case of all credible faults is also included. The basic components of the photo-voltaic power system are the solar array, solar array drive, battery, battery charge and discharge regulators, bus voltage regulator, load switching, fuses, and the distribution harness. The harness consists of conducting wires and connectors that connect various components together.

The near-Earth space environment, i.e., thermosphere and ionosphere, presents a substantial risk to space systems. The spacecraft power system must withstand the space environment and meet full performance specifications over the entire mission life, starting from the launch phase to disposal at the end of life. In that way, the environmental factors also affect the overall design of all other components of the power system [3].

## **I.2 Near-Earth Space Environment**

A spacecraft is affected by physical conditions in space which go far beyond the well-known environmental requirements on Earth. Typical features of the space environment are high vacuum, short-wave solar radiation (electromagnetic waves), ultraviolet X-rays and gamma radiation from the galactic background, high-energy particles (electrons, protons, neutrons and alpha particles), the cold background of space, microgravity, aerodynamic drag of the atmosphere at low Earth orbits, and the influence of atomic oxygen. These conditions have to be considered during the design and realization of a spacecraft [1].

The conditions depend on the orbit of the mission. The main distinctions are:

- Low Earth Orbit (LEO).

- Medium Earth Orbit (MEO).

- Geostationary Orbit (GEO).

- Highly Eccentric Orbit (HEO).

- Interplanetary space trajectories.

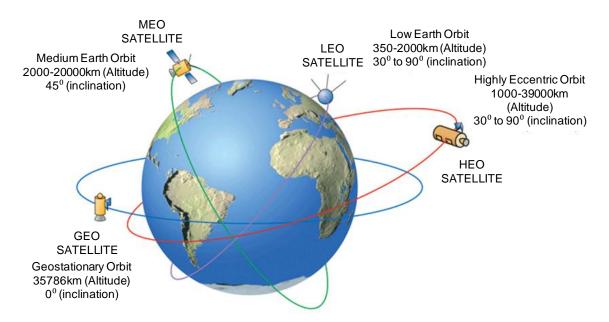

LEO is approximately a circular orbit at low altitude. The International Space Station (ISS) operates in LEO. Most communications satellites operate in GEO, but some newer constellations are planned and/or placed in LEO between 350 and 2000-km altitudes and 30 to 90° inclinations (see figure 1). Being closer to the Earth, smaller and simpler satellites can be used in this orbit. On the negative side, LEO communications satellites require tracking of omni-directional antennas, and many of them are needed for wide coverage [3].

MEO sometimes called Intermediate Circular Orbit (ICO) because is the region of space between LEO and GEO. The orbital periods of MEO satellites range from about 2 to 12 hours. Some MEO satellites orbit in near perfect circles, and therefore have constant altitude and travel at a constant speed. Due this, a fleet of several MEO satellites, with orbits properly coordinated can provide global wireless communication coverage. Because MEO satellites are closer to the earth than geostationary satellites, earth-based transmitters with relatively low power and modest-sized antennas can access the system. Because MEO satellites orbit at higher altitudes than LEO satellites, the useful footprint (coverage area on the earth's surface) is greater for each satellite. Thus a global-coverage fleet of MEO satellites can have fewer members than a global-coverage fleet of LEO satellites [3].

GEO orbit is a very special geosynchronous orbit, and, in fact, is unique. It is exactly circular with a radius of 35,786km in the Earth's equatorial plane with zero degree inclination and zero eccentricity.

A satellite placed in this orbit is synchronized with the Earth's rotation rate and direction (eastward). It does not move with respect to the Earth, and sees the same object on the Earth steadily. The orbit period is the same as that of the Earth's rotation, i.e., 23 h 56m 4.09 s. As a result, the satellite's beam-to-Earth and the ground station's beam-to-satellite are steady in position. This simplifies the design and operating requirements of both the satellite and the ground station. However, it takes more fuel to reach and maintain the geostationary orbit than any other orbit around the Earth [3].

HEO, also called Highly Elliptical Orbit Molniya, represents one specific orbit named in that way after the Molniya Soviet communication satellites which used them. The advantage of this orbit is a good coverage of the entire northern hemisphere. The disadvantage is no coverage over the southern hemisphere. Moreover, it requires more satellites and needs two tracking antennas at each ground stations [3].

Figure 1. Satellite Earth orbit map [4].

The interplanetary space trajectories have remained an activity of unmanned space flight except for the Apollo missions to the Moon. Over the decades dozens of space probes have flown to all planets (except Pluto) as well as to many asteroids and comets. In many cases these were not only fly-bys but even orbiting and landing missions. For instance, robotic vehicles have been deployed on Mars, or cometary material has been returned to Earth. Special challenges of interplanetary space flight are significant signal latency, long flight time, and navigation. Moreover, a sufficient power supply is one of the greatest problems in the outer Solar System [1].

## I.3 Operational Spacecraft Environment

Spacecraft operation is characterized by its remoteness from the Earth and thus the loss of the Earth's protective shield, namely, the atmosphere. This atmosphere evidently provides a suitable stable environment in which the human species has been able to evolve. Coupled with the gravitational force of the Earth, 'the one *g* environment', it provides familiarity in design and its removal has significant and sometimes unexpected implications [1].

Before considering the environment, it should be noted that the different phases in the life of a space vehicle, namely, manufacture, pre-launch, launch and finally space operation, all have their own distinctive features. Although a space vehicle spends the majority of its life in space, it is evident that first it must survive to terrestrial conditions like dust and humidity for complete success. Whilst the manufacturing phase is not part of this work, it has an effect upon the reliability and the ability to meet design goals [1].

In the launch phase the design, manufacture and assembly of a large spacecraft, and its final integration into a launch vehicle is a lengthy process, lasting typically 5 to 10 years. Components and subsystems may be stored for months or even years prior to launch. Careful environmental control during such periods is essential if degradation of the spacecraft system as a whole is to be avoided [2]. On the other hand, during the launch phase high levels of acceleration, shock, and vibration are present. The resulting stress levels, varying with the launch vehicle, have effects on the power system design, particularly on the solar panels. For example, in transfer orbit, the solar panel is still folded, but must withstand the accelerating force at perigee and the braking force at apogee. Thermally, the outer solar panels must withstand the Earth's heat radiation and albedo, in addition to the solar radiation, without exceeding the specified temperature limit [3].

Now then, regarding the environmental conditions, the lack of gravity and atmosphere in space has significant effects on the power system design. Zero gravity and vacuum jointly deprive all spacecraft equipment from the natural convection cooling which is normal on Earth. The thermal design in space, therefore, depends primarily on conduction cooling and, to some extent, on radiation cooling. The heat rejection to the outer space, however, must depend only on radiation cooling. On the other hand, the vacuum causes sublimation and outgassing, more in some materials than others. The subsequent condensation of the sublimed vapor on cold surfaces can cause short circuits in electrical parts. Since zinc has a high sublimation rate, and some polymers have high outgassing rates, their use in space is restricted. The solar array current collecting slip rings and brushes can experience cold welding under high contact pressure in a vacuum. The use of lubricants having low sublimation rates, or keeping them in sealed pressurized enclosures, is therefore important [3].

There are other issues that constrain the power system design like Earth's magnetic field, solar flares and solar wind, charged particles that comes with the sun's radiation, meteoroids and debris.

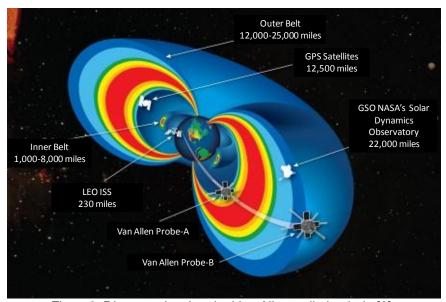

The Earth's magnetic field covers the magnetosphere, a doughnut shaped region of space influenced by the Earth's magnetic field. It acts on the electrons and protons coming from the space. The Van Allen radiation belts (see figure 2) are parts of the magnetosphere that contain a large number of particles. The magnetosphere normally shields the Earth from these particles. However, when a disturbance on the sun radiates an abundance of particles, some reach the Earth's atmosphere near the magnetic poles and cause a glow known as an aurora, popularly known as the northern lights (or the southern lights, in the southern hemisphere) [3].

Figure 2. Diagram showing the Van Allen radiation belts[6].

Besides, the sun continuously radiates energy in several forms: visible light, invisible infrared, ultraviolet, X-rays, gamma rays, radio waves, electrons, protons, and plasma (electrically charged hot gas). The abundance of charged particles that come with the sun's radiation makes space a hostile environment. The common sources of charged particles in the space environment are as follows:

- Solar radiation, consisting of mostly electrons and protons from the sun.

- Solar wind brings bursts of charged particles in addition to the normal radiation from the sun. It is primarily made of protons and some electrons radiating from the sun.

- Cosmic radiation comes mostly from the outer space and some probably from the sun. It consists approximately of 85% proton, 12% alpha particles, and 3% electrons.

In addition to the last total dose effects, which are caused by deposition of energy by many particles, there is a set of phenomena that are caused by single particles, called single event effects. The first one, single event upset occurs when a heavy ion is incident on the sensitive area of an integrated circuit, producing sufficient charge in the form of electron-hole pairs to cause a change in the logic state of the device. This type of error is known as a 'soft' error since it is reversible and causes no permanent damage. However, if it occurs in critical circuitry such as a control system or decision-making logic, then it can have serious consequences on the spacecraft operation generating false commands [2].

A single-event latch-up occurs when the passage of a single charged particle leads to a latched low impedance state in a parasitic PNPN devices in bulk complementary metal oxide semiconductor (CMOS) material, and it can result in burn-out. A more serious effect is single-event burn-out which occurs when an incident ion produces a conducting path-in a metal oxide semiconductor field effect transistor (MOSFET), for example, that causes the device to latch-up; if this condition continues for a sufficiently long time then the device could be completely burnt out and destroyed [2]. Finally, single-event-induced dark current is caused by the passage of a particle which causes displacement damage in a single pixel. Tests must be conducted at the subsystem and at the total system levels to ensure the tolerance levels are met and that catastrophic failure is impossible. Error correction techniques applied at the systems level include: redundant units, selferror-detecting and error-correcting checking circuits, codes. breakpoint reasonableness testing, and repetitive execution and watchdog timers (time-related solutions) [5].

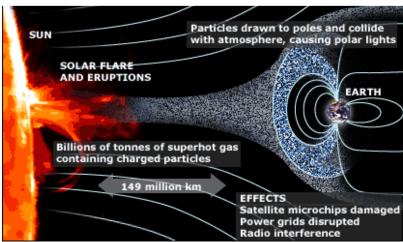

There are another two factors that contributes to electronic systems damage in space, solar wind and solar flares. A continuous stream of protons, electrons, and ionized gas leaving the sun and sweeping the solar system is called solar wind. It is very thin, containing approximately 5 charged particles per cubic centimeter of space. The solar wind streams constantly, but not evenly. When these particles flow past the Earth, some get trapped in the Earth's magnetosphere. On the other hand, a solar flare is a gush of ionized gas with charged particles spewed out by the corona, the sun's glowing outer shell. It is associated with dark sunspots bounded by intense magnetic fields that come and go in 11-year cycles. The flare can cause auroras and disturb radio signals on Earth. The ionized gas is extremely hot, such that atoms of hydrogen and helium are homogenized into diluted plasma, composed mainly of negatively charged electrons and positively charged protons (see figure 3). Although this constitutes a million tons of matter moving at a million miles per hour, its density is so low that it is still considered a vacuum. Therefore, their energy levels and the corresponding probabilities that must be considered in designing the power system are mutually agreed upon by the satellite customer and the manufacturer [3].

Figure 3. Solar activity and its effects on Earth[7].

Major effects of solar flares and geomagnetic storms on the spacecraft power system are:

- Rapid degradation of the solar array power generation. This is a life shortening, not a life threatening, effect.

- Common-mode electromagnetic interference (EMI) noise entering the electrical power system components through exposed cables. This can upset the power system possibly causing a permanent damage.

Another important aspect and related with solar array degradation is the atom oxygen which is present in LEO. It severely erodes some materials, such as silver, which is extensively used in the solar array construction. Similar erosion is also seen in some electrical insulation such as Kapton and silicon rubber. The erosion comes not only from the chemical activity, but also in large part by the atoms travelling at several km/s velocities relative to the spacecraft. In addition to the erosion (surface recession), atomic oxygen can also form stable oxides on the metal surface. For these reasons, exposed bare silver in solar arrays and silicon or Kapton insulation on electrical wires are undesirable [3].

Therefore, all these phenomena affect in some way to spacecraft systems. As a result, different electronic devices manufacturers develop ICs that were submitted to very well planned tests simulating similar space environmental contingencies. In the next section, it is given a concise description about state of the art, in the research, of EPS on-board scientific space missions. The later will help to understand the goal of this work, which is focused in the conditioning and distribution of low-voltages levels at different loads on the spacecraft.

## 1.4 State-of-the-art of Spacecraft EPS

Different space agencies, for instance, NASA (National Aeronautics and Space Administration), ESA (European Space Agency), JAXA (Japan Aerospace Exploration Agency) and CNES (Centre National d'Études Spatiales) are constantly developing new philosophies about next generations of spacecraft power systems regarding specific key points in future missions. Some of these issues, addressed by ESA in [8], are focused on higher power demand and system efficiency, reusability, adaptability and flexibility, decrease in system mass, size and cost, as well as modularity and standardization. The later will help to meet the main goal of EPS, for a determined space mission, which is to ensure reliable delivery of electrical power and prevent failure propagation, under all foreseeable conditions, during all mission phases.

Power requirements in very early satellites were several watts. In today's communications satellites, it is several Kilowatts and is growing. Furthermore, some strategic defense spacecraft power requirements are estimated to be in hundred of Kilowatts and some concepts require hundreds of Megawatts of burst power [3]. Owing solar radiation represent the only external source of energy available in space, any spacecraft power system needs a solar array structure in order to achieve that energy; if there is not such structure, it must carry its own source of energy.

Therefore, in a very general way figure 4 shows the basic block components of the spacecraft power system. They are the primary energy source, energy conversion, power regulator, rechargeable energy storage, power conditioning, distribution and protection, to be acquired by user's equipment (load) in power utilization block.

Figure 4. Basic block components of EPS on spacecraft.

Within the candidates for the primary energy source are: solar radiation, radioisotopes, nuclear reactors and electrochemical fuel. The block of energy conversion may be photovoltaic, thermoelectric, dynamic alternator, full cell or thermionic. Finally, energy storage is typically electrochemical, although flywheel technology was also used at NASA Glenn research center [3].

On the other hand, the block of conditioning, distribution and protection provides bus voltage conditioning converting unregulated battery voltage into a semi-regulated low voltage line; meanwhile distribution section distributes the different voltage to the payload and experiments. Within this block, the third very important task is the power system protection provided against faults and short-circuits in the subsystems and bus circuitry.

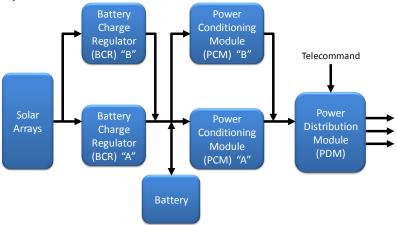

Therefore, the figure 4 shows the basic block diagram of EPS in a spacecraft; these blocks are comprised by several modules depending on target mission. In the case of microsatellites development, as example Tsinghua-1 [9], the power system design reflects the need for autonomous operation, independent of all other systems, as is practiced and described on EPS of small satellites [10]. Autonomy is obtained using converter regulation methods and through total redundancy when mass issue is not a critical constraint. The redundant systems automatically switch to the other system in the event that a fault is detected. As reference, figure 5 shows the components included in EPS of micro-satellites.

Figure 5. Micro-satellite power system block diagram.

In figure above, and for the particular case of Tsinghua-1 micro-satellite, the redundant system is comprised by two identical BCR's capable of deliver full power from solar panels to the battery and for the rest of spacecraft. Meanwhile, the two PCMs ensure regulated power through convert the raw battery voltage into a regulated voltage line for other subsystems. Both modules (BCRs and PCMs) are equipped with control and regulation circuitry; furthermore, are capable to detect faults and also to switch the cold redundant systems for reliable and safe operation.

On the other hand, the area of solar panel plays a very important role in determining the total power the solar panel should give. The parameters involved on such calculation are the power budget, orbit, placement and packing. Equations 1-3 help to calculate the power that solar panel should generate ( $P_S$ ), the effective solar area that must meet ( $A_S$ ), and the area of each panel ( $A_P$ ), respectively as is described in [9].

$$P_n * (1 + M_p)/E_p = P_S * I_i * I_S * e^{-fN}$$

(1)

$$A_S * 1353 * U = P_S \tag{2}$$

$$A_P = P_n / (1353 * I_i * I_S * e^{-fN} * T * P_a * U$$

(3)

In equation 1, are involved power and orbit parameters like  $P_n$  as power budget,  $E_p$  as efficiency of power system, and  $M_p$  as the power margin. Meanwhile, orbit parameters are  $I_s$  which is the sunlight factor (typical 1/3 of eclipse time),  $I_i$  used as illumination factor (typical value of 0.7) and the degradation rate,  $e^{-fN}$ , where N represents the life time and f have typical value of 0.025. In equation 2, is required the efficiency of solar cells (U) which values are 14% in case of Si, and 18% for GaAs. Therefore, from the data above it can be obtained the effective area of solar panel,  $A_S$ . Finally, in order to calculate the area of each panel equation 3 is used. In this equation, T depends of shape solar array, in the case for Tsinghua-1, shape like a box is considered, thus a factor of 1.25\*A is used (A: section area of one surface).  $P_a$  is a factor (80%) utilized when cannot be used the total area of solar panel to place solar cells.

As a last block, the PDM has the task to distribute the different voltages to the payload and experiments. A second very important task of this block is to protect the power system against faults and short-circuits in the subsystems and bus circuitry. Furthermore, the distribution can be performed in three different ways, as is described in [9]. The first one is by Hard Wired, this means that the subsystem is directly connected to the EPS. The second one is by fused lines, the subsystem is connected to EPS via a fuse protecting the power system from short-circuits down the line. However, in [9] is stated that the most flexible way of distribution is via power switch. The last has two main functions; is possible to switch the subsystems On/Off by tele-commnads (TC), and also can be considered as electronic fuse that automatically switches off when the current drawn, by the subsystem, becomes larger than a pre-programmed value.

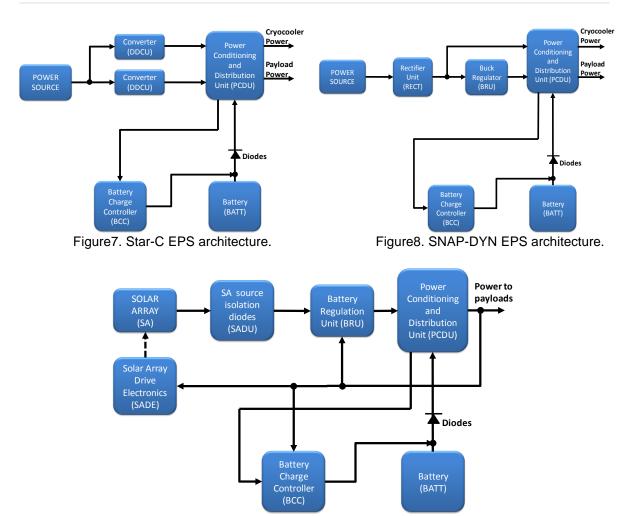

Now then, all above described was based on the utilization of the most common used power source in space, solar radiation. However, some surveillance satellites have considered and compared different power sources, as a part of its EPS, as is showed and evaluated in [11]. The three sources selected were a PV concentrator and two fission reactors which were evaluated for their compatibility with payload operation. Figures 6, 7 and 8, show the block diagrams of proposed EPS architectures for the three sources. Note that these sorts of satellites will consist of: A power control & distribution unit (PCDU) which contains monitoring and fault protection capabilities for all spacecraft power. Two, or more batteries for energy storage. A battery charge controller (BCC) and voltage converters or regulators, as required by the particular power source.

Figure 6. Solar array EPS architecture.

The above three architectures are quite similar. The main difference is that for solar array source, isolation diodes for solar array (SADU), solar array drive electronics (SADE) and a bus regulator unit (BRU) are added. On the other hand, radiation is the major concern with reactors; they are mounted on booms to reduce the spacecraft dosage. This in turns increases weight and complicates the spacecraft attitude control system. Furthermore, electronics parts of spacecraft still require additional shielding.

As conclusion for surveillance satellites in [11], states that solar array architecture meets with the main constraints, weight and compatibility with payload operation, but possibly not meet some of the survivability requirements. The reactors are compact, but relatively heavy. However, appears like that, with development will meet weight limits [11].

Another kind of application, in satellites, is those based on radar payload on a space-based radar (SBR) satellite. The major issues are founded in generating and distributing power, specifically, in the power distribution and control system, as is stated in [12]. The EPS of SBR differs from existing systems in three major ways. First, it is required tens of kW of dc from radar payload. Second, the antenna would contain many solid-state transmit/receive modules feeding than 30,000 radiating elements distributed over a large area. Finally, the radar will demand critical transient response from dc power supply.

The principal challenges in designing at [12], are the average of dc power supply, orbit, and number of loads. The last, represents the principal constraint for power conditioning and distribution system. Fundamental power architecture distribution to be implemented (radial, trunk, ring, etc.) is another very important task to be defined, as well as, location of various elements and modules (constrained by presumption as to the basic geometry of the spacecraft), and component technology to be used are fully related.

On the other hand, the choice of bus voltages is a question of compromise. Meanwhile, high voltage had the advantage of reducing the conductor mass and the power loss. Against this, was the need to limit the voltage to prevent plasma leakage and breakdown, and reduce the stresses in semiconductor devices used in the associated converters and regulators.

Finally, and regarding management and control autonomy, implementation of onboard control circuitry for data management becomes financially feasible when volume of data involved is relatively small. So caution must be exercised regarding number of on-board elements in control systems are considered. As a conclusion, in this sort of satellites, power conversion and conditioning scheme result in a major concern. A principal design choice is whether to use central or local conditioning. In central approach lightweight and efficient (>85%) converters in the 5 to 10kW range would need to be develop using maybe individual converters rated over 100W each one. On the other hand, local conversion at the T/R module level would need small converters rated, maybe, up to 5W and efficiencies of 90 to 95%. However, it is necessary to assure enough space inside each transmit /receive module.

Now then, taken as example larger spacecrafts as reported in [13], the power requirements of last have increased from tens of watts up to the present programs requiring powers in the range of 10 to 300kW in space stations. In these cases spacecraft power systems require special attention mainly because of two reasons. First, due to high power demanded and inevitable subsystem weight; and second, for its aim, which is the efficient transformation of the available energy into electrical power. Besides, properly distributed architecture to other systems and payloads has to be selected.

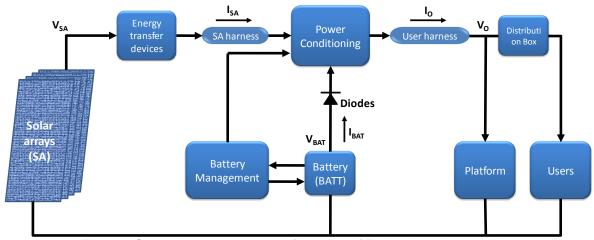

For large satellites, in applications as Earth-orbiting [14], the EPS is composed of solar arrays, batteries for provisional energy storage, power conditioning and harness for energy transformation and distribution, as is showed in figure 9. The power conditioning block associated with spacecraft power system has been the "heart and mind" of the system itself [13].

Figure 9. General power system configuration of Earth-observing satellite.

The power conditioning system converts the requested energy into an electrical form  $(V_O)$ , distributed to the users network through one or several bus bars, and guarantees the reliable working of the system. According to the adopted power system topology, the voltages of the solar array  $(V_{SA})$ , the battery  $(V_{BAT})$  or the bus bars  $(V_O)$  may be identical or independent. The power system is responsible for the correct operation of the payload internal power conversion and distribution network. This system is composed of several functions which are supplied under a centralized or decentralized form via dc/dc or dc/ac converters connected to the distribution box unit (DBU) [13]. On the other hand, the platform is responsible for spacecraft in-orbit servicing functions as attitude control, thermal, housekeeping, and data handling, as well as the energy supply of the complete satellite.

Thus, the basic components of PV-battery system (as showed in figure 9), are extremely important in selecting the power system architecture that is most suitable for the mission. The following architectures represent the EPS configurations that would optimize the system performance for a given mission.

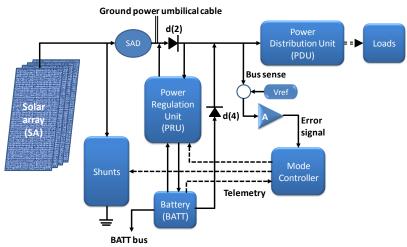

## I.4.1 Direct Energy Transfer (DET) architecture

Here, the solar power is transferred to the loads with no series component in between. The necessary exceptions are: the *slip rings*, which provide a rotary joint between the Earth-facing spacecraft body and the sun-facing solar array; and the power distribution unit (PDU), consisting of load switching relays and fuses to protect the power system from faults in the load circuits.

The DET can be further subdivided into three classes: the fully regulated bus, the sunlight regulated bus, and the unregulated bus voltage power system. The components and operation of these busses are similar, except that the latter has no battery discharge converter (or regulator) in the power regulator unit (PRU).

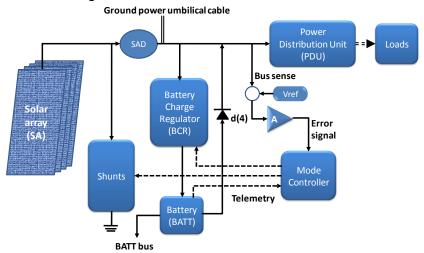

Figure 10 shows the fully regulated bus DET architecture. In the fully regulated bus the typical bus voltage variations is  $\pm 2\%$  to  $\pm 5\%$  of the nominal voltage. This architecture in normal operation maintains the bus voltage between the specified upper limit and the lower limit.

Figure 10. Fully regulated bus direct energy transfer architecture.

The components and its description are as follows. The solar array is generally divided into many parallel circuits (strings), each with isolation diodes so that a failed string would not draw power from the healthy ones. These diodes may be located inside the PRU for protection, or on the back of the solar array exposed to the environment. The electrostatic discharge induced transient voltage suppressing snubber capacitors may be located inside or outside. The bus diodes pair d(2), typically Schottky diodes, prevents loss of the bus voltage in case the battery charger gets an internal fault, which may clear after some time. Those diodes are usually implemented in defense meteorological satellites.

The solar array drive (SAD) continuously orients the solar array to face the sun for generating the maximum possible power during the entire sunlight period of the orbit. Shunt component dissipates power that is unwanted after meeting the load power and the battery charge power requirements. The battery stores energy in an electrochemical form to supply power to the loads during eclipse periods over the entire mission life. The PRU provides an interface between the solar array bus and the battery. Due to the widely voltage variation of battery, the discharge converter in the PRU boosts the battery voltage to the bus voltage during an eclipse and the charge converter bucks the array voltage to the battery voltage during sunlight.

The PDU ensures that all loads, except critical and essential loads, are powered through switches and fuses. The fuses are not to protect the loads as much as to protect the power system from faults in the user equipment. The bus voltage controller consists of the bus voltage sensor, the reference voltage and the error signal amplifier. The amplified error signal output of the bus controller enters the mode controller, which in turn sends command signals needed to regulate the bus voltage within required limits. The mode controller automatically changes the EPS mode in response to the error signal as follows: *shunt* mode which during sunlight dissipates the excess in power. *Charge cut-back* mode controls the battery temperature cutting back the charge rate when battery is approaching to full charge. *Discharge* mode maintains the bus voltage through PRU which automatically increase the duty ratio of the discharge converter as the battery voltage decays. And in *PRU bypass* mode, the battery is instantly connected to the bus by the bypass diode quad d(4), which quickly delivers the battery energy to the fuse in case of fault, and blocks power flow to the battery at all other times.

The battery bus is essentially a tap point directly from battery, regarding that during launch and ascent phases the PV array is not deployed, and the battery meets all the energy needs. The power ground cord preserves the battery power during prelaunch testing and final checks before lift-off. Finally, the battery telemetry consists of the battery voltage, current, temperature, individual cell voltages and the internal pressures of selected cells.

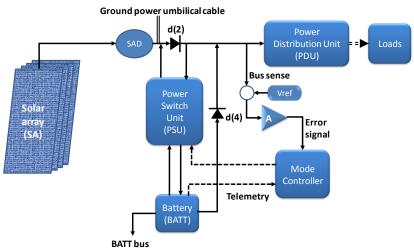

On the other hand, figure 11 shows the sun regulated bus DET architecture. The aim of this architecture is to minimize complexity distributing power from sources like solar array and battery, directly to the load. Although, this DET bus is sometimes misinterpreted as unregulated bus, the bus voltage is regulated by shunt control during sunlight, and is unregulated only during an eclipse. For this reason, this sort of bus is also known as the partially regulated bus, sunlight regulated bus, or sun-regulated bus.

Figure 11. SRB direct energy transfer architecture.

The sun-regulated bus has the usual battery charge regulator to regulate the battery charge rate during sunlight as commanded, but does not have the battery discharge converter. Instead, the battery discharges directly to the bus during eclipse through diode 'd4', called battery discharge diode. It only allows discharge from the battery, but blocks any uncontrolled charge current coming directly to the battery, leaving the charging function to the charge regulator. Thus, the battery is disconnected from the bus during sunlight when the shunt controller is regulating the bus voltage. Therefore, the voltage regulation during sunlight is achieved by shunt control circuits. However, since the battery is directly connected to the bus without a discharge converter in between, the bus voltage is the same as the battery voltage. Therefore, the bus voltage falls as the battery discharges during eclipse, and rises as it gets recharged during sunlight. This architecture would be most beneficial in multiple battery systems in GEO where the sunlight duration is long and the eclipse is short [3].

Finally, the figure 12 shows the unregulated bus DET architecture. The last, basically connects the batteries directly to the solar cells through power switch unit, and provides the lowest level of bus regulation. The bus voltage will vary with varying solar conditions and battery state-of-charge. The main challenge with this topology is matching the battery voltage to the solar panel voltage such that the panel's operating point is close to its maximum power point. As the battery voltage varies, the operating point will move away, giving reduced solar panel efficiency [15].

Figure 12. URB direct energy transfer architecture.

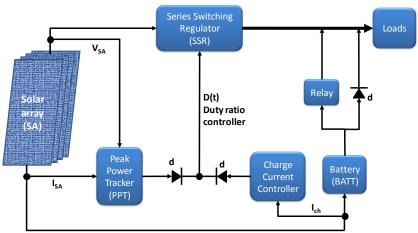

#### I.4.2 Peak Power Transfer (PPT) architecture

Here, the solar array output voltage is always set at the value which results in the maximum power transfer from the array to the load. A series power converter between the array and the load matches the load voltage requirement and the array output voltage. For this architecture to be cost effective, the power loss in the

PPT converter must be less than the gain in operating the system at the peak power point all the time [3]. Figure 13 shows the PPT architecture for a mission with wide variations in solar flux and temperature.

Figure 13. PPT architecture in a mission with wide variations in solar flux and temperature.

In this architecture, a switching regulator between the solar array and the load remedies the main disparity between the voltage produced at maximum power and the constant load voltage. The series regulator input voltage is then maintained at the maximum power producing level by the PPT block, and the output voltage is stepped down to a constant load voltage by varying the duty ratio as required. The PPT is activated only when the battery needs charging or the load demand exceeds the solar array output. Otherwise, the excess power is left on the array raising the array temperature. The battery relay is opened up when the battery is fully charged.

The PPT architecture is particularly useful in applications where the additional weight, power loss, and cost of adding such an assembly can be justified, as happens in small satellites where solar array is not always oriented towards the sun. Furthermore, in satellites having solar radiation and array temperature varying over a wide range is also applied [3]. The last definitively implies a variation in array voltage.

The main advantages of the PPT are that it maximizes the solar array output power all the time, and it does not require the shunt regulator and the battery charge regulator. On the other hand, it results in poor system efficiency due to power loss in the PPT converter. Moreover, since these losses are dissipated inside the spacecraft body, it negatively impacts the thermal system.

Once studied the different alternatives on EPS architectures in different sort of space missions. The research will focus on the low-voltage levels distribution unit, as a part of secondary power distribution system of photo-voltaic EPS spacecraft in order to provide power to the network users through one or several busses, and quarantees the reliable working of the system.

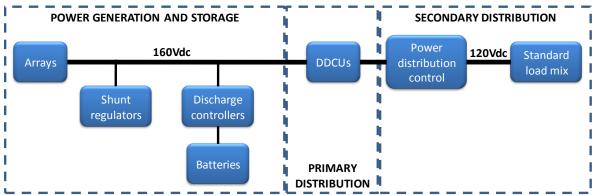

#### I.4.3 Secondary power distribution

At the beginning of 1988 the experience in designing dc EPS for spacecraft was limited to the heritage got from relatively low power of less than a kW to several kW. As some examples, most American spacecraft have used the NASA standard 28Vdc bus. Both regulated and unregulated 28Vdc designs have been flown. The specification for unregulated dc buses permit voltages as high as 42Vdc. European have used a 50Vdc regulated bus in several spacecraft including the European telecommunication satellite series with an 800W and Olympus with a 4kW capacity [17]. On the other hand, General Electric with Radio Corporation of America has built the satellite television corporation which is a direct broadcast satellite spacecraft with a 2kW capacity and a 100Vdc bus [18].

Until now, most spacecraft have used 28Vdc and 50Vdc distribution buses. However, as spacecraft size and power increased, it is inevitable that distribution voltages would increase because of mass considerations. Therefore, as the spacecraft power and bus lengths increase, higher bus voltages could be used to reduce cable mass, to improve power conditioner efficiency, and to reduce EMI [19].

The voltage selection is based upon constraints imposed by space environments and the availability of components. For example, under space vacuum conditions, electrical discharge (corona) can cause shorting between conductors and subsystems at voltage levels above 280Vdc [20]. In LEO, often power loss occurs because of plasma acting as shunting resistor across the PV arrays. This power loss increases with voltage, and becomes noticeable for PV arrays, above 160Vdc [19]. All these factors generate voltage stress in certain critical parts that are voltage-limited as tantalum capacitors, semi-conductors, and power devices. Although, actually designs parts and design methods have been improved and overcome the voltage limitations, it is highly recommendable to stay bellow 160Vdc for a selected bus voltage [21].

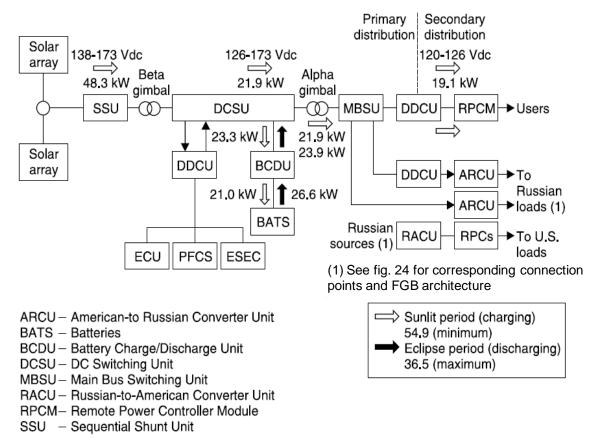

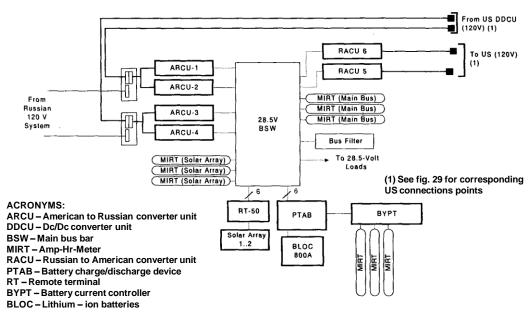

As example of above mentioned, figure 14 shows a simplified block diagram of ISS EPS [22]. All blocks involved, already described in previous sections, provide a primary distribution regulated 160Vdc bus. Voltage conversion is accomplished by dc-dc converter units (DDCUs) which feed a secondary distribution voltage of 120Vdc and provide isolation.

Figure 14. Baseline of EPS on ISS.

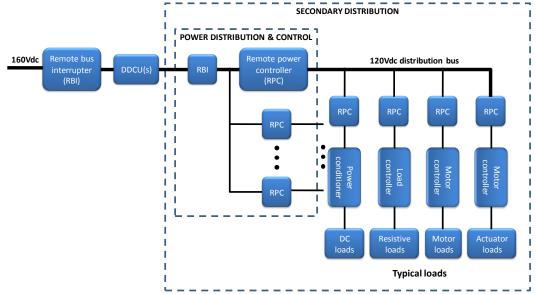

Figure 15, shows a simplified block diagram of a typical secondary power distribution system [24]. This figure illustrates all of the essential elements of the secondary distribution power supplied to typical loads.

Figure 15. Typical secondary power distribution system.

On the other hand, the typically bus voltage levels for secondary power distribution section are: 28V (up to 2.5kW), 50V (up to 8kW), 100V and 125V (above 8kW). It is recommended that bus voltages should not be selected below 20Vdc and not exceeds 125Vdc. Bus voltage below 20Vdc might lead unwieldy current densities, while bus voltage above 125Vdc might easily generate dangerous potential gradients leading to ionization of air molecules (plasma) causing coronal and electric arc discharges, in particular during tests in partially pressurized environments. Furthermore, is necessary to consider that the biggest selection of components-of-the-shelf (COTS) is compatible for operating voltages between 24 and 50 Vdc [2].

The secondary power distribution system often results quite complex because of large number of different type of loads, as well as the control in their interactions. Topics as fault tolerance, safety, and high reliability are no less important.

The typical loads in a spacecraft are varied and usually are depending on space mission target, but generally those are comprised by small motors, pumps, induction heaters, battery circuitry, transmitters and semiconductors electronic devices proper to sort of mission. Typically, the dc voltage levels supplied for this sorts of loads are in the range of 5Vdc to 3.3Vdc (even less) for logic circuits, ±15Vdc and ±12Vdc for control electronics, and 28Vdc for instruments based on motors and actuators.

In the next section, of this research, is described the state of the art of the low-voltage level generation in secondary power distribution section: low-voltage power supply.

## I.4.3.a Low-voltage power supply (LVPS)

As semiconductor technology increase in functional densities and processing speeds of electronic system, is mandatory to minimize power consumption. Therefore, to allow higher processing speeds reducing power consumption, supply voltages had been reduced in new logic families. With the simultaneous increase in power demand and decrease in supply voltage level, new challenges arise for the power system.

According to international technology roadmap for semiconductors every 18 to 24 months integration scale of transistor in ICs is doubled, as well as clock frequency [25]. As a result, higher performances ICs like microprocessor units, memories, and application specific integrated circuits (ASICs) are produced to benefit a wide range of ground level applications which basically are implemented in sectors as telecom, computer, industrial, and military systems. However, regardless application field, these ICs in a circuit board requires several regulated supply voltages to function properly. Furthermore, the ICs digital cores may run at lower voltage while their input/output and analog sections operate with a higher supply voltage. Consequently, on-board LVPS systems must provide features as:

- Very low output voltage levels (≤1V).

- High output currents (≥10A).

- Efficient thermal management.

- Multiple outputs regulation.

- High power density and efficiency.

- Low-profile (mass and dimensions) and costs.

Unfortunately, the on-board power supplies not always meet these features because of several constraints, some of those, related to PCB area, conductions losses and degraded voltage regulation at point-of-load (POL).

Therefore, the current stage of LVPD architectures, as well as system integration, have been developed and improved on industrial, telecom and computer systems. In next paragraphs, the most important architectures on these fields are explained and considered, in order to find and optimal and innovative solution for low-voltage power distribution on a scientific space mission.

The figure 16 shows a block diagram of centralized power system. In a centralized power architecture all power is performed in one bulky power supply which provides the final voltage(s) required at the POL(s) [26]. In other words, this power distribution architecture converts the bus line voltage to the number of DC voltages needed in the system to the appropriate load.

Figure 16. Centralized LVPD architecture.

The strategy above is very cost effective. It doesn't consume precious board real estate at the point of load with the power conversion function. It's relatively simple to manage thermal behavior and EMI. It is fairly efficient because it avoids serial power transformations. This architecture, in general, works well when the power requirements, once defined, are not likely to change and space is not an issue. However, the most obvious problem is how to distribute hundreds of amps common with low output voltages. Furthermore, in this power distribution strategy the power supply must be sized to handle system of maximum configuration, which could put the small configurations (many low-voltages) at a cost disadvantage [27].

On the other hand, the remoteness of the supply from the load, which could be consider as another drawback, can negatively impact the ability of the supply to react to a rapidly changing load (i.e., transient response). Also thermal management, although relatively simple, could become in a special challenge owing the excess heat generated which could concentrate hundreds of watts in a centralize area. The last implies large heat-sinks and fans structures implemented to keep-out the power supply from becoming overheated. Finally, these system hotspots are a source of reduced system reliability [27].

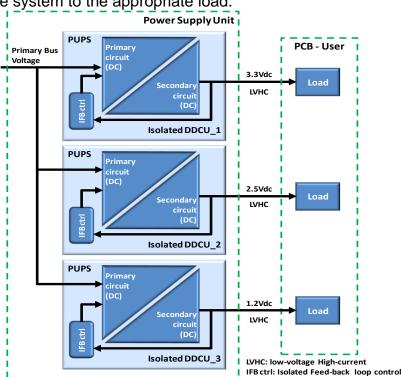

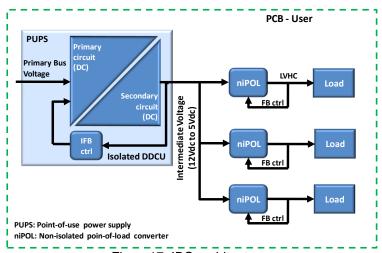

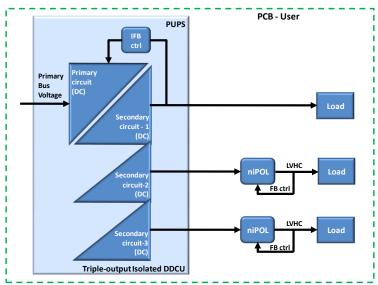

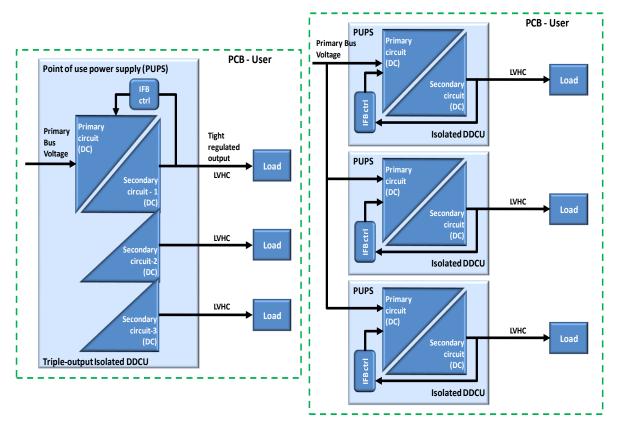

To solve some addressed shortcomings of centralized power architecture, figures from 17 to 20 show the conventional distributed point-of-use power supply architectures [XIX-XXI], which are decentralized power distribution architectures consisting, in the simplest form, of a DDCU serving post regulators, non-isolated Point-of-Load (niPOL) converters, or a mix suited on-board users. The DDCU might provide intermediate DC voltage with certain level of regulation, isolation, noise suppression, and power factor correction. Therefore, this intermediate voltage is converted by post regulators located at the point of the load they serve. The last improves dynamic response, a better distribution of low voltages as well as heat distribution through the system eliminating the need of heat sinks or high velocity airflow structures. Distributed point-of-use power supply architectures, nevertheless, can be more expensive because isolation, regulation, transformation, EMI filtering and I/O protection are all done at every brick [27].

Figure 17. IBC architecture.

In figures 17 and 18, both intermediate bus converter (IBC) architectures, isolated and non-isolated, are widely used in telecom and computer systems. The DDCU converts the power from the system bus into a relatively lower intermediate voltage, which is normally between 12 to 5 volts [25]. Then the power is distributed at this intermediate voltage and converted the second time by the post-regulators into the required low voltage at the POL. The two-stage dc-dc power conversion for each output gives good regulation at POL, nevertheless reduces the

overall efficiency, and due to additional power components employed, the cost as well as the physical size of the power supply is increased [27].

Figure 18. IBC multiple outputs architecture.

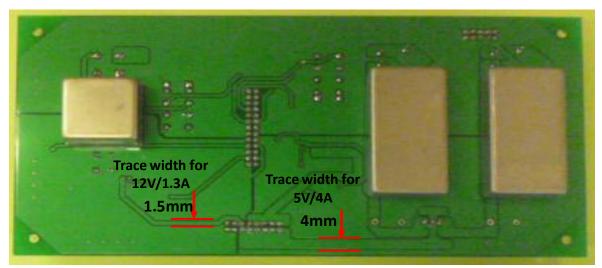

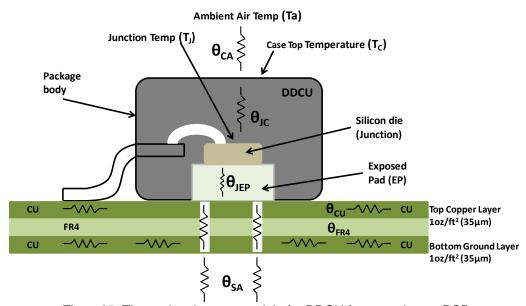

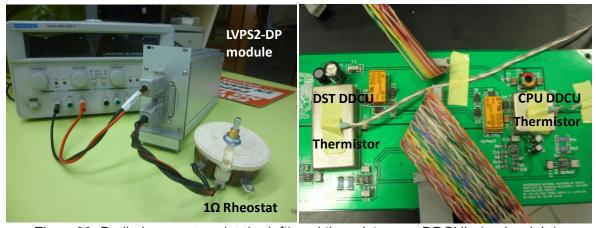

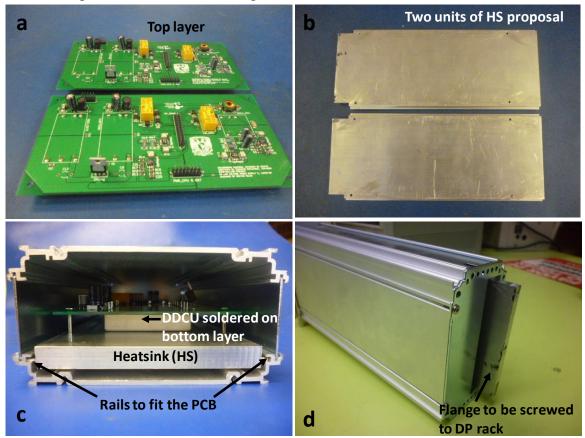

Furthermore, because the intermediate voltage is lower than main bus voltage, the power distribution is done with a relatively higher current over a long distance on the PCB. This will cause a significant conduction loss [25]. The conduction lost  $(P_{loss})$  in a PCB track is determined by equation 4, where  $\rho$  is the copper resistivity, l, w and h is the length, width and thickness of the track, respectively, which is used to distribute an rms current of  $I_{rms}$  [30]. Therefore, in order to minimize losses many layers of PCB must be used to distribute the power; consequently, PCB real estate utilization is greatly reduced for routing the high-speed signals.

$$P_{loss} = \rho \frac{l}{w \times h} I_{rms\_distr}^2 \tag{4}$$

On the other hand, in figure 19 the cross-regulated multi-channel architecture employs fewer power components for multiple outputs than the IBC architectures do. However, it is rarely used in telecom and computer systems, because precise regulation in multiple outputs is not obtainable owing to exacting matching and coupling of the magnetic elements [25]. Furthermore, the internal loop control on DDCU multiple outputs is usually associated to single or positive output making them tightly regulated, nevertheless this put it in total dependence the tight regulation of the other outputs.

Finally, in the figure 20 is shown the multi-module architecture which frequently is put it in practice at industry. Here, several point of use power supplies are used each independently producing a finely-regulated supply voltage.

It is efficient, especially when several low-voltage high-current loads are located at different points on the circuit board. It is because each point of use power supply can be placed close to its load, thus the power can be delivered to these locations at the level of the bus voltage, and it is converted into the required low voltage at the point of load. Therefore, high current only, travels a very short distance reducing conduction losses on the PCB. However, this approach is rather expensive because of the high costs of point of use power supplies, thermal management in critical sections of board, and it takes much of the valuable on-board space [25].

Figure 19. Cross-regulated multichannel architecture.

Figure 20. Multi-module architecture.

Currently, the introduction of new modular and high density power converters did make faster and easily the migration to distribute point of use power supply architectures, and overcame some of the problems of centralized architectures. However, with each new generation of processors, memories, DSPs, FPGAs and ASICs, the trend is toward lower voltages, higher currents, higher speeds and more on-board voltages. Consequently, system designers are challenged to contend with a proliferation of lower voltages; provide ever-faster transient response; improve overall power system efficiency; and do it all using less board area [31]. The last, cause that for some applications distribute point of use power supply solutions required increase the number of power modules affecting subsystem development, in terms of board space and cost.

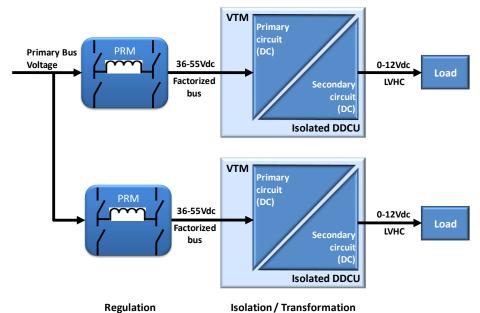

One of the key objectives of factorized power architecture, which is showed in figure 21, is to maximize the competitiveness of a power system by providing the highest degree of system flexibility, power density, conversion efficiency, transient responsiveness, noise performance, and field reliability [31]. All these features are meeting by separating conventional converter functionality in two power building blocks: a *pre-regulator Module* (PRM) and a *voltage transformation module* (VTM). Therefore, the load regulation function is accomplished by a non-isolated converter with high efficiency (97%-99%), the PRM. The later works with an input line range of 36V to 55V, and outputs a *factorized bus* that can range from 0V up to 55V [32]. After that, a voltage transformation stage is enabled by a *voltage transformation module* (VTM), designed to convert the factorized bus to the voltage levels required by loads with efficiencies as high as 97%. Furthermore, VTM provides effective current multiplication and isolation.

Figure 21. Factorized power architecture.

The very important issues of this architecture are that factorized voltage bus is normally maintained above 40V, the last reduce losses and cross-section requirements on the main board. The load voltage can be regulated has a wider range, given the factorized bus range and the availability of various VTM transformer ratios [32]. And, PRMs and VTMs are power components ICs which are enabled to do power conversion in a small (≤ 4 cm³) and light (<15gr) power ball grid array or J-level package, with power densities over 800W/in³ which represent good thermal management.

The combination of factorized power architecture and IC power blocks give the power designer the flexibility to use only what is needed where it is needed [28]. Furthermore, this architecture also take advantage of the state-of-the-art in designing switching mode power supplies (SMPS), by implementing zero-voltage switching and zero-current switching topologies on VTMs to provide wide voltage range input and high efficiency voltage transformation [31]. However, the main inconvenient (at the designing phase of this work) lies that this architecture enables an efficiently power conversion only for process over 200W of power demand [27]. The last issue, is an inconvenient for low power ranges application resulting in high cost architecture.

Once stated the most important aspects in the research about LVPS architectures on industrial, telecom and computer fields; is necessary to put in context the complexity, for distributing low-voltage levels, in a very large and innovative instrument on high energy particle detection within a scientific space mission development. All advances reached, by above architectures, represent potential different possible solutions for distributing low-voltage levels in space environment. However, the constraints in electronic design at this environment make every mission a very particular scenario. Then, power designer has to innovate according to scenario requirements of scientific mission being considered, in order to find an optimal solution for its LVPD system [29]. Therefore, in next chapter will be described the Extreme Universe Space Observatory (EUSO) instrument, onboard Japanese Experiment Module (JEM). This instrument, represent a scientific space mission in fundamental physics research field. Moreover, due to the complexity of the instrument, a large scale comprehensive prototype is mandatory: EUSO-Balloon instrument is such prototype, and also will be described.

# II.1 JEM-EUSO project

In general, space scientific missions are conducted with small, medium and large satellites, as well as space stations. Its targets could be one or more different topics related with Earth's observation, weather study, fundamental research, etc. The latter, typically suits purpose of studying astronomical objects or physical phenomena in the context of cosmology or analyses in relativistic physics [2]. In that way, ultra high energy cosmic rays (UHECR) detection has attracted the attention of a big scientific sector in Physics. The reason is that Cosmic Rays (CR) provides a unique probe of the most energetic processes in the universe. Therefore, in order to innovate in CR detection, a space telescope is proposed and can be extremely large and complex as is the case of JEM-EUSO mission.

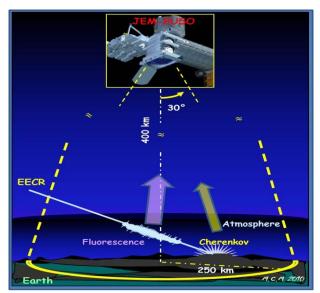

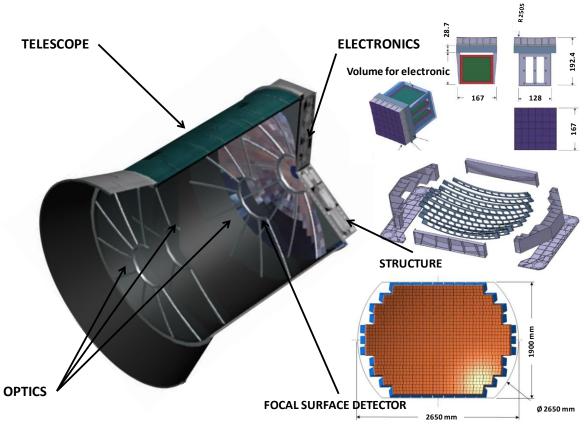

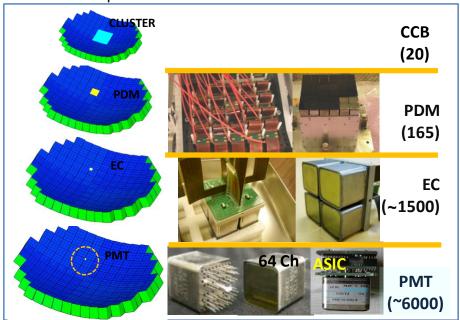

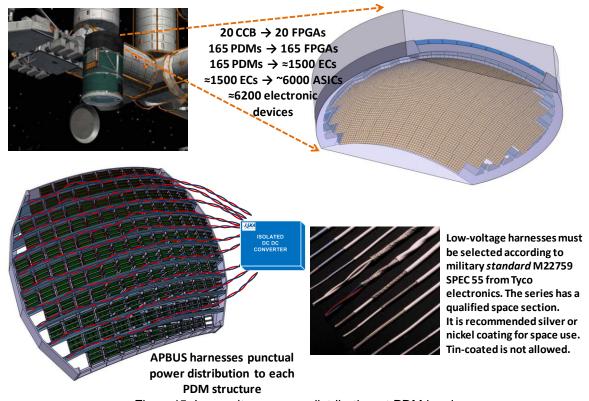

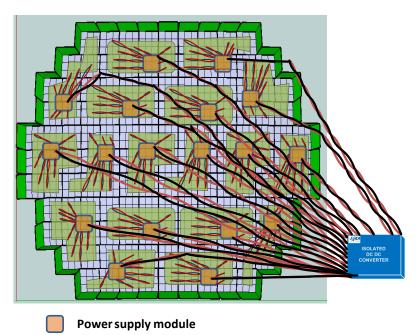

JEM-EUSO is a worldwide collaborating effort of approximately 75 research groups from 13 countries. The instrument consists of a large telescope with a wide field-ofview (±30°), to be mounted on ISS JEM. It is the first space mission to explore the universe at extreme energies through the detection from space of UHECR (≥10^20eV) impinging the Earth's atmosphere. Such interactions produce an extensive air shower (EAS), a huge number of charged particles, mainly electrons and positrons travelling through the atmosphere along the original direction of the incoming UHECR. These particles excite the atmospheric N<sub>2</sub>, which immediately decays by fluorescence producing UV photons with wavelengths between 300 and 400 nm. Furthermore, the electrons and positrons are super-luminal inside the atmosphere producing UV Cherenkov radiation. Both radiations are observed by JEM-EUSO from LEO at 400 km of height. Since electrons and positrons travel all at roughly the same speed, essentially that of light the net effect is that, from the point of view of the telescope, an EAS is observed as a light spot moving at the speed of light, thus defining a track on its focal surface. It is worth to notice that Cherenkov photons are emitted along the propagation direction of the particles in the EAS, i.e., downwards (see figure 22). Therefore, those photons are only observed because of scattering in the atmosphere or after diffuse reflection on the top of optically thick clouds or on the ground. The latter produces a strong Cherenkov mark signaling the impact point of the EAS and it is extremely important for data reconstruction [33].

Figure 22. JEM-EUSO will use the Earth atmosphere as a giant detector of UHECR [34].

In a beginning, EUSO was originally selected by ESA as a mission attached to the European Columbus Module of the ISS. Then, Phase-A study has been successfully completed in June 2004 under ESA. However, ESA postponed the start of phase-B, so Japanese and U.S. teams redefined EUSO as a mission attached to exposure facility on JEM (JEM/EF) of ISS. Therefore, the mission was

renamed as JEM-EUSO and continue with extensive simulations, design, and prototype hardware developments that significantly improved mission profile, targeting the launch in 2017 by H2B rocket and conveyed by the HTV (H-II Transfer vehicle) to ISS [35].

JEM-EUSO instrument is designed to operate for more than 3 years on board the ISS. Then, in next section it will be given a brief background of ISS as well as its EPS. Also, are described the subsystems that comprise this complex instrument, plus the conditions and constraints to be consider during work's development.

### **II.2 International Space Station**

As mentioned above, the most standard space missions are based on satellites due to the fact that reach the stage of being economically viable. As examples, we have several satellites for communications, weather and navigation purposes, as well as those for monitoring Earth's resources, health of its crops and pollution. However, there are some special missions that requires more complex and biggest structure for serving to scientific community on issues related to Earth's environment, solar system and universe [1]. The International Space Station represents a very good example.

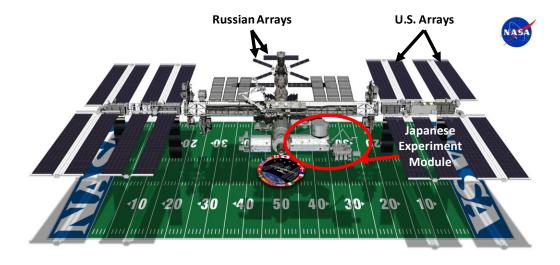

The ISS, as showed in figure 23, is truly the largest and most complex structure ever built wider than the length of a football field, with sixteen international partners. The complete assembly weighs 450 tons and the total interior space comprises six laboratories equal to two Boeing 747 aircraft. The ISS is located at an altitude range of 335 to 500 km, in LEO, with a 90 min orbit period and 35 min of eclipse [3]. The experiments planned for its on-board laboratories are targeted to enhance our understanding in Earth's observation, exposure of micro-gravity on humans and producing new medicines and materials.

Figure 23. International Space Station [36].

# II.2.1 Utilization: JEM/Kibo-Exposure Facility

As can be seen in figure 23, ISS utilization could be subdivided in different modules from different countries. For this work, JEM is targeted. Experiments in JEM/Kibo focus on space medicine, biology, Earth observations, material production, biotechnology, and communications research [37]. *Kibo* (translated as hope) experiments and systems are operated from the Mission Control Room in the Space Station Operations Facility at the Tsukuba Space Center in Ibaraki Prefecture, Japan, just north of Tokyo. The Earth observation payloads are accommodated in the external JEM/Kibo-EF.

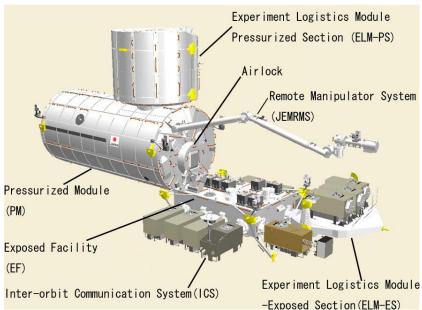

The JEM-EF is an external platform for conducting scientific observations, Earth observations, and experiments in an environment exposed to space. The JEM-EF/payload interface on the JEM-EF side is the Exposed Facility Unit (EFU). There are a total of 12 EFUs on the JEM-EF, nine of which are available for users. The other three EFUs are used for the JEM-experiment logistics module-exposed section (ELM-ES) and for temporary storage. Figure 24, is a general view of the JEM/Kibo facility; meanwhile figure 25, is a block diagram of the EFU locations on the JEM-EF. In general, the JEM-EF services its EFU payloads with electrical power, data, and active thermal control [37].

Figure 24. General view of JEM/Kibo-EF [38].

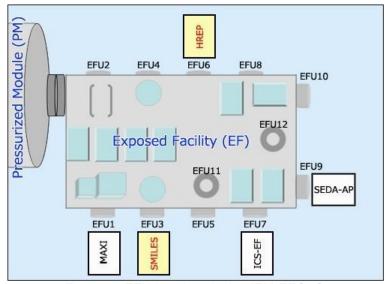

As stated above, nine EFUs are available for users. Figure 25, shows the experimental payloads already mounted on these EFUs: MAXI (monitor of all sky X-ray image), SMILES (superconducting sub-millimeter-wave limb-emission sounder), ICS (inter-orbit communication system), SEDA (space environment data acquisition equipment), and HREP (HICO-RAIDS experiment payload).

Figure 25. EFU locations in the JEM-EF [37].

On the other hand, each EFU has a built-in attached payload BUS (APBUS) unit. The APBUS was developed to service the *Kibo*-EF payloads. Each experiment/payload is mounted onto the *Kibo* Exposed Pallet, grasped by the *Kibo* remote manipulator system, transported to the predetermined position, and then installed at the predetermined port of the *Kibo* EF.

The various handling logistic task-launch, on-board transportation, and installation require the payloads to be equipped with special attachment: the payload attach mechanism-payload unit (PAM-PU), the grapple fixture, and/or payload interface unit (PIU). All attachments are subject to accurate alignment/interface requirements for installation. Therefore, JAXA developed a mission interface structure to satisfy all interface requirements for the payloads to be handled. This resulted in two types of support structures: box structure (BStr) and pallet structure (PStr) showed both in the figure 26 bellow.

Figure 26. Mission interface support structure: BStr (left) and PStr (right) [37].

The subsystems needed for APBUS BStr or PStr service provision are: the heater control equipment (HCE), the attached payload remote terminal (APRT), the power distribution box for attached payload (PDAP), and the extension mechanism assembly (EMA).

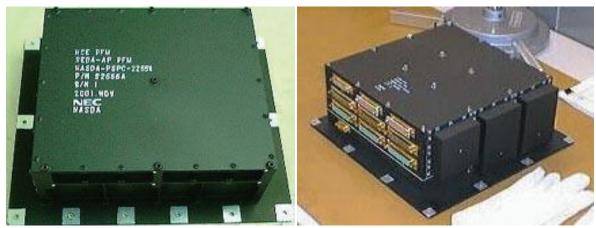

Figure 27, shows HCE at left and APRT at right. HCE detects experiment equipment temperature and keeps experiment equipment warm by providing electrical power to the heater in case the sensor detects a determined temperature [39]. HCE has a mass of 2 kg, power: 330mA (supply current), and a controllable temperature range of -44°C to 1°C. On the other hand, APRT converts signals of experiment equipment to the *Kibo* specific communication protocol (MIL-STD-1553B) to perform experiments on *Kibo* [39]. APRT has a mass of 6 kg.

Figure 27. HCE at left, and APRT at right [39].

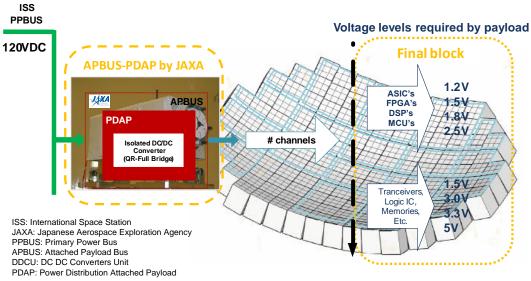

Considering the EPS of ISS which distributes a 120V electrical power supply line, through the *Kibo*-EF, experiment equipment must satisfy specific interface conditions (e.g. load characteristics) to connect to the *Kibo*-EF. PDAP can meet above conditions and transform electrical power to 28 V that is easy for experiment equipment to use [39]. Besides, PDAP can distribute electrical power to multiple lines (12 channels max). PDAP has a mass of 7 kg.

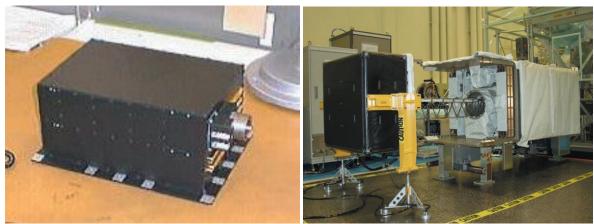

On the other hand, some *Kibo*-EF experiments need an extension from the main structure. EMA was developed for this purpose. EMA can extend up to 1 m with the experiment equipment on the tip of an extendable mast [39]. Also, EMA can stow the extendable mast within the mission structure as required. For that purpose, EMA is equipped with LLM (Launch Lock Mechanism) to positively fix the extendable mast during launch and landing (Shuttle requirement), and to release the extendable mast to perform experiments on the *Kibo*-EF [39]. Figure 28 shows PDAP at left and EMA to the right.

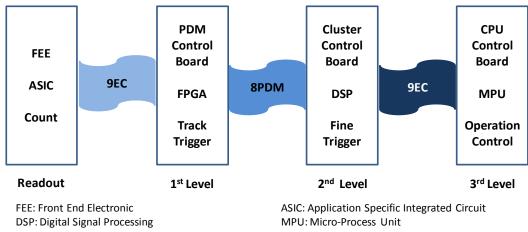

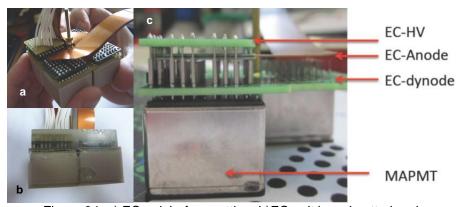

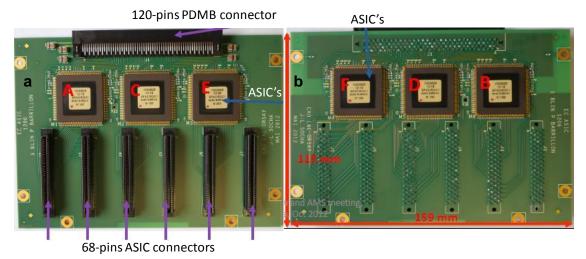

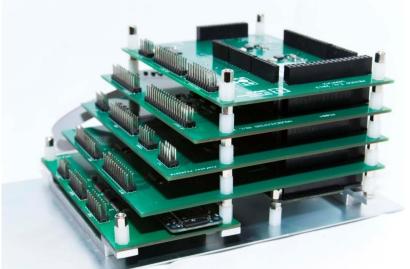

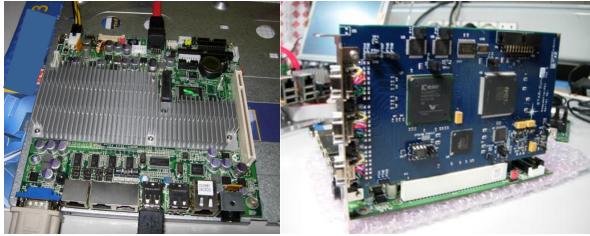

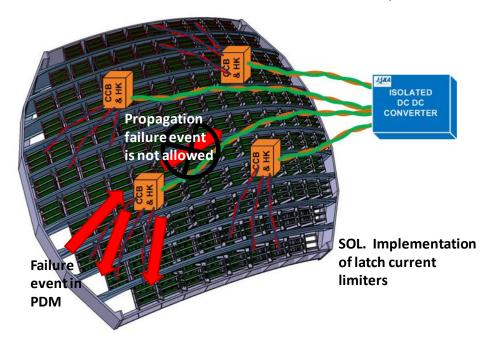

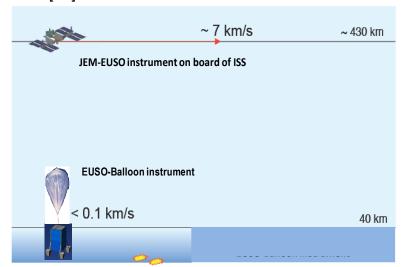

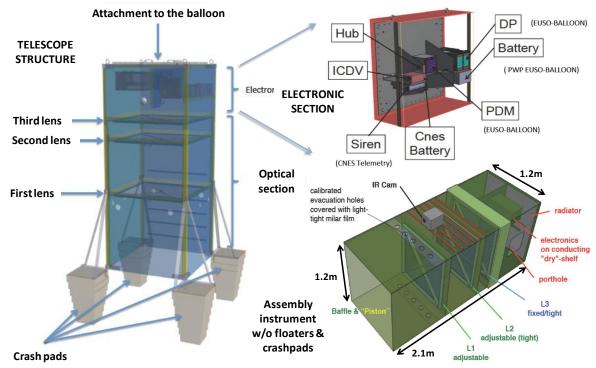

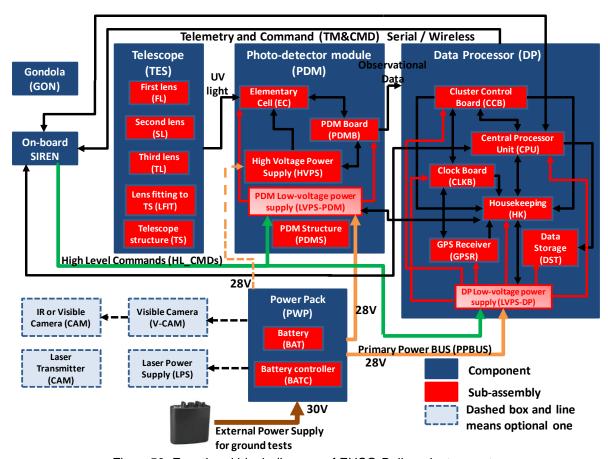

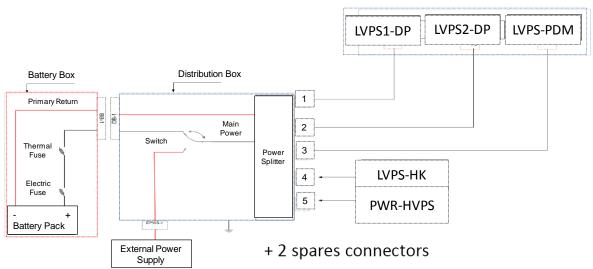

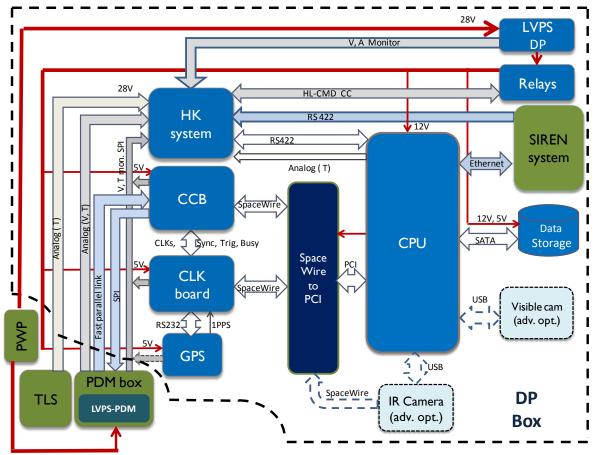

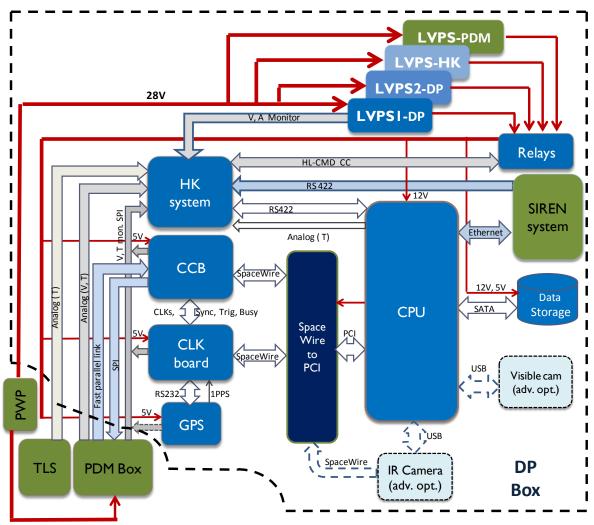

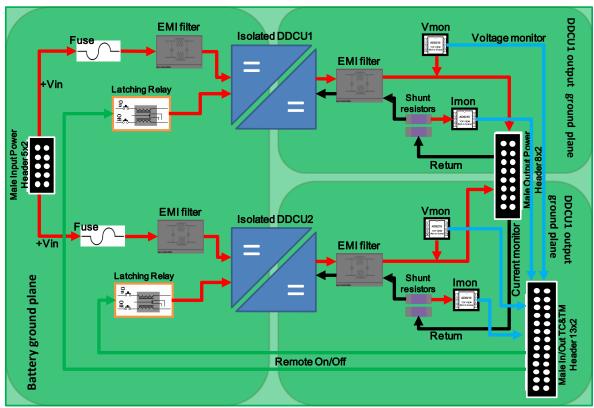

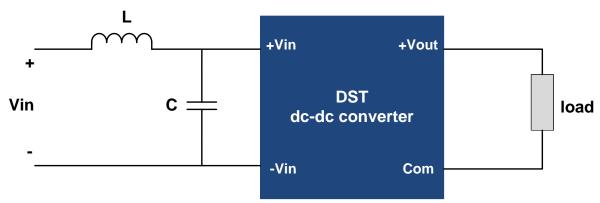

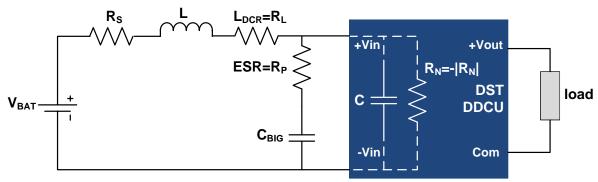

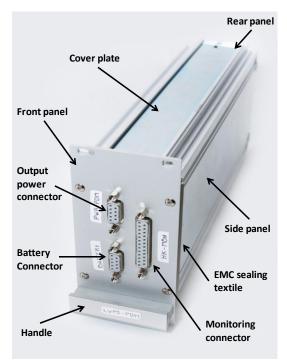

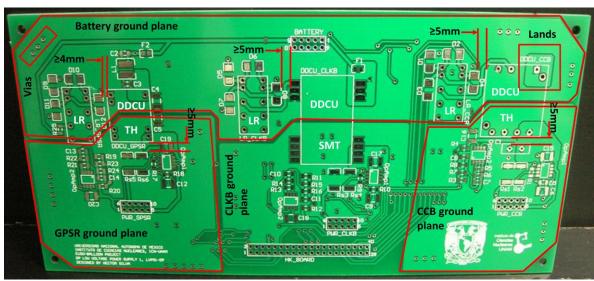

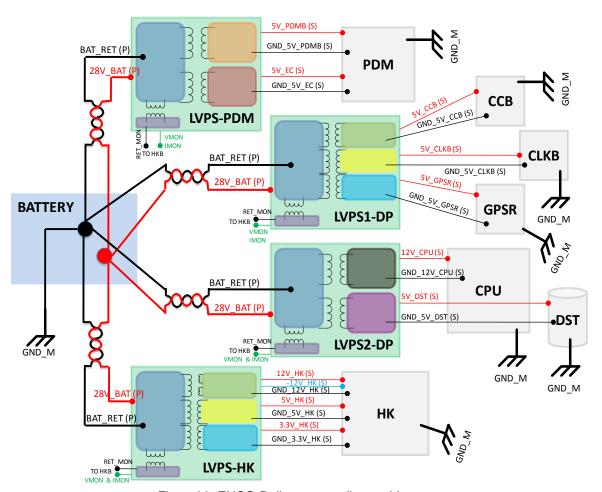

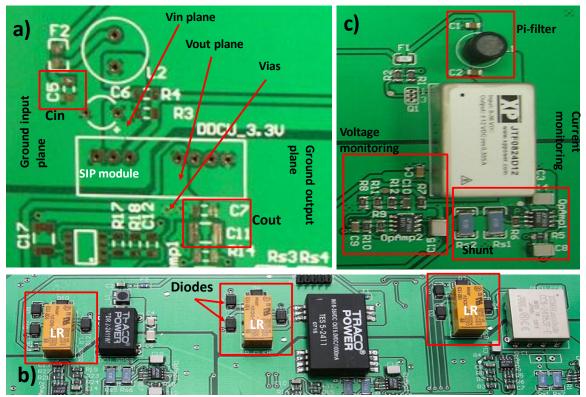

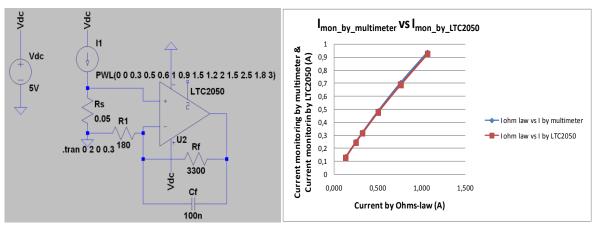

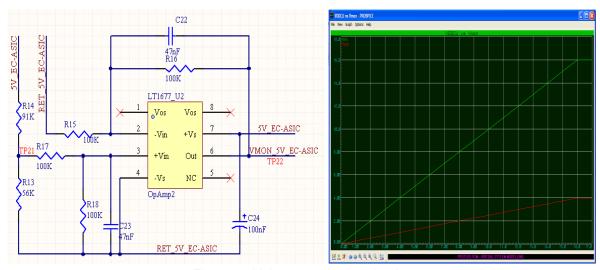

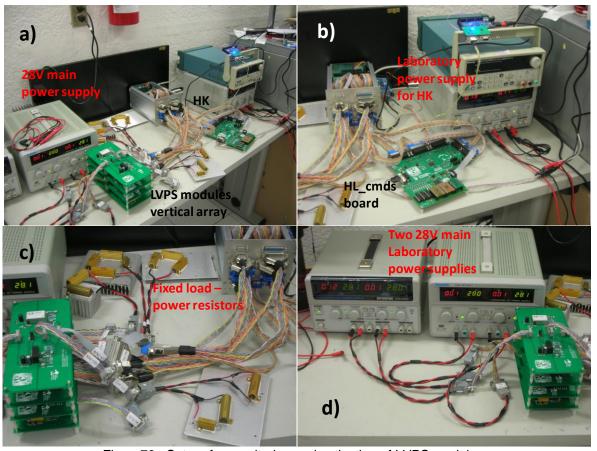

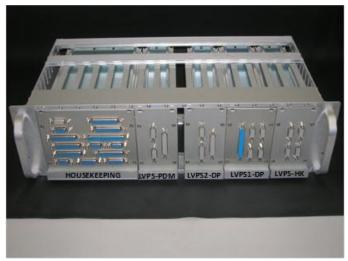

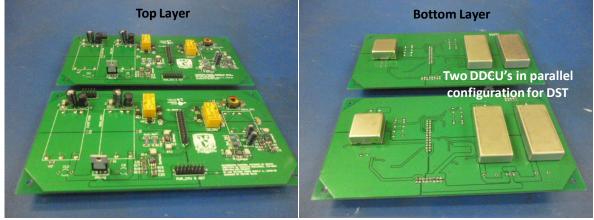

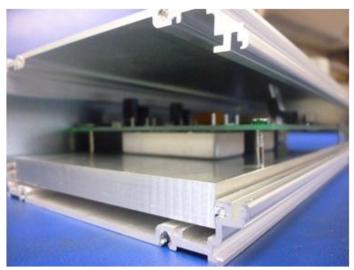

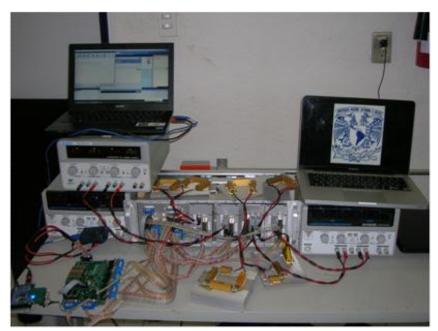

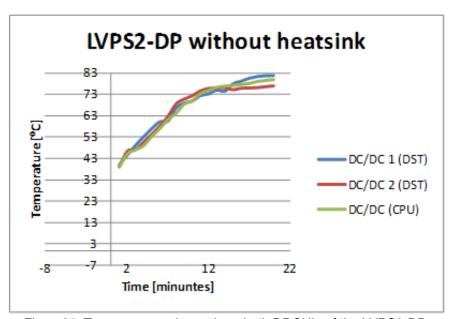

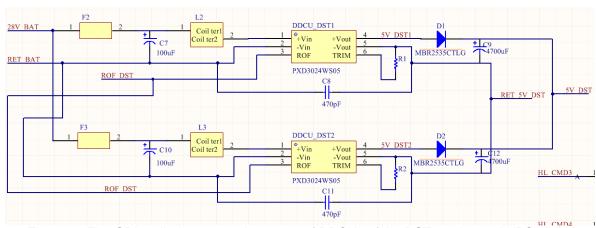

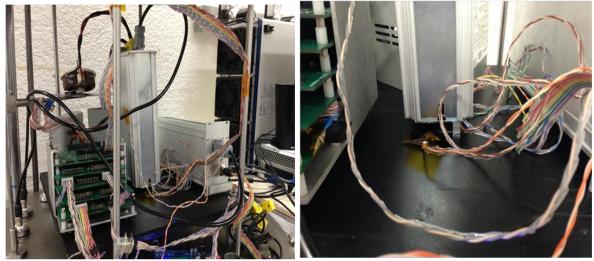

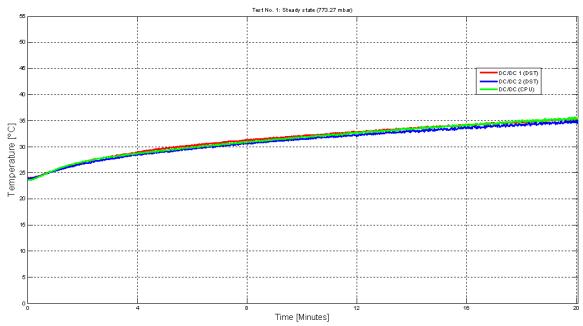

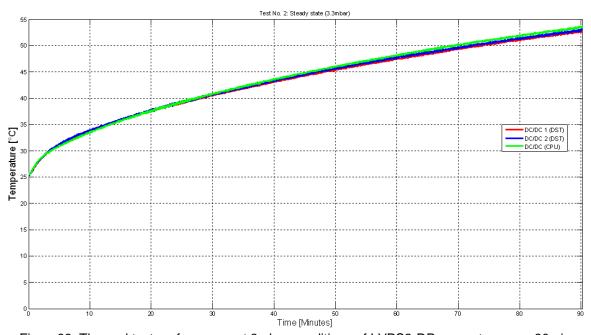

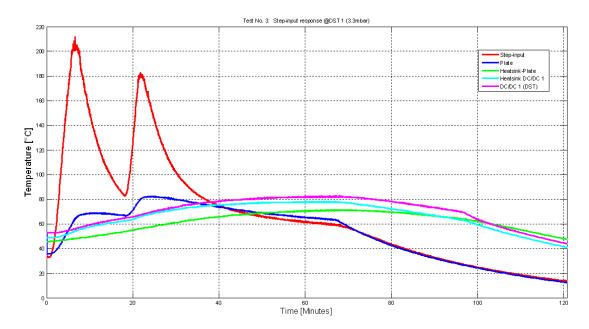

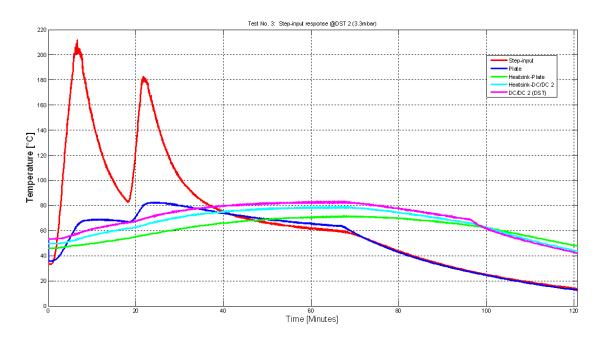

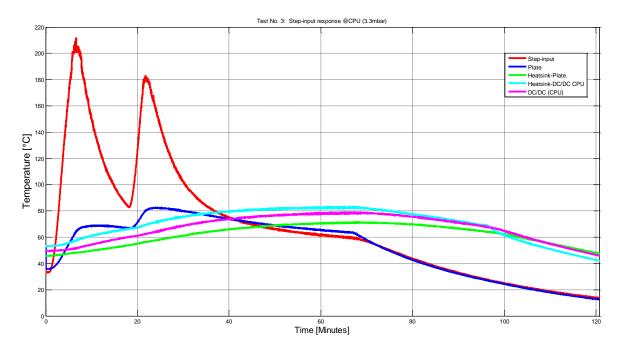

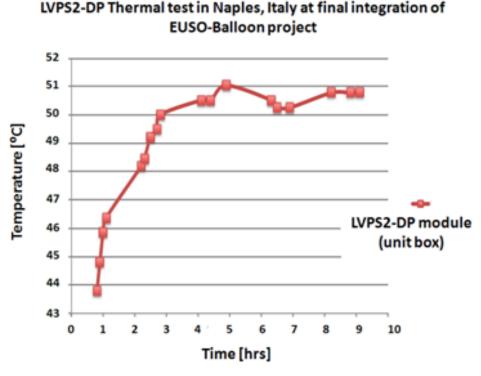

Figure 28. DPA at left, and EMA at right [39].