# DIRECTORIO DE PROFESORES DEL CURSO: DISPOSITIVOS Y CIRCUITOS ELECTRONICOS 1984.

1. M. EN I. HUGO CALLEJA GJUMLICH INVESTIGADOR

SECCION DE ELECTRONICA

DEPFI

UNAM

550 52 15 Ext. 4477

2. M. EN I. ROBERTO DAZA GOMEZ TORRES

PROFESOR DEPFI

UNAM

MEXICO, D.F.

550 52 15 Ext. 4477

ING. ROBERTO MACIAS PEREZ (COORDINADOR).

COORDINADOR DEL AREA DE INGENIERIA EN ELECTRONICA

DIVISION DE INGENIERIA MECANICA Y ELECTRICA

FACULTAD DE INGENIERIA

UNAM

MEXICO, D.F.

550 52 15 EXT. 3755

ING. JORGE EUGENIO LAVIN MARTINEZ

PROFESOR

DIVISION DE INGENIERIA MECANICA Y ELECTRICA

FACULTAD DE INGENIERIA

UNAM

MEXICO, D.F.

550 52 15 EXT. 3755

M EN C. ANASTASIO MONTIEL MAYORGA

SUBDIRECTOR DE OPERACION

DIRECCION GENERAL DE DESARROLLO TECNOLOGICO

S. C. T.

XOLA Y AV. UNIVERSIDAD

MEXICO, D.F.

ING. EDUARDO RAMIREZ SANCHEZ

PROFESOR

COORDINADOR DEL LABORATORIO DE ELECTRONICA

DIVISION DE INGENIERIA MECANICA Y ELECTRICA

FACULTAD DE INGENIERIA

UNAM

DEPTO. DE COMUNICACIONES Y ELECTRONICA

MEXICO, D.F.

550 52 15 EXT. 3761

00 kg gag: .

... H (4)

# ELECTRONICA: DISI ATIVOS Y CIRCUITOS

# 10 AL 22 DE SEPTIEMBRE DE 1984

| FECHA               | HORARIO      |    | T E M A S                                                                                                                                                                                                                          | PROFESORES                         |

|---------------------|--------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 10 de septiembre    | 17 a 21 Hrs. | 1. | INTRODUCCION<br>Señal: Analógica y Digital.<br>Términos de uso común.<br>Sistemas analógicos, digitales<br>e híbridos.                                                                                                             | M. en C. Anastasio Montiel Mayorga |

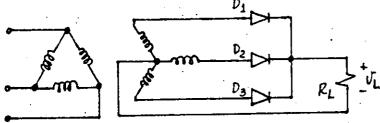

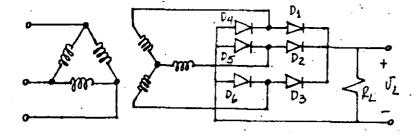

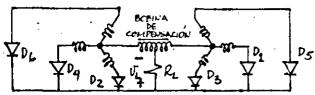

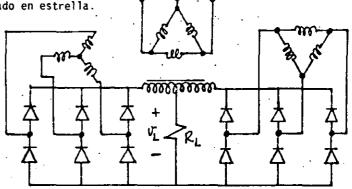

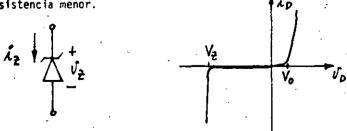

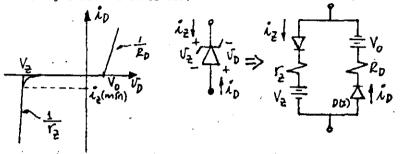

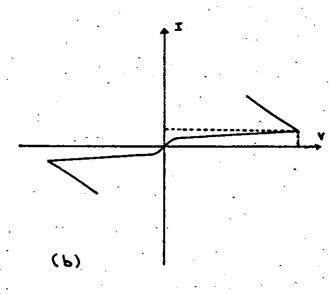

| 11 de septiembre    | 17 a 21 Hrs. | 2. | EL DIODO Funcionamiento, características y especificaciones del fabricante.  Modelos. Aplicaciones: Rectificadores monofásicos y polifásicos, recortadores y multiplicadores de voltaje. El diodo Zener como regulador de voltaje. | M. en C. Anastasio Montiel Mayorga |

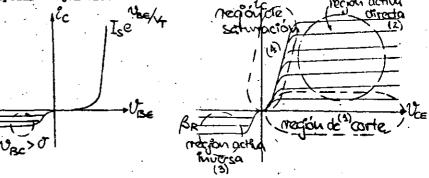

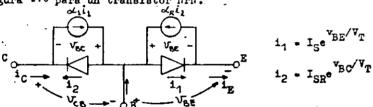

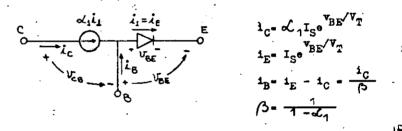

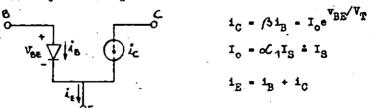

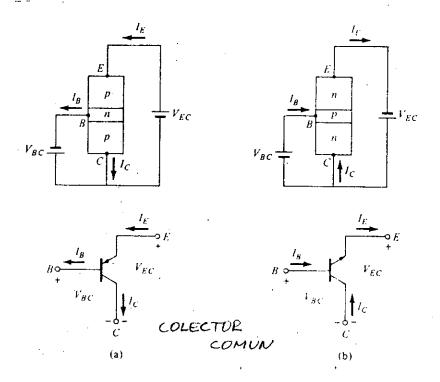

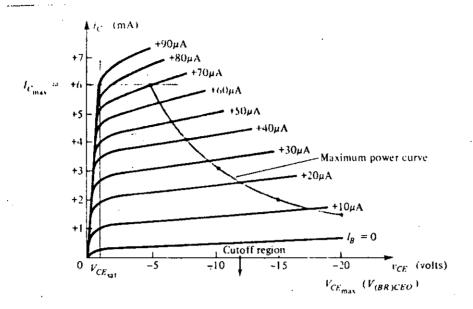

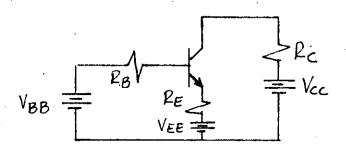

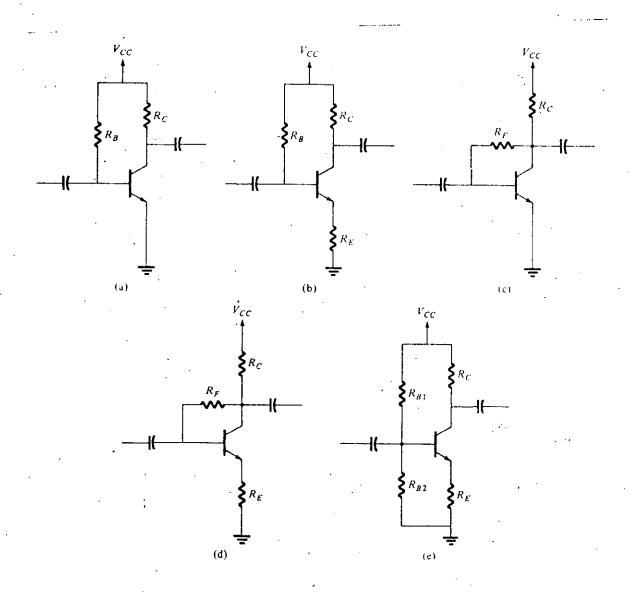

| 12 de septiembre    | 17 a 21 Hrs. | 3. | EL TRANSISTOR Funcionamiento, características y especificaciones. Polarización. Amplificadores de baja y alta po- tencia.                                                                                                          | M. en C. Anastasio Montiel Mayorga |

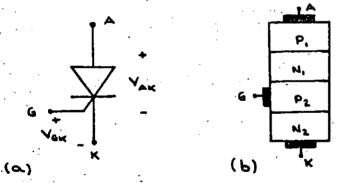

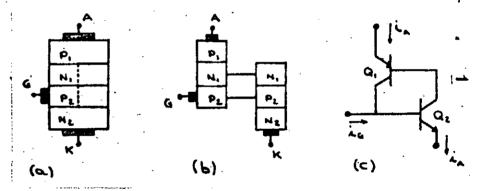

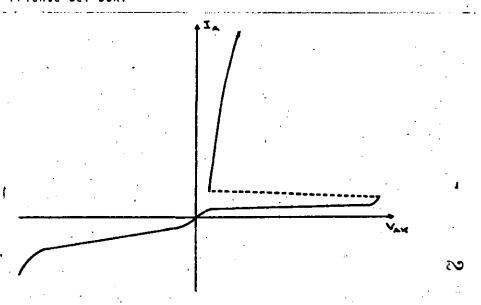

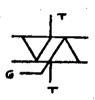

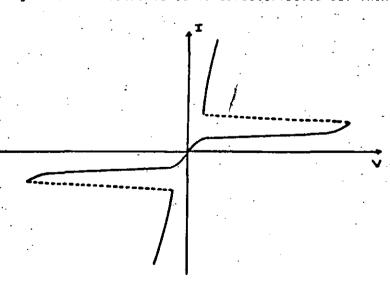

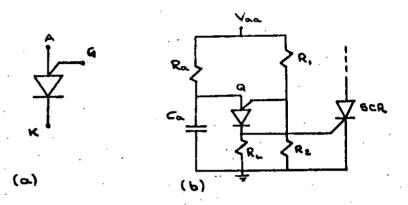

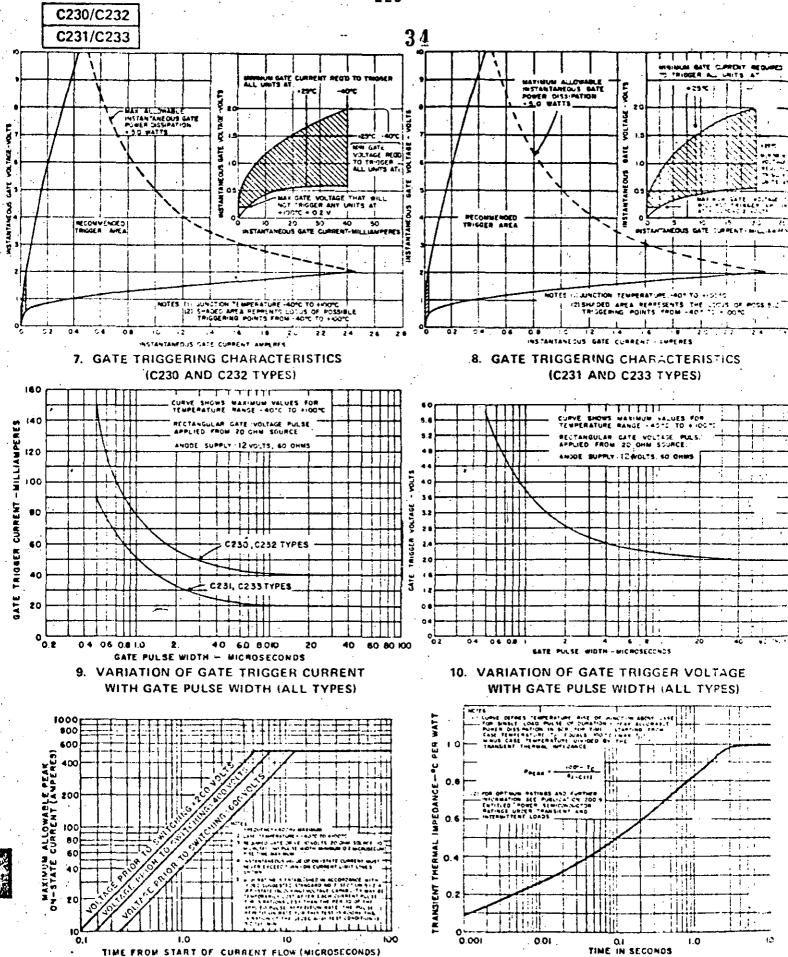

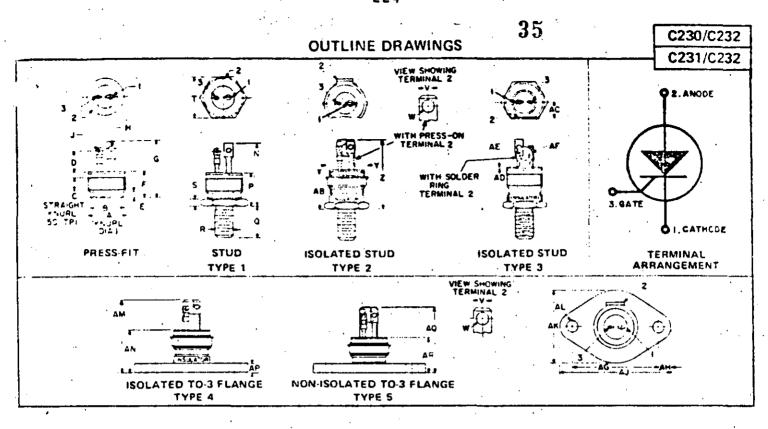

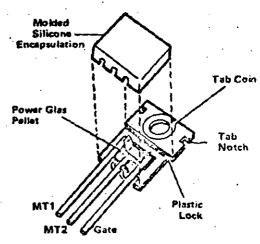

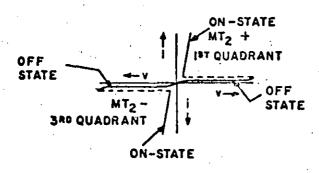

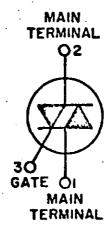

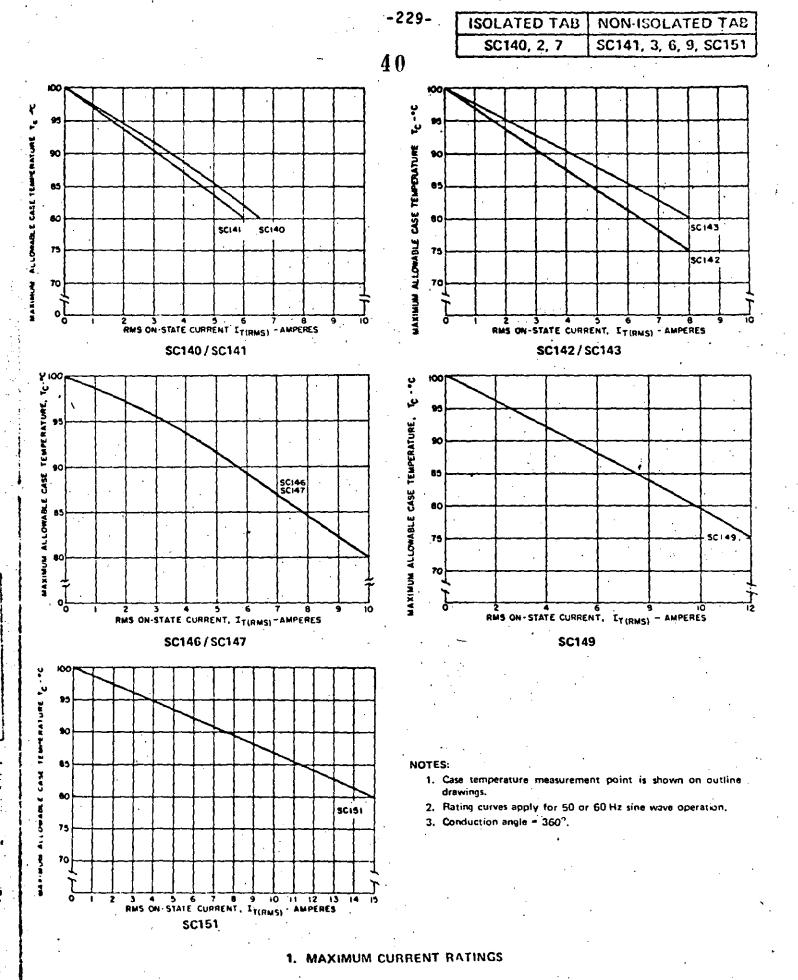

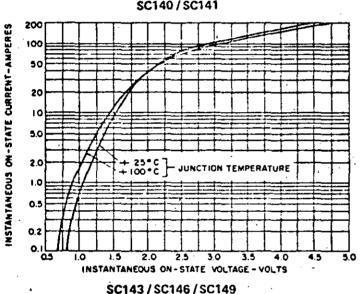

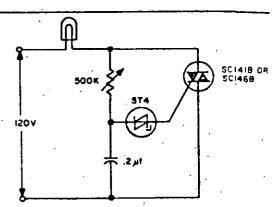

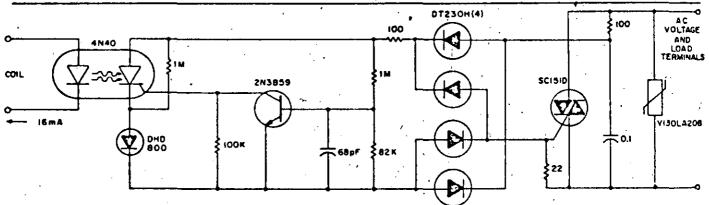

| 13 de septiembre    | 17 a 21 Hrs. | 4. | TIRISTORES Funcionamiento, características y especificaciones. Dispositivos de disparo. Técnicas de apagado. Aplicaciones.                                                                                                         | M. en C. Hugo Calleja Gjumlich     |

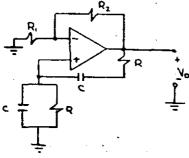

| 14,17 de septiembre | 17 a 21 Hrs. | 5. | EL AMPLIFICADOR OPERACIONAL<br>Características y especificaciones.<br>Modelos.<br>Aplicaciones lineales y no lineales.                                                                                                             | Ing. Roberto Macías Pérez          |

| FECHA               | HORARIO      | •   | T E M A S                                                                                                                |       | PROFESORES                                                |

|---------------------|--------------|-----|--------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------|

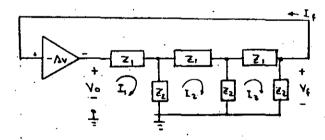

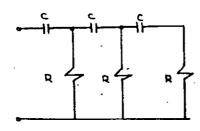

| 18 de septiembre    | 17 a 19 Hrs. | 6.  | GENERADORES DE ONDAS.                                                                                                    |       | Ing. Roberto Macías Pérez                                 |

| 18 de septiembre    | 19 a 21 Hrs. | 7.  | Compuertas. Multiplexores. Deco-                                                                                         | -     | Ing. Eduardo Ramírez Sánchez                              |

| 19,20 de septiembre | 17 a 21 Hrs. |     | dificadores. ROM's y PLA's.<br>Flip-Flop. Contadores. Registros.<br>Memorias.<br>Aplicaciones.                           | · -   |                                                           |

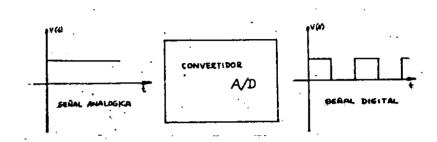

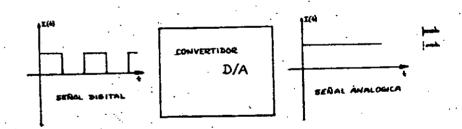

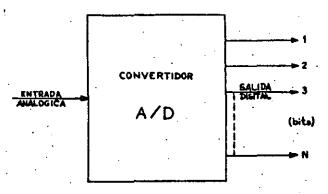

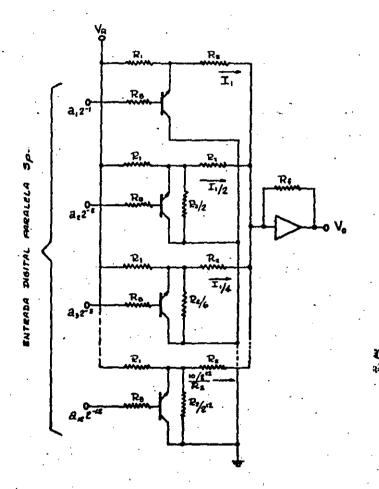

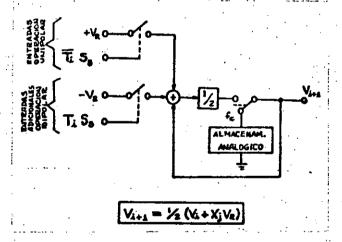

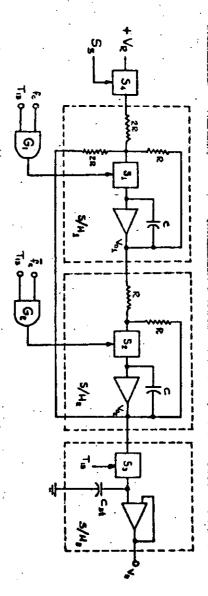

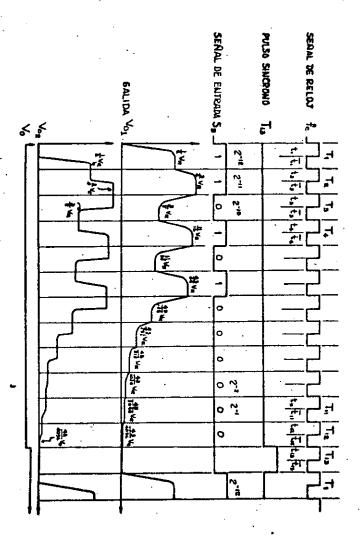

| 21 de septiembre    | 17 a 19 Hrs. | 8.  | CONVERTIDORES A/D Y D/A<br>Cuantización, Velocidad de Mues-                                                              |       | M. en I. Roberto Daza-Gómez Torres                        |

|                     |              |     | treo.<br>Tipos.<br>Aplicaciones.                                                                                         | • .   |                                                           |

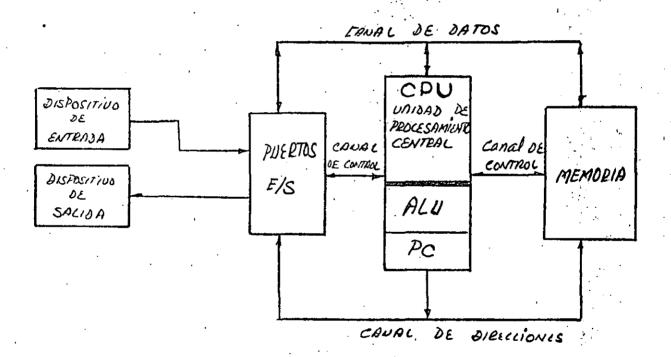

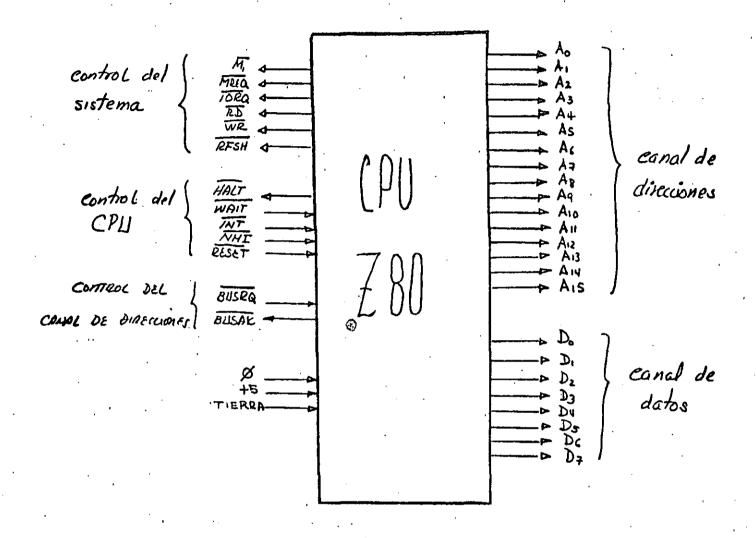

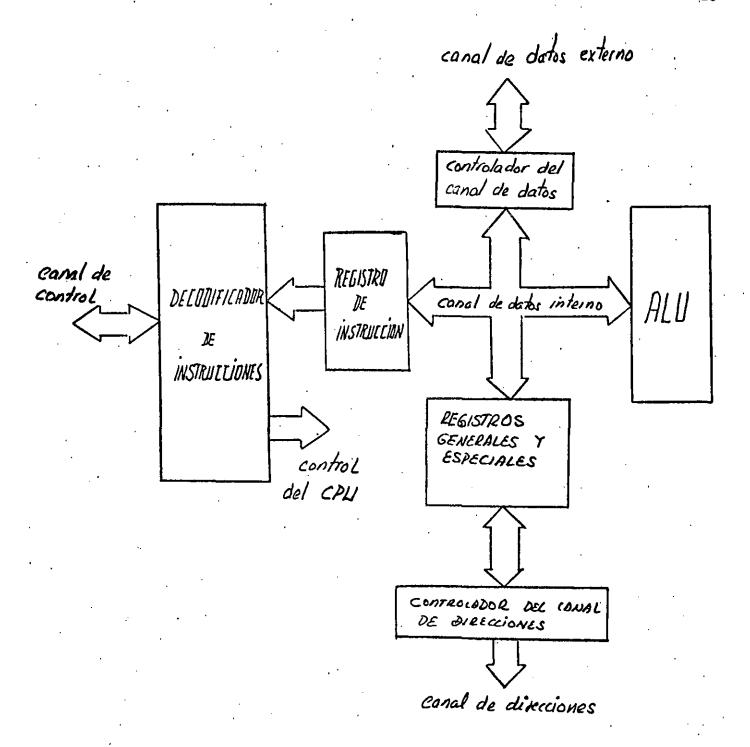

| 21 de septiembre    | 19 a 21 Hrs. | 9.  | MICROPROCESADORES.<br>Arquitectura. Ciclo de operación.<br>Instrucciones. Interrupciones. Operaciones de Entrada/Salida. | . ; . | M. en I. Roberto Daza-Gómez Torres                        |

| 15 de septiembre    | 9 a 14 Hrs.  | 10. | PRACTICA DE LABORATORIO.                                                                                                 |       | Ing. Roberto Macías Pérez<br>Ing. Eduardo Ramírez Sánchez |

| 22 de septiembre    | 9 a 14 Hrs.  | 11. | PRACTICA DE LABORATORIO.                                                                                                 |       | Ing. Roberto Macías Pérez<br>Ing. Eduardo Ramírez Sánchez |

# EVALUACION DEL PERSONAL DOCENTE

| CUR | TOS                                  | DOMINIO DEL TEMA . | EFICIENCIA EN EL USO DE<br>AYUDAS AUDIOVISUALES | MANTENIMIENTO DEL<br>INTERES. (COMUNICACION CON<br>LOS ASISTENTES, AMENIDAD,<br>FACILIDAD DE EXPRESION). | PUNTUALIDAD |   |

|-----|--------------------------------------|--------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------|---|

|     | CONFERENCISTA                        |                    |                                                 | ,                                                                                                        |             |   |

| 1.  | M. EN C. ANASTASIO MONTIEL MAYORGA   |                    |                                                 |                                                                                                          |             |   |

| 2.  | M. EN C. HUGO CALLEJA GJUMLICH       |                    |                                                 |                                                                                                          |             |   |

| 3.  | ING. ROBERTO MACIAS PEREZ            | ·                  |                                                 | - '                                                                                                      |             |   |

| 4.  | ING. EDUARDO RAMIREZ SANCHEZ         |                    | ,                                               |                                                                                                          |             |   |

| 5.  | M. EN I. ROBERTO DAZA - GOMEZ TORRES |                    |                                                 |                                                                                                          |             |   |

| 6.  |                                      |                    |                                                 | _                                                                                                        |             |   |

| 7.  |                                      |                    |                                                 | •                                                                                                        |             |   |

| 8.  |                                      |                    |                                                 |                                                                                                          |             |   |

| 9.  |                                      |                    |                                                 |                                                                                                          |             | · |

|     | ESCALA DE EVALUACION: 1 a 10         |                    |                                                 |                                                                                                          |             |   |

|         |   |     | • |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|---------|---|-----|---|---|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|         |   |     |   |   |        |            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •           |

|         |   |     |   |   |        |            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

|         |   |     |   |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|         | • |     |   |   | • .    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|         | • |     |   | , |        |            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,           |

| •       |   | ÷   |   |   | •      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·           |

| •       |   |     |   |   | t in a | ·          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·<br>7<br>1 |

|         |   |     |   | · |        | •          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| <br>    |   | •   |   |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| ·       |   |     |   |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| · · · · |   | •   |   |   |        | <b>`</b> * |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| *       |   | . ' |   |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|         | • |     | • |   | •      | · .        | The state of the s |             |

|         |   |     |   |   |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|         |   |     |   |   | •      |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

|         |   |     | • | ٠ |        | •          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|         |   |     |   |   | ,      |            | . ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

|         |   |     |   |   | •      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

# EVALUACION DE LA ENSEÑANZA

| SU EVALUACION SINCERA NOS AYUDARA A MEJORAR LOS PROGRAMAS POSTERIORES QUE DISEÑAREMOS PARA USTED. | ORGANIZACION Y DESARROLLO<br>DEL TEMA | GRADO DE PROFUNDIDAD<br>LOGRADO EN EL TEMA | GRADO DE ACTUALIZACION<br>LOGRADO EN EL TEMA | UTILIDAD PRACTICA DEL<br>TEMA |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------|----------------------------------------------|-------------------------------|--|

| INTRODUCCION                                                                                      |                                       |                                            |                                              |                               |  |

| EL DIODO                                                                                          |                                       |                                            |                                              |                               |  |

| EL TRANSISTOR                                                                                     |                                       |                                            |                                              |                               |  |

| TIRISTORES                                                                                        |                                       |                                            | ·                                            |                               |  |

| EL AMPLIFICADOR OPERACIONAL                                                                       |                                       |                                            |                                              |                               |  |

| GENERADORES DE ONDAS                                                                              |                                       |                                            |                                              |                               |  |

| CIRCUITOS DIGITALES                                                                               |                                       |                                            |                                              | ·                             |  |

| CONVERTIDORES A/D Y D/A                                                                           |                                       |                                            |                                              |                               |  |

| MICROPROCESADORES                                                                                 | ,                                     |                                            |                                              |                               |  |

| PRACTICA DE LABORATORIO                                                                           | •                                     |                                            |                                              |                               |  |

| 'edcs. FSCALA DE EVALUACION: La 10                                                                |                                       |                                            | 4 .                                          |                               |  |

# EVALUACION DEL CURSO

|    | CONCEPTO                                        | EVALUACION |

|----|-------------------------------------------------|------------|

| ۱. | APLICACION INMEDIATA DE LOS CONCEPTOS EXPUESTOS |            |

| 2. | CLARIDAD CON QUE SE EXPUSIERON LOS TEMAS        |            |

| 3. | GRADO DE ACTUALIZACION LOGRADO CON EL CURSO     |            |

| 4. | CUMPLIMIENTO DE LOS OBJETIVOS DEL CURSO         |            |

| 5. | CONTINUIDAD EN LOS TEMAS DEL CURSO              |            |

| 6. | CALIDAD DE LAS NOTAS DEL CURSO                  |            |

| 7. | GRADO DE MOTIVACION LOGRADO CON EL CURSO        |            |

## ESCALA DE EVALUACION DE I A 10

| MUY AGRADABLE                                                                 |              |               | AGRADABLE                        |          | DESAGR                         | ADABLE        |

|-------------------------------------------------------------------------------|--------------|---------------|----------------------------------|----------|--------------------------------|---------------|

|                                                                               |              |               |                                  |          |                                |               |

| Medio de comunicaci                                                           | ón por el    | que se        | enteró del                       | l curso  | :                              |               |

| PERIODICO EXCELSION<br>ANUNCIO TITULADO DI<br>VISION DE EDUCACION<br>CONTINUA | ANUN<br>VISI | ICIO TIT      | OVEDADES<br>ULADO DI<br>DUCACION | <u>.</u> | FOLLETO I                      | DEL CURS      |

|                                                                               |              | · <del></del> |                                  | <u> </u> |                                | · <u></u>     |

| CARTEL MENSUA                                                                 | L R          | DIO UNI       | VERSIDAD                         |          | COMUNICAO<br>TELEFONO,<br>ETC. |               |

|                                                                               |              |               |                                  |          |                                |               |

| REVISTAS TECNICAS                                                             | FOLLETO      | ANUAL         | CARTELER<br>UNIVERSI             |          |                                | GACET<br>UNAM |

|                                                                               |              |               |                                  |          | ·                              |               |

| Medio de transporte                                                           | utilizad     | o para        | venir al Pa                      | alacio   | de Mineri                      | ia:           |

| AUTOMOVIL<br>PARTICULAR                                                       |              | METR          | 0                                |          | OTRO MEI                       | 010           |

| Qué cambios haría                                                             | usted en     | el prog       | rama para t                      | tratar   | de perfe                       | cionar        |

|                                                                               | ·            |               |                                  |          |                                |               |

|                                                                               |              |               |                                  |          | •                              |               |

|                                                                    |                          |                        | •                                            |                    |

|--------------------------------------------------------------------|--------------------------|------------------------|----------------------------------------------|--------------------|

| La coordinació                                                     | n académic               | ca fue:                |                                              |                    |

| EXCELENTE                                                          | BUENA                    |                        | REGULAR                                      | MALA               |

|                                                                    |                          | ·                      |                                              |                    |

| Si está intere:<br>más conveniente                                 | sado en to<br>e para usi | omar alg               | un curso intensi                             | vo ¿Cuál es el hor |

| LUNES A VIERNI<br>DE 9 A 13 H. Y<br>DE 14 A 18 H.<br>(CON COMIDAS) | / VIERN                  | S A<br>VES DE<br>21 H. | LUNES, MIERCOL<br>Y VIERNES DE<br>18 A 21 H. | DE 18 A 21 H.      |

|                                                                    |                          |                        |                                              |                    |

| VIERNES DE 17<br>SABADOS DE 9 A                                    |                          |                        | DE 17 A 21 H.<br>DE 9 A 13 Y<br>18 H.        | OTRO               |

|                                                                    |                          | <del></del>            |                                              |                    |

| Qué servicios<br>ontinua, para                                     | adicional<br>los asist   | es dese<br>entes?      | aría que tuviese                             | la División de Ed  |

|                                                                    |                          |                        |                                              |                    |

| tras sugerenci                                                     | as:                      |                        |                                              |                    |

DISPOSITIVOS Y CIRCUITOS ELECTRONICOS

ING.ANASTASIO MONTIEL MAYORGA

ING. HUGO CALLEJA GJUMLICH

ING. ROBERTO MACIAS PEREZ

ING. EDUARDO RAMIREZ S.

SEPTIEMBRE, 1984.

### 1.0 INTRODUCCION

Como los equipos y sistemas electrónicos están integrados por la interconexión de una gran variedad de elementos, algunos de ellos familiares y otros simplemente desconocidos, resulta obvio que el conocimiento más o menos claro de la operación de dichos dispositivos, y el de las leyes que regulan tanto su funcionamiento como la interacción entre ellos, constituyen las herramientas fundamentales de trabajo en esta área.

Por esta razón, en este curso básico se presentan en forma simple y simplificada, tanto los aspectos del funcionamiento de los dispositivos electrónicos más comunes, como las técnicas de análisis y diseño de los circuitos más representativos de sus aplicaciones.

También a fin de hacer este curso autosuficiente, se abordan desde los conceptos básicos antecedentes hasta algunos más avanzados, aplicados tanto a la electrónica analógica como a la digital.

#### 1.1 SEÑAL

Desde el punto de vista del área de estudio y de itras áreas afines, una señal es cualquier variable física que contiene información en alguna de sus característi cas, por ejemplo, en su magnitud o en alguna variación con el tiempo. La información puede ser cualquiera: voz, música, imágenes, datos numéricos, etc. En cambio, las variables físicas que pueden contener la información en un sistema eléctrico son la corriente y el voltaje. Sin embargo, en otros sistemas las variables portadoras de información pueden ser diferentes; en el caso de un sistema mecánico, por ejemplo, la fuerza y la velocidad; en un sistema hidráulico, la presión y el gasto; etc. Con mucha frecuencia estos últimos sistemas y otros más, se modelan con un sistema eléctrico equivalente, de tal forma, que un entendimiento claro de los sistemas eléctricos permite comprender una gran variedad de fenómenos.

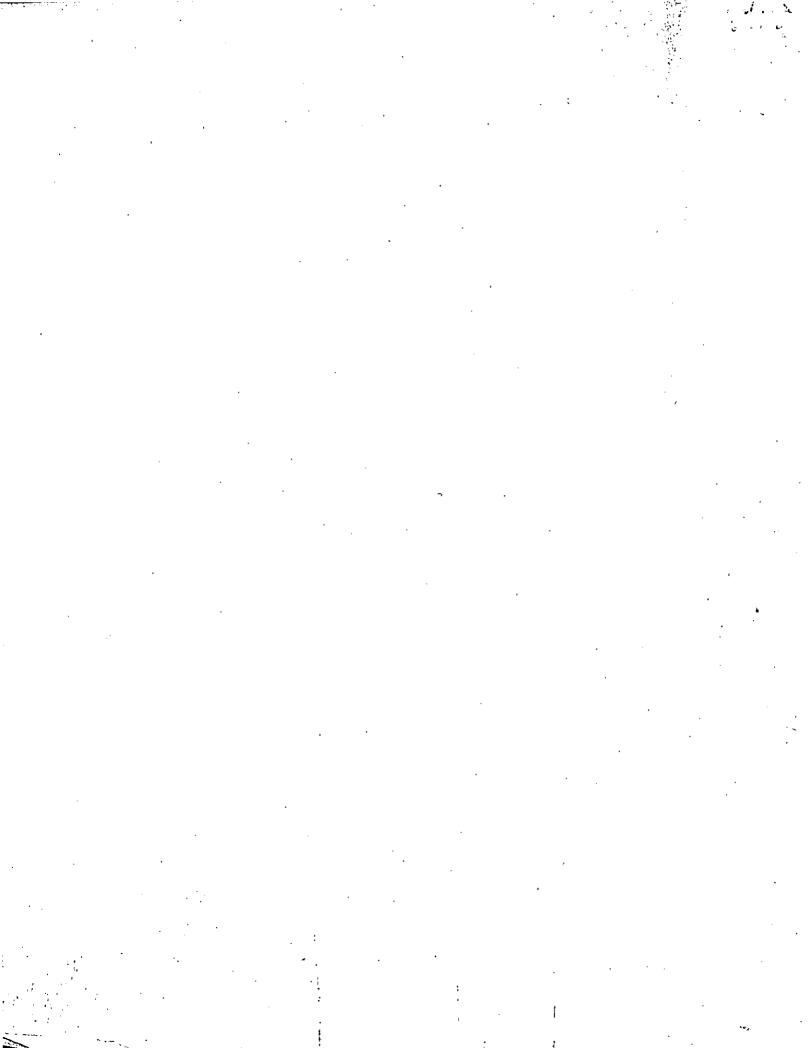

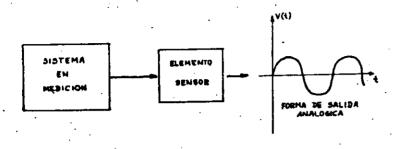

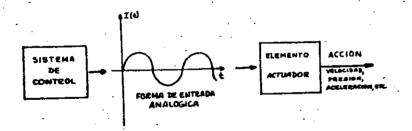

La información puede ser llevada en dos formas diferentes: en forma analógica o digital. En una Señal Analógica la información está contenida en alguna característica continua del voltaje o la corriente, tal como la amplitud o la frecuencia. Por ejemplo, en la Fig. 1.1, el voltaje es producido por los termopares cuando están a diferentes temperaturas. Cuando la diferencia de temperaturas varía, el voltaje también varía, de tal forma que el voltaje es una representación "análoga" de la diferencia de temperaturas.

Figura 1.1 Ejemplo de Señal Analógica

una Señal Digital, en su forma más simple, es aquella que puede tomar uno de dos valores discretos a la vez. Se utiliza para representar información del tipo "ON-OFF" ó "SI-NO", o bién, números o la ocurrencia de eventos. Un ejemplo sencillo es lo que ocurre en un horno automático. Cuando la temperatura del horno baja de cierto nivel, el interruptor del termostato se cierra, encendiéndose el horno; y cuando la temperatura de la temperatura de la alcanzado cierto nivel adecuado, el interruptor se abre, apagándose el horno. Es decir, el termostato provee una señal digital que controla al horno, si el interruptor se cierra significa que la temperatura es muy fría y el horno pasa al estado "ON" o encendido, mientras que si se abre, el horno pasa al estado "OFF" o apagado, indicándose que la temperatura es adecuada.

Las señales digitales pueden estar representadas por niveles de CD, pulsos, trenes de pulsos, pulsos codif $\underline{i}$  cados y algunas otras variantes.

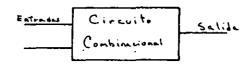

#### 1.2 EL SISTEMA DE PROCESAMIENTO DE SEÑALES

Un sistema de procesamiento de señales es la interconexión de componentes y dispositivos que pueden aceptar una o varias señales de entrada, operar sobre ellas para extraer o corregir la información, y presentarla como una o varias salidas en un tiempo y en una forma adecuada.

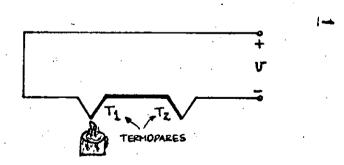

La Fig. 1.2 ilustra las componentes de un sistema generalizado. Los círculos representan los dos tipos de procesamiento que se pueden tener -analógico y digital - mientras el bloque central, representa la conversión de señales analógicas a digitales (A/D) y vicever

sa (D/A), que es necesario efectuar para que las señales analógicas y digitales puedan interactuar.

Para obtener las señales de interés a partir de los sistemas físicos, se usan transductores. Estos son dis positivos que convierten las variables físicas a una señal de corriente o voltaje. Un ejemplo es el termopar utilizado anteriormente, el cual convierte la temperatura a un voltaje.

Figura 1.2 Componentes de un Sistema de Procesamiento de Señales.

Por último, las salidas pueden darse en varias formas, dependiendo de qué se desee hacer con ellas. Por ejem plo, algunas pueden ir a un dispositivo de despliegue o "display", que puede ser analógico o digital; otras pueden convertirse en señales audibles, etc.

#### 1.3 SISTEMAS ANALOGICOS, DIGITALES E HIBRIDOS

Se dice que un sistema es analógico o digital, cuando las señales que procesa tienen esa característica. En los sistemas híbridos, una parte del procesamiento se efectúa sobre las señales en estado analógico y la otra, en estado digital.

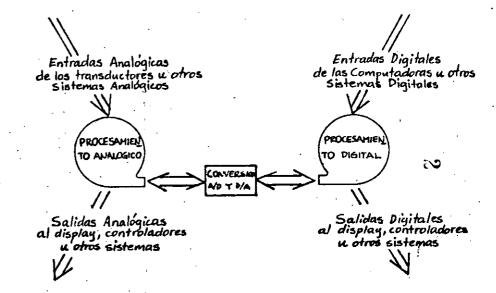

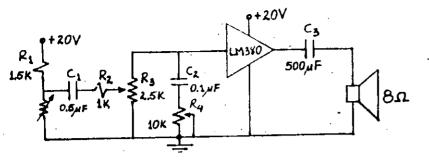

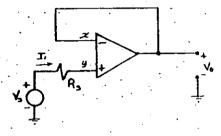

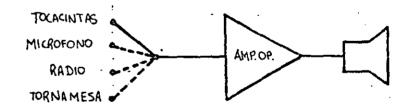

Un ejemplo muy simple de sistema analógico es el amplificador de audio, cuyo diagrama de bloques se muestra en la Fig. 1.3a. El micrófono de carbón realiza la función de transductor, ya que convierte las variaciones de la presión del aire que llegan a su superficie, en variaciones de su resistencia eléctrica interna. Para obtener una señal eléctrica, estas variaciones en la resistencia del micrófono se convierten a voltaje, hacciendo circular una corriente constante a través del micrófono. Con una corriente constante de unos 11 mA, un micrófono de carbón típicamente entrega un voltaje de pico de unos 220 mV a circuito abierto, y presenta una resistencia promedio de CA de unos 250  $\Omega$ .

Figura 1.3 Ejemplo de Sistema Analógico; El ampl<u>i</u>

ficador de audio.

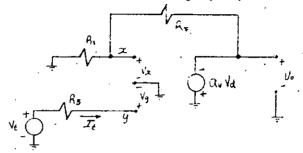

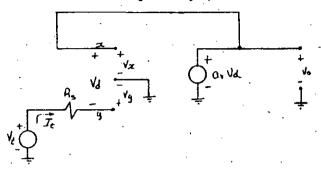

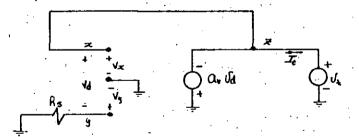

Para fines de análisis o diseño, el micrófono puede modelarse con una fuente de voltaje dependiente de la presión—del aire v(p), en serie con su resistencia interna de  $250\Omega$ ; y la bocina con una resistencia de carga  $R_{L}$ , por ejemplo,  $8\,\Omega$ , como se muestra en la Fig. 1.3b.

La función del amplificador es incrementar el nivel de potencia para que al ser aplicado a la bocina, el sonido sea tan audible como se desee. Si por ejemplo, se requie ren 5W de pico en la bocina de  $8\,\Omega$ , se necesita un amplificador que entregue un voltaje de salida de  $V_1=(5Wx8\,\Omega)^{1/2}=6.3V$  de pico; y si la amplitud de pico del voltaje de entrada se considera 220 mV, la ganancia de dicho amplificador deberá ser  $A_0=6.3/0.22=28.7$ .

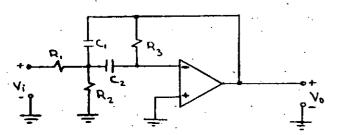

Para la realización física de este pequeño amplificador de audio, es necesario adicionar algunos otros elementos, como se muestra en la Fíg. 1.4. La fuentes de corriente constante está constituida por la batería y la resistencia en serie R<sub>1</sub>; se han agregado un control de volumen R<sub>3</sub> y un control de tono C<sub>2</sub> y R<sub>4</sub>, así como los capacitores C<sub>1</sub> y C<sub>3</sub> que bloquean la componente de CD para que no pase al amplificador ni a la carga, respectivamente. Como en este caso la potencía que se desea en la carga es baja, se puede utilizar como elemento amplificador un solo circuito integrado.

Sin embargo, cuando los niveles de potencia son altos, es necesario diseñar o disponer de etapas amplificadoras de potencia, las cuales generalmente están constituidas por elementos discretos de potencia. En este último caso, los circuitos integrados pueden utilizarse como etapas preamplificadoras de baja y mediana potencia.

Figura 1.4 Amplificador de Audio

Algunos otros aspectos que deben considerarse en el diseño de este simple amplificador son, por ejemplo, la respuesta en frecuencia, la distorsión, la estabilidad de operación y otros.

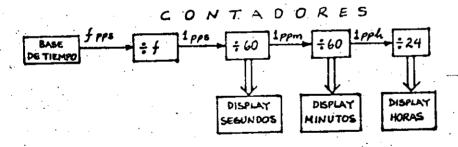

Para contrastar la operación de un sistema digital con el analógico que acabamos de tratar, considérese el caso, también muy simple, de un reloj digital cuyo diagrama de bloques se muestra en la Fig. 1.5. Consiste en una base de tiempo, contadores de pulsos y dispositivos de display.

Figura 1.5 Ejemplo de Sistema Digital: El Reloj Digital.

La base de tiempo es un oscilador electrónico, el cual entrega f pulsos por segundo. Si la salida de este os-

ciiador se conecta a la entrada de un contador que cuando la cuenta llega a los f pulsos, entrega un pulso a su

salida, se tendrá un pulso por segundo. Un segundo contador en cascada contará hasta sesenta y dará un pulso a

su salida, el cual ocurre cada minuto y así sucesivamente.

Como los contadores disponen de terminales de salida en

las que aparece la cantidad de pulsos contados, éstas se

conectan a los dispositivos de despliegue que son los in

dicadores del tiempo del reloj.

Cabe señalar que la exactitud del reloj está determinada por la exactitud con que la base de tiempo entrega los f pulsos por segundo.

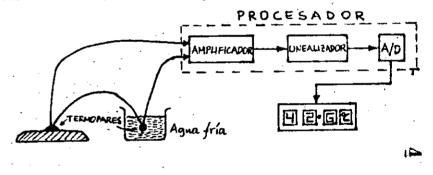

Como ejemplo de sistema hibrido, considérese el diagrama de bloques de la Fig. 1.6 que representa los elementos básicos de un termómetro digital.

Figura 1.6 Ejemplo de Sistema Híbrido: Termómetro Digital.

La pareja de termopares, uno de ellos unido al objeto del que se desea medir la temperatura, y el otro sume<u>r</u> gido en agua fría para tener un punto estable de referencia, entregan al procesador un voltaje que depende

de la diferencia de temperaturas entre ellos, como se vió anteriormente. Debido a que el voltaje que entre gan los termopares es muy pequeño, se requiere de una etapa inicial de amplificación. Además, como la respuesta de estos elementos no es lineal, es necesario efectuar una corrección a través del linealizador. Finalmente, el A/D convierte la señal analógica en digital y es enviada al dispositivo de despliegue.

Como la función primordial de los sistemas electrónicos es el procesamiento de señales, y este presenta una amplia gama de variantes, durante el desarrollo del curso se continuarán analizando otros sistemas, con el fin de reforzar las ideas iniciales presentadas en los ejemplos antertores.

## 2.0 EL DIODO

Existen en el mercado una gran variedad de diodos, desde bulbos al vacío o de gas, hasta los diodos de juntura P-N, tales como los diodos rectificadores de potencia, diodos Zener, diodo Túnel, varactores, diodos emisores de luz, etc., y los de juntura metal-semiconductor, entre los que se pueden señalar: el rectificador de selenio, el de cobre-óxido cuproso, el de magnesio-sulfuro cúprico, el de punta de contacto y el de barrera Schottky. Puede decirse que de estos últimos, los tres primeros práctica mente han desaparecido por sus fuertes limitaciones en cuanto a costo, tamaño y capacidad de potencia. Lo ante rior también es válido para los bulbos, los cuales han sido desplazados totalmente por los de juntura P-N.

La importancia de los dispositivos semiconductores es fácilmente explicable, si se considera que en la actualidad predominan en la gran mayoría de las aplicaciones de bido a su bajo costo, reducidas dimensiones, alto rendimiento, larga vida, aceptables niveles de potencia y temperaturas de operación, fácil manejo y otras características adicionales.

Como el diodo semiconductor o juntura P-N, es la base de casi todos los dispositivos de estado sólido, en esta -- sección, aunque sea a nivel cualitativo, se presentan al gunos aspectos sobresalientes de su funcionamiento y construcción, lo cual permitirá comprender la operación de estructuras más complejas, así como el modelado de las mismas considerando las restricciones impuestas por la aplicación.

S.

Si se preguntara ¿qué es un material semiconductor?, una de las posibles respuestas sería: es un material medio buen conductor eléctrico, o bién, un semiconductor no es ni un buen conductor ni un buen aislador. Desgraciadamente ambas definiciones, que se derivan del significado del prefijo "semi", resultan imprecisas y poco útil cuando se trata de comprender porqué los dispositivos de estado sólido están fabricados de estos materiales. En realidad son varias las características que hacen diferente a un material semiconductor de un conductor, como se establecerá en esta sección.

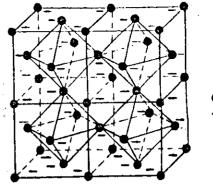

La mayorfa de los conductores sólidos de electricidad pueden clasificarse en metales y semiconductores. Am bos presentan una estructura atómica cristalina, es decir, sús átomos están ordenados en una forma regular constituyendo la red estructural del material. Por ejemplo, en la Figura 2.1 se muestra la estructura cristalina cúbica que presentan algunos buenos con ductores, tales como el cobre, la plata y el aluminio. Las fuerzas atractivas interatómicas que mantienen casi inmóviles a los iones que integran la estructura, son de origen electrostático, y el tipo de enlace es metálico, en el cual los electrones de valencia no están fijos en los enlaces, sino más bien, pueden mover se libremente en todo el cristal.

• IÓN POSITIVO - ELECTRÓN

Figura 2.1 Estructura cristalina que presentan algunos metales.

Una representación más común de la estructura atómica que presentan los metales, es la indicada en la Fig. 2.2, conocida como "modelo electrón-gas" de un metal, en donde los iones positivos aparecen sumergidos en un "gas" o "mar" de electrones libres.

Figura 2.2 Modelo electrón-gas de un metal.

En este esquema se ha considerado que cada átomo metálico contribuye solamente con un electrón, el de yale<u>n</u> cleo y los electrones internos restantes.

Como los átomos de cualquier sólido tienen una concentración volumétrica del orden del número de Avogadro, aproximadamente  $6 \times 10^{2.3}$  átomos/cm³, consecuentemente, si cada átomo contribuye con un electrón libre, se tendrán también  $6 \times 10^{2.3}$ electrones libres/cm³.

Esta es la razón de que los metales sean buenos conductores eléctricos, disponen de grandes concentraciones de electrones libres o móviles, que pueden moverse muy fácilmente bajo el influjo de un campo eléctrico exteno aplicado.

De esta descripción cualitativa pueden deducirse algunas conclusiones importantes:

- a) El metal continúa siendo eléctricamente neutro en su conjunto, porque la carga negativa que represen tan los electrones libres, es exactamente igual a la carga positiva de los iones.

- b) En un metal, la corriente es conducida por un solo tipo de carga móvil: los electrones libres. Los iones no se mueven porque permanecen fijos constituyendo la estructura cristalina del material.

- c) La densidad de los portadores de carga o electrones libres que participan en el proceso de conducción, depende principalmente del número de electrones de valencia que tengan los átomos que forman el material. Es decir, para un metal dado, la densidad de portadores es fija.

### 2.1.1 SEMICONDUCTORES INTRINSECOS O PUROS

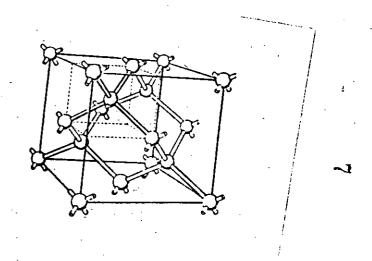

Como se señaló anteriormente, también los materiales semiconductores presentan una estructura cristalina. En la siguiente figura se muestra la estructura que presentan el silicio y el germanio, que son los dos semiconductores más utilizados en la fabricación de dispositivos.

Figura 2.3 Estructura cristalina del silicio y del germanio.

En este caso, las fuerzas atractivas también son de origen electrostático pero el enlace es del tipo covalente, en el cual dos átomos comparten dos electrones. En este caso, cada átomo está en el centro de un tetraedro regular y comparte sus cuatro electrones de valencia con cua

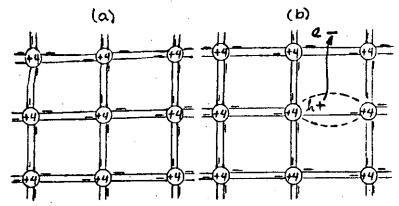

tro átomos vecinos y equidistantes. Las caracteristicas esenciales de esta estructura, pueden representarse en un diagrama bidimensional como se muestra en la Figura 2.4a, la cual corresponde a la situación que prevalece a muy baja temperatura, aproximadamente 0°K. Como los electrones de valencia están ocupando sus respectivos lugares en los enlaces covalentes, no hay electrones libres dispuestos a conducir la corriente y por este motivo, los semiconductores se comportan como buenos aisladores a muy bajas temperaturas.

Figura 2.4 Diagrama bidimensional que muestra los enlaces covalentes de los materiales semiconductores.

(a) T = 0°K, (b) T = 300°K.

A temperatura ambiente, aproximadamente unos 300°K, la energía suministrada a los electrones de valencia por el incremento en la temperatura, es lo suficientemente grande como para que algunos enlaces covalentes se rom pan, provocando que algunos átomos se ionicen y se -- creen electrones libres. Esta situación se muestra en la Fig. 2.4b. La cantidad de electrones libres generados de esta forma, en realidad es muy pequeña, por ejemplo, en el germanio a temperatura ambiente se rompen unos 10<sup>23</sup> átoplamente se tiene un electrón libre por cada

10<sup>10</sup> stomos. A pesar de lo anterior, el efecto que se tiene en las características eléctricas del material es enorme, ya que se hace posible la conducción donde no la había, el material es considerado un semiconductor porque no dispone de la gran concentración de electrones libres presentes en un metal, ni tampoco esta concentración es tan pequeña como en los aisladores, en donde, por ejemplo en el caso del diámante, se tiene un enlace covalente roto por cada 10<sup>15</sup> átomos.

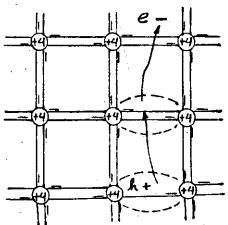

Al romperse un enlace covalente, el electrón deja un lu gar vacío conocido como hueco, que puede ser ocupado por otro electrón vecino. Este último hecho se muestra en la Fig. 2.5, y constituye un movimiento de carga en el que no intervienen los electrones libres. De hecho, esta es otra característica fundamental que hace diferente a un semiconductor de un metal; en el primero, la corriente es debida al flujo de electrones libres y al de los electrones de enlaces que ocupan sucesivamente los lugares de los huecos, y en el último, como se concluyó anteriormente, la corriente es debida exclusivamente al flujo de electrones libres.

Figura 2.5 El electrón del enlace covalente vecino puede ocupar la posición de un hueco.

#### 2.1.3 DENSIDAD DE CORRIENTE

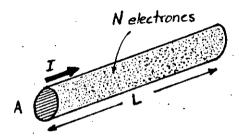

Considérese un conductor de longitud L y sección transversal de área A, conteniendo N electrones libres, como se muestra en la siguiente figura.

Figura 2.7 Segmento de conductor.

Si un electrón recorre la distancia L metros en un tiempo de T segundos, la corriente que es la carga total que atravieza cualquier sección transversal del conductor por unidad de tiempo, será:

$$I = \frac{Nq}{T} \tag{2.8}$$

y como T = L/v, donde v es la velocidad promedio o velocidad de arrastre que experimentan los electrones al apl<u>i</u> car un campo eléctrico, se tiene

$$I = \frac{Nqv}{L} \tag{2.9}$$

Ahora bién, por definición la densidad de corriente J es la corriente por unidad de área, es decir:

$$J = \frac{Nqv}{IA} \tag{2.10}$$

como LA es el volumen, N/LA es la concentración de electrones n:

$$J = nqv \qquad (2.11)$$

y como v puede representarse por  $v = \mu_n \varepsilon$ , donde  $\mu_n$  es la movilidad de los electrones que está dada en  $\{\frac{m^2}{V \cdot s}\}$ , sustituyendo en (2.11), se obtiene

$$J = qn u_n \epsilon = \sigma \epsilon$$

(2.12)

donde:

$$\sigma = nqu_n \tag{2.13}$$

es la conductividad del metal en  $(\Omega-m)^{-1}$

Para el caso de un semiconductor, la expresión (2.12) no es aplicable directamente porque como se recordará, el mecanismo de conducción en un semiconductor es pipo lar, involucra el movimiento de electrones negativos y huecos positivos. Aunque estas partículas se mueven en direcciones opuestas bajo la acción de un mismo cam po eléctrico, como tienen signos opuestos, las corrientes tienen la misma dirección. Por ello, la densidad de corriente de arrastre para los huecos, electrones y la total, será:

$$Jp = p \mu_p q \varepsilon \qquad (2.14)$$

$$J_n = n u_n q \varepsilon \qquad (2.15)$$

$$J = (n\mu_n + p\mu_n)$$

$q \in \pm \sigma \in$  (2.16)

donde:

n = concentración de electrones libres

Pn = movilidad de los electrones

p = concentración de huecos