# PROCESAMIENTO DIGITAL DE SEÑALES

#### SEGUNDA PARTE

# MICROCONTROLADORES Y REALIZACIÓN DE LOS FILTROS CON TMS320CXX

# BOHUMIL PŠENIČKA LARRY ESCOBAR

UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

FACULTAD DE INGENIERÍA

DIVISIÓN DE INGENIERÍA ELÉCTRICA

DEPARTAMENTO DE TELECOMUNICACIONES

MÉXICO 1997

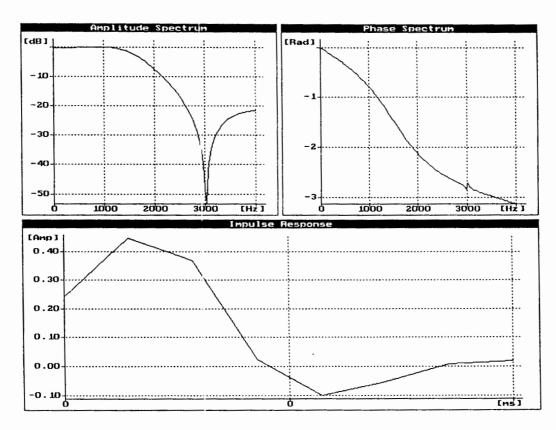

#### APUNTE187-B FACULTAD DE INGENIERIA UNAM.

G.- 611449

PŠENIČKA, Bohumil y Larry Escobar. Frocesamiento digital de señales. Microcontroladores y realización de los filtros con TMS320CXX, 2º parte. México, UNAM, Facultad de Ingeniería, 1997, 178 pp., ils.

APUNTE 187-B FACULTAD DE INGENIERIA UNAM.

Procesamiento digital de señales. Microcontroladores y realización de los filtros con TMS320CXX, 2ª parte.

Prohibida la reproducción o transmisión total o parcial de esta obra por cualquier medio o sistema electrónico o mecánico (incluyendo el fotocopiado, la grabación o cualquier sistema de recuperación y almacenamiento de información), sin consentimiento por escrito del editor.

Derechos reservados.

©1997, Facultad de Ingeniería, Universidad Nacional Autónoma de México. Ciudad Universitaria, México, D.F.

Primera edición, septiembre 1997.

ISBN 968-36-6473-3 Impreso en México.

# Prólogo

G-11/19

Con el avance de la tecnología, la computadora se ha convertido en una herramienta fundamental en la simulación y el procesamiento digital de señales (PDS), por lo cual constituye una solución real para los problemas de medición, control, filtrado, análisis espectral, sistemas de comunicaciones, etc.

Entre las áreas de interés que conforman el PDS están el análisis de señales y sistemas, el análisis y síntesis de filtros digitales, la identificación de sistemas, la ingeniería de software, la arquitectura de microcomputadoras y el diseño con circuitos con muy alta escala de integración (VLSI). Las tareas del PDS se realizan eficiente y sistemáticamente a través de sistemas que combinan la tecnología de los circuitos VLSI con una gran variedad de algoritmos matemáticos y con el software necesario para su implementación.

Uno de los objetivos de un sistema de PDS es proveer una mejor aproximación al análisis o estimación contenido de la información. El análisis de señales es el proceso de definir y cuantificar las características de una señal o para una aplicación. Con el desarrollo de las comunicaciones, el PDS y los procesadores de señales digitales (DSP), que se realizan mediante los microcontroladores, se han convertido en una herramienta necesaria para cualquier sistema digital, por lo que la tendencia al uso de estos sistemas es cada día mayor.

A fin de fortalecer la asignatura de Procesamiento digital de señales que cursan los estudiantes de las carreras de electrónica, telecomunicaciones y computación, las cuales se imparten en la Facultad de Ingeniería de la UNAM, y contribuir a la enseñanza y aprendizaje de los DSP, los autores han tenido el empeño de elaborar este libro con objeto de explicar cómo se realizan los filtros digitales mediante los microprocesadores de la familia de DSP de TMS320 de la compañía Texas Instruments, principalmente el TMS320C25 de aritmética entera y el TMS320C30 de aritmética flotante, así como describir sus características en hardware y software, sus formas de programarlos, dar ejemplos y algunas aplicaciones.

El hecho de elegir esta familia es porque son los DSP que más se han difundido en el mercado y los que un ingeniero encontraría en la práctica profesional, a pesar de este enfoque, también se proporciona a los alumnos las bases de lo que es un DSP y las formas de presentar algoritmos propios del PDS, lo que da lugar a que cualquier DSP diferente a los tratados no sea difícil de utilizar.

El libro está dividido en 9 capítulos. El primer capítulo fue escrito por el Ing. Larry Escobar y los demás por el Dr Bohumil Pšenička. En los primeros tres se presenta la descripción y arquitectura del TMS320C25 con las instrucciones para escribir los progra-

mas en ensamblador y los ejemplos para la realización de los filtros digitales en cascada, en paralelo, de estado y en la forma de cruz. En los capítulos cuatro, cinco y seis se explica la arquitectura del TMS320C30, herramientas de desarrollo, la EVM y realización de filtros digitales. En los capítulos siete y ocho se describen la arquitectura y el depurador de TMS320C50. En el último capítulo los estudiantes encuentran algunas instrucciones útilos para realizar y analizar los filtros digitales mediante el paquete MATLAB.

Los autores esperan que este libro sea una contribución sólida para los desafíos tecnológicos del futuro que tendrán que enfrentar los ingenieros en telecomunicaciones, electrónica y en computación. Asimismo, agradecen el apoyo a la Facultad de Ingeniería de la UNAM y a las personas que colaboraron en el proceso de edición para que esta obra llegara a publicarse.

> Dr. Bohumil Pšenička Ing. Larry Escobar

Profesores de la Facultad de Ingeniería de la UNAM

# Contenido

| 1 | Des  | cripción y arquitectura del TMS320C25                                  | 9          |

|---|------|------------------------------------------------------------------------|------------|

|   | 1.1  | Descripción general                                                    | 9          |

|   | 1.2  | Características                                                        | 9          |

|   | 1.3  | Arquitectura                                                           | 10         |

|   | 1.4  | Diagrama de bloques funcional                                          | 13         |

|   | 1.5  | Organización de la memoria                                             | 14         |

|   | 1.6  | Sistema de control                                                     | 20         |

| 2 | Inst | trucciones del DSP TMS320C25                                           | 29         |

| 3 | Rea  | alización de filtros digitales con DSP TMS320C25                       | 41         |

|   | 3.1  | Instrucciones del DSP TMS320C25                                        | 41         |

|   |      | 3.1.1 MACD (Multiply and Accumulate with Data Move)                    | 41         |

|   |      | 3.1.2 LT (Load T Register)                                             | 44         |

|   |      | 3.1.3 LTA (Load T Register and Accumulate Previous Product and Move    |            |

|   |      | Data)                                                                  | 45         |

|   |      | 3.1.4 LTD (Load T Register, Accumulate Previous Product and Move Data) | 46         |

|   |      | 3.1.5 LTP (Load T Register and store P register in Accumulator)        | 47         |

|   |      | 3.1.6 PAC (Load Accumulador with P Register)                           | 48         |

|   |      | 3.1.7 LTS (Load T Register, Substract Previous Product)                | 48         |

|   |      | 3.1.8 MPY (Multiply)                                                   | 49         |

|   |      | 3.1.9 MPYA (Multiply and Accumulate Previous Product)                  | 50         |

|   |      | 3.1.10 MPYS (Multiply and Subtract Previous Product)                   | 51         |

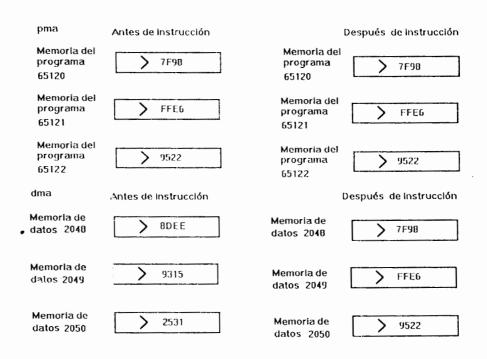

|   |      | 3.1.11 BLKD (Block Move from Data to Data Memory)                      | 52         |

|   |      | 3.1.12 BLKP (Block Move from Program to Data Memory)                   | 53         |

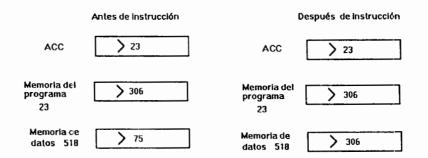

|   |      | 3.1.13 TBLR (Table Read)                                               | 55         |

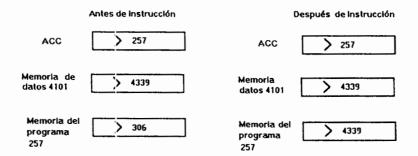

|   |      | 3.1.14 TBLW (Table Write)                                              | 56         |

|   |      | 3.1.15 IN (Input Data from Port)                                       | 57         |

|   |      | 3.1.16 OUT (Output Data to Port)                                       | 57         |

|   |      | 3.1.17 B (Branch Unconditionally)                                      | 58         |

|   | 3.2  |                                                                        | 59         |

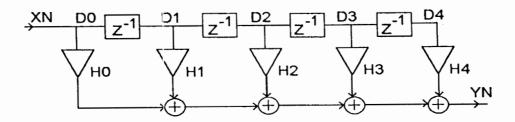

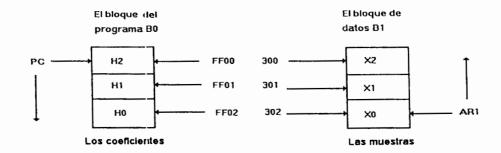

|   |      | 3.2.1 Programa del filtro FIR con los comandos LTD, MPY                | 59         |

|   |      | 3.2.2 Programa del filtro FIR con la instrucción BANZ                  | <b>5</b> 9 |

|   |      | 3.2.3 Programa del filtro FIR usando MACD y RPTK                       | 60         |

|   | 3.3  | Programas en ensamblador para los filtros IIR                          | 61         |

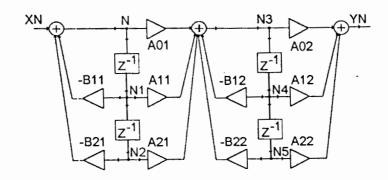

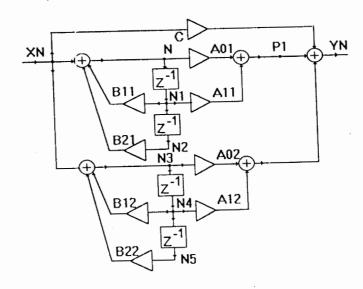

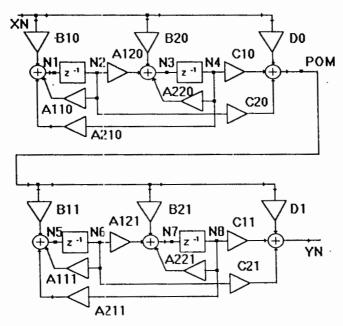

|   |      | 3.3.1 Estructura de cascada                                            | 61         |

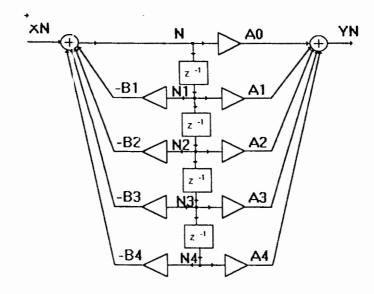

|   |      | 3.3.2 Estructura directa del filtro IIR de 40 orden                    | 64         |

|   |      | 3.3.3          | Estructura paralela del filtro IIR de 40 orden 67  |

|---|------|----------------|----------------------------------------------------|

|   |      | 3.3.4          | Realización de dos filtros de estado en cascada 69 |

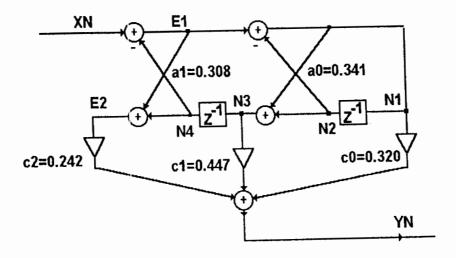

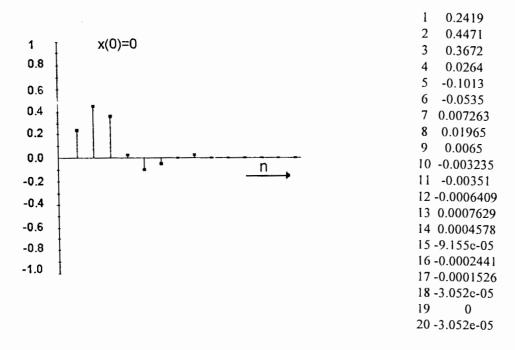

|   |      | 3.3.5          | Diseño del filtro digital en forma de cruz         |

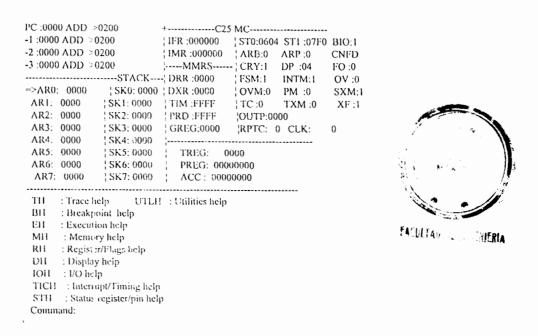

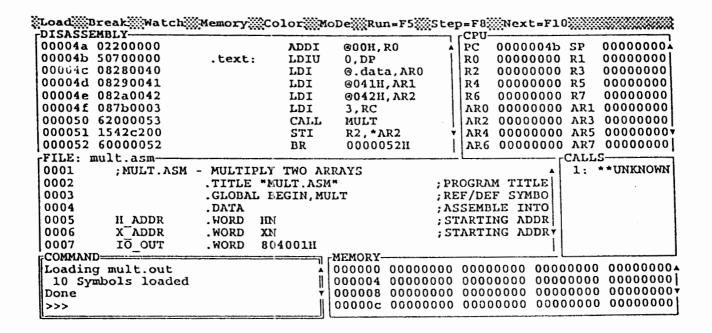

|   | 3.4  | Simulad        | dor del PSD TMS320C25                              |

|   |      |                |                                                    |

| 4 |      | -              | esador TMS320C30 81                                |

|   | 4.1  |                | cción                                              |

|   | 4.2  |                | ectura                                             |

|   | 4.3  |                | central de proceso (CPU)                           |

|   |      |                | Archivo de registros del CPU                       |

|   | 4.4  |                | zación de la memoria                               |

|   | 4.5  | Operac         | ión del bus interno                                |

|   | 4.6  | Operac         | ión del bus externo                                |

|   | 4.7  | $\cdot$ Contro | l de periféricos                                   |

|   | 4.8  | Acceso         | directo a memoria (DMA)                            |

|   | 4.9  | Opera          | ciones con pipeline                                |

|   | 4.10 | Uso de         | los recursos del sistema                           |

|   | 4.11 | Conjun         | to de instrucciones                                |

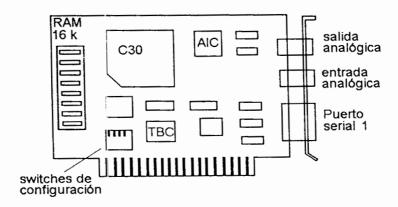

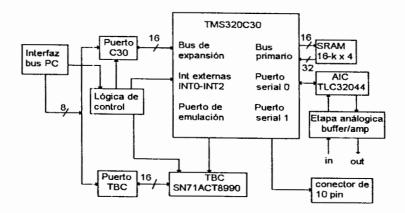

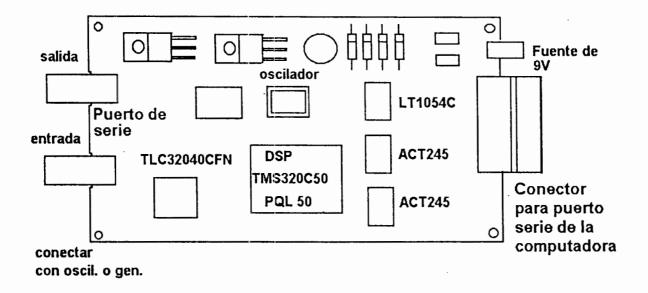

| 5 | Her  | ramien         | ta de desarrollo EVM                               |

|   | 5.1  |                | acción                                             |

|   | 5.2  |                | erísticas generales                                |

|   | 5.3  |                | uración y generación de código                     |

|   | 5.4  |                | nicación entre el host y la EVM                    |

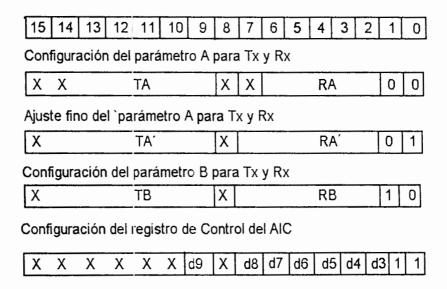

|   | 5.5  |                | o de información desde el TMS320C30                |

|   | 5.6  | · ·            | o del controlador de interfaz analógica            |

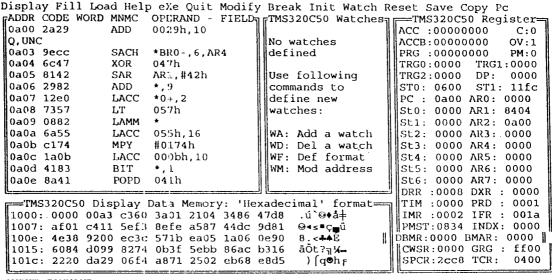

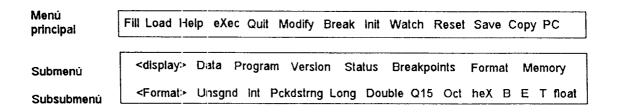

|   | 5.7  |                | re asociado: el depurador de código                |

|   | 0.1  | 5.7.1          | Comandos del depurador de código                   |

|   |      | 0.1.1          | Comandos del deputador de codigo                   |

| 6 | Rea  |                | n de filtros digitales con TMS320C30 123           |

|   | 6.1  | Instru         | cciones del TMS329C30                              |

|   |      | 6.1.1          | MPYF3-Multiplicación en punto flotante             |

|   |      | 6.1.2          | Instrucciones en paralelo MPYF3  ADDF3             |

|   |      | 6.1.3          | Multiplicar y cargar en paralelo MPYF3  STF        |

|   |      | 6.1.4          | Multiplicar y restar en paralelo MPYF3  SUBF3      |

|   |      | 6.1.5          | Cargar en paralelo LDF  LDF                        |

|   |      | 6.1.6          | Instrucciones para entrada y salida                |

|   |      | 6.1.7          | Instrucción de repetición                          |

|   |      | 6.1.8          | Multiplicación con buffer circular                 |

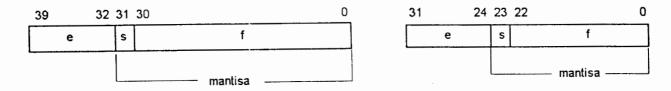

|   | 6.2  | Repre          | sentación de los números en TMS320C30              |

|   | 6.3  |                | amas en ensamblador                                |

|   |      | 6.3.1          | Multiplicación de dos series de números            |

|   |      | 6.3.2          | Multiplicación de las matrices                     |

|   |      | 6.3.3          | Programa con el buffer circular                    |

| 7 | Des | cripción y arquitectura del TMS320C50                      | 143 |

|---|-----|------------------------------------------------------------|-----|

|   | 7.1 | Introducción                                               | 143 |

|   | 7.2 | Características                                            | 143 |

|   | 7.3 | Arquitectura                                               | 144 |

|   | 7.4 | Memoria                                                    | 149 |

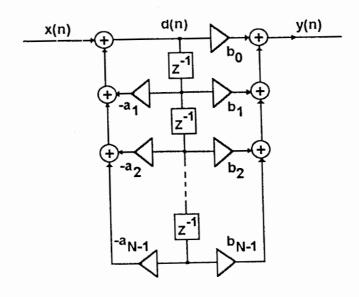

|   | 7.5 | Ejemplos de un filtro de respuesta infinita al impulso IIR | 151 |

| 8 | Des | cripción del ensamblador y depurador DSK                   | 155 |

| 9 | Pro | grama MATLAB para el procesamiento digital de señales      | 159 |

|   | 9.1 | Introducción de datos en MATLAB                            | 159 |

|   | 9.2 | Números complejos y matrices complejas                     | 160 |

|   | 9.3 | Formatos de salida                                         | 161 |

|   | 9.4 | Operaciones con las matrices                               | 161 |

|   | 9.5 | Instrucciones matemáticas elementales                      | 163 |

|   | 9.6 | Vectores y matrices                                        | 165 |

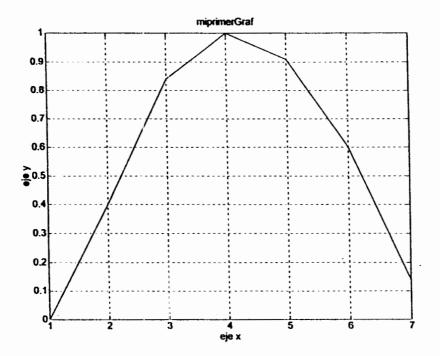

|   | 9.7 | Instrucciones para graficar                                | 166 |

|   | 9.8 | Ejemplos                                                   | 171 |

|   | Bil | bliografía                                                 | 175 |

|   | Ínc | dice analítico                                             | 177 |

# Índice de abreviaturas

- ACC- Acumulador.

- ACCH- La parte alta del acumulador.

- ACCL- La parte baja del acumulador.

- ARAU- Unidad aritmético lógica de los registros auxiliares.

- ARB- Buffer de los registros auxiliares.

- ARP- Apuntador de los registros auxiliares.

- ARx- Registros auxiliares

- CALU- Unidad aritmética lógica central.

- CNFD- Configura bloque BO en la memoria de datos.

- CNFP- Configura bloque BO en la memoria de programa.

- COFF- El archivo ejecutable para EVM de formato común.

- DAB- Bus de datos.

- DP- Apuntador de página.

- DR- Pin del puerto de serie para recepción.

- DRR- Registro para recepción en la forma serial.

- DSP- Procesamiento digital de señales.

- DSK- Archivo ejecutable para starter-kit.

- DX- Pin del puerto de serie para transmisión.

- DXR- Registro para transmisión en la forma serial.

- EVM- Módulo de evaluación.

- FIR- Filtros con respuesta finita.

- GREG- Registro de memoria global.

- IE- Registro de habilitación.

- IF- Registro de banderas.

- IFR- Registro de bandera para interrupción.

- IMR- Registro interrupción mascarable.

- IIR- Filtros con respuesta infinita.

- IRO- Registro índice O.

- IR1- Registro indice 1.

- MIPS- Millones de instrucciones por segundo.

- MUX- Multiplexor.

- PAB- Bus de programa.

- PFC- Registro para direccionar BO.

- PC- Contador de programa.

- PR- Registro P.

- Rx- Registro de precisión extendida.

- RE- Registro de dir. final de repetición.

- RPTC-Registro de repetición.

- RS- Registro de dir. inicial de repetición.

- RSR- Registro de corrimiento para recepción serial.

- STO- Registro de estado O.

- ST1- Registro de estado 1.

- TBC- Controlador de canal de pruebas.

- TR- Registro T.

- VLSI-Muy alta escala de integración.

# Capítulo 1

# Descripción y arquitectura del TMS320C25

La familia de procesadores TMS320 de 16/32 bits de Texas Instruments, empleada para el procesamiento digital de señales (DSP), combina la flexibilidad de un controlador de alta velocidad con la capacidad numérica de un procesador y ofrece una opción para la tecnología VLSI (muy alta escala de integración) y el multiprocesamiento de señales.

Dichas características hacen que esta familia presente una alta capacidad de ejecución, arquitectura de gran funcionalidad y relación costo/efectividad ideal para solucionar diversos problemas en telecomunicaciones, computación, comercio, industria y aplicaciones militares, entre otras.

# 1.1 Descripción general

La combinación de la arquitectura tipo Harvard de la familia TMS320 (separación de los buses de datos y datos de programa) y su conjunto de instrucciones especiales para el DSP proveen una alta velocidad de ejecución y gran flexibilidad. De esta forma, se produce una familia de procesadores capaces de ejecutar 10 MIPS (millones de instrucciones por segundo), ya que se realizan funciones en hardware, que en comparación con otros procesadores, recurren al software o microcódigos para generarlas.

La segunda generación de la familia TMS320 está compuesta de dos procesadores: el TMS32020 y el TMS320C25. La arquitectura de ambos procesadores se basa en la del TMS32010. El TMS32020 trabaja a 20 MHz y ejecuta el doble de instrucciones del TMS32010, mientras que el TMS320C25 incrementa la funcionalidad de la arquitectura en relación al TMS32020.

## 1.2 Características

- Ciclo de instrucción 100 ns.

- 544-palabras de datos programables en memoria RAM interna.

- 4k-palabras de programa en memoria ROM interna.

- 128k-palabras de espacio total de memoria DATOS y PROGRAMA.

- ALU/acumulador de 32 bits.

- Multiplicador paralelo de 16 × 16 bits con producto de 32 bits.

- Instrucciones de multiplicación/acumulación ejecutadas en un ciclo simple de instrucción.

- la strucciones de repetición para uso eficiente del espacio de programa y mejor ejecución.

- Movimiento de bloques para el manejo de DATOS/PROGRAMA.

- Timer integrado para operaciones de control.

- Ocho registros auxiliares con una propia unidad aritmética.

- Un stack por hardware de ocho niveles.

- Dicciséis canales de entrada o salida.

- Un registro de corrimiento paralelo de 16 bits.

- Posibilidad de generar tiempos de espera para comunicación a periféricos o memorias de respuesta lenta.

- Un puerto serie para interfaz directa a "codecs" (codificador-decodificador).

- Entrada de sincronización para sincronía en configuraciones de múltiples procesadores.

- Interfaz de memoria de datos global.

- Compatibilidad de códigos fuente del TMS32010.

- Concurrencia con DMA usando una operación de espera extendida.

- Instrucciones para realizar filtros, la transformada rápida de Fourier y aritmética de precisión extendida.

- Generador de reloj interno.

- Suministro de potencia de 5 volts.

## 1.3 Arquitectura

La destacada funcionalidad del TMS320C25 (TMS) para el procesamiento digital de señales (DSP) se debe a su arquitectura tipo Harvard, que maximiza el procesamiento mediante dos estructuras de buses de memoria separadas (memorias de programa y datos) para incrementar la velocidad de ejecución, contando con instrucciones que realizan la transferencia de datos entre ambos espacios.

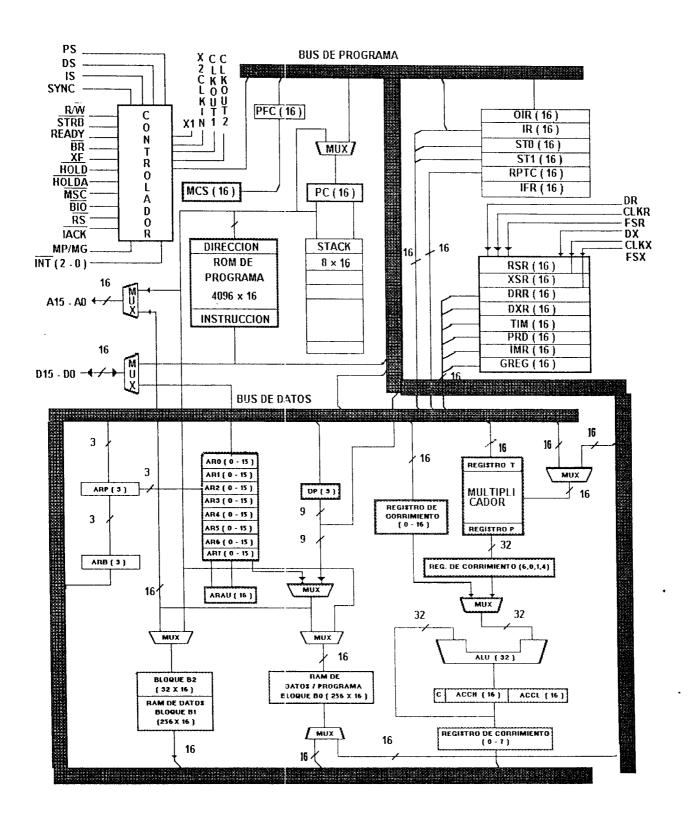

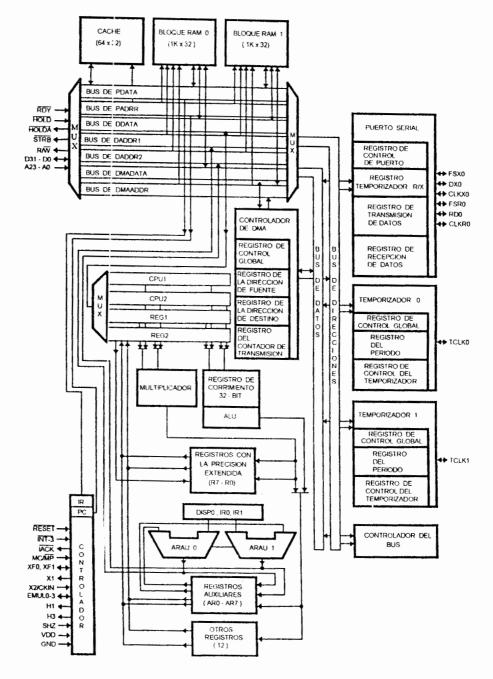

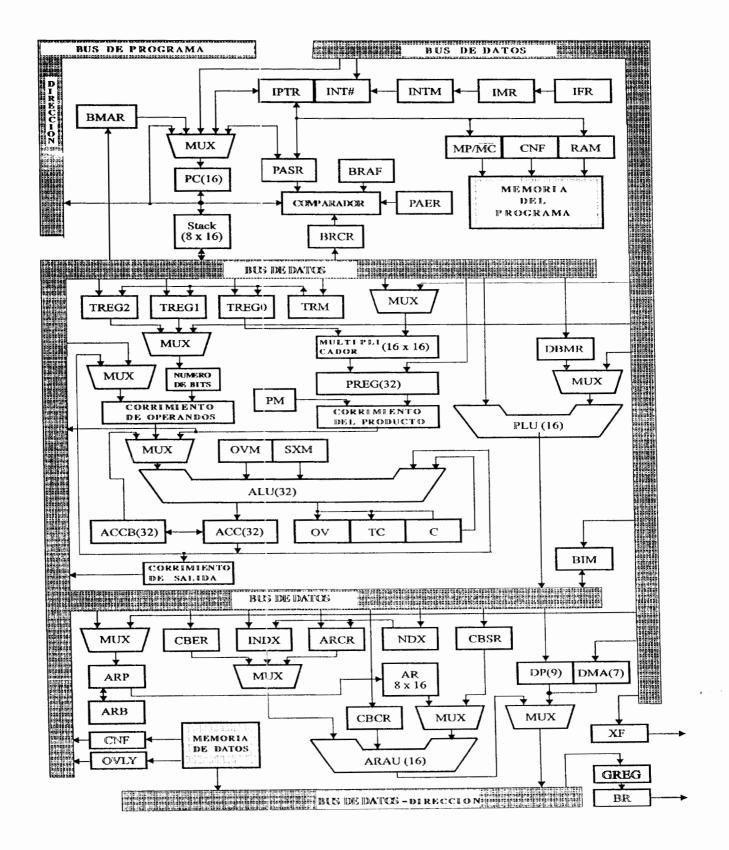

Figura 1.1. Arquitectura del TMS325C25

Externamente, las memorias de programa y datos son multiplexadas sobre el mismo bus para maximizar el intervalo de direccionamiento entre dichos espacios, mientras se minimizan los pines del dispositivo.

La flexibilidad en el diseño del sistema se incrementa con tres bloques de datos internos en RAM (un total de 544 palabras), donde uno de ellos puede ser configurado como memoria programa o memoria dato. El TMS es capaz de direccionar externamente 64k-palabras en un espacio de memoria dato para facilitar la realización de algoritmos para DSP.

La memoria interna ROM mascarable de 4k-palabras puede ser usada para reducir el costo de sistemas. Los programas de 4k-palabras pueden ser mascarables en la memoria ROM interna y, de esta forma, ejecutados a alta velocidad desde este espacio de memoria. Externamente el espacio de memoria de programa direccionable es de 64k-palabras.

El TMS funciona con una aritmética en modo dos complemento, empleando una ALU y un acumulador de 32 bits. La ALU es una unidad aritmética de propósito general que opera con palabras de 16 bits provenientes de la RAM de datos, o derivadas de instrucciones inmediatas, o por el empleo del registro resultado (producto) del multiplicador de 32 bits. La ALU puede efectuar operaciones booleanas. El acumulador almacena los resultados de la ALU y a su vez es una segunda entrada a la ALU. La longitud total del acumulador es de 32 bits, la cual está dividida en dos partes, una alta (bits 31 al 16) y otra baja (bits 15 al 0), y para el manejo de datos se tiene instrucciones de almacenamiento para cada una de las partes (alta y baja) del acumulador.

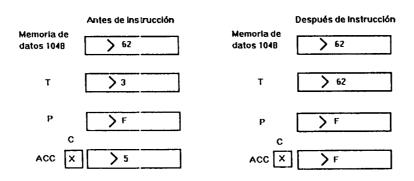

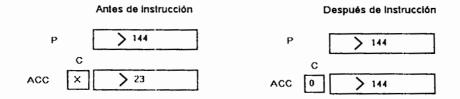

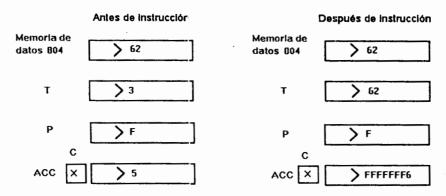

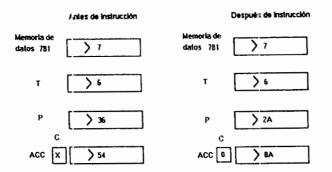

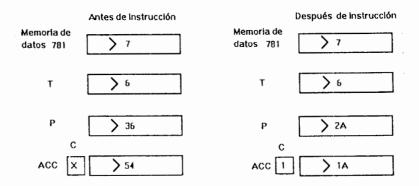

El multiplicador realiza operaciones de 16 × 16 bits en modo dos complemento con un resultado de 32 bits en un solo ciclo de instrucción. El multiplicador está compuesto de tres elementos: el registro T (de 16 bits) para almacenar temporalmente el multiplicado, el registro P (de 32 bits) para almacenar el producto, y un arreglo multiplicador. Los valores del multiplicador provienen de la memoria dato, memoria programa (cuando se emplean las instrucciones MAC/MACD), o son derivados de una instrucción inmediata MPYK (multiplicación inmediata). La rapidez del multiplicador integrado permite la ejecución de operaciones fundamentales en el DSP como la convolución, correlación y filtrado.

El registro de corrimiento del TMS tiene una entrada de 16 bits y está conectado al bus de datos, mientras que su salida de 32 bits está conectada a la ALU. Este registro proporciona corrimientos a la izquierda de 0 a 16 bits sobre los datos de entrada y son programados mediante las instrucciones por medio del "shift" (corrimiento). Adicionalmente, se tiene la capacidad de que el procesador funcione con escalamiento numérico, extracción de bits, aritmética extendida y prevención de sobreflujo.

La interfaz local de la memoria del TMS consta de un bus de datos paralelo de 16 bits (D15-D0), un bus de direcciones de 16 bits (A15-A0), tres pines para selección de memoria dato/programa o espacio de entrada/salida (/DS, /PS e /IS) y varias señales de control del sistema. La señal R/w controla el sentido de transferencia del dato, y la señal /STRB provee un tiempo válido para la transferencia de información. Cuando se emplean las memorias ROM, RAM internas o memoria de programa externa de alta velocidad, el TMS ejecuta instrucciones a la máxima velocidad sin tiempos de espera. De otro modo, se utiliza la señal READY para generar tiempos de espera para comunicarse con memorias externas lentas.

El stack por hardware de ocho niveles almacena el contenido del contador de programa durante interrupciones y llamadas de subrutinas. Las instrucciones PUSH y POP permiten salvar y recuperar información contenida en el stack. Las interrupciones empleadas en el dispositivo son mascarables.

Las operaciones de control son proporcionadas en el TMS por un timer interno de 16 bits mapeado en memoria, un contador de repetición, tres interrupciones externas mascarables, y una interrupción interna generada por el puerto serie o el timer.

Un puerto serie interno full-duplex provee comunicación directa con dispositivos seriales como codecs, convertidores seriales A/D, y otros dispositivos seriales. Los dos registros del puerto serial mapeados en la memoria (registros de transmisión/recepción de dato) pueden operar en modo byte (8 bits) o modo word (16 bits). Cada registro tiene una entrada de reloj externa, una entrada de sincronía y registros de corrimiento. La comunicación serial puede ser usada entre procesadores en aplicaciones de multiprocesos.

El TMS para aplicaciones de múltiples procesadores tiene la capacidad de distribuir el espacio global de memoria de dato y de comunicación mediante las señales /BR (requerimiento de bus) y READY. El registro de distribución de la memoria global de dato (GREG) de 8 bits especifica hasta 32k-palabras de memoria dato como memoria global externa. El contenido del registro determina el tamaño del espacio global de memoria. Si la instrucción actual direcciona un operando dentro de este espacio, /BR se activa para requerir el control del bus. La extensión del ciclo de lectura/escritura de memoria se controla con la línea READY.

El procesador TMS soporta acceso directo a memoria (DMA) para su memoria externa dato/programa, para lo cual utiliza las señales /HOLD y /HOLDA. Otro procesador puede tomar por completo el control de la memoria externa del TMS por medio de la señal /HOLD (activa baja). Esta señal provoca que el TMS mantenga en estado de alta impedancia sus líneas de direccionamiento, datos y control. Sin embargo, de manera concurrente al modo DMA, el TMS continuará ejecutando su programa si éste opera con la RAM y ROM internas.

# 1.4 Diagrama de bloques funcional

La arquitectura del TMS320C25 está construida alrededor de dos buses: de programa y de datos. El bus de programa proporciona el código de instrucción y operandos inmediatos de la memoria de programa. El bus de datos interconecta varios elementos, como la unidad aritmética lógica central (CALU) y los registros auxiliares a los datos RAM. Tanto el bus de programa como el de datos pueden transferir datos de memoria dato RAM interna y de la memoria programa interna o externa al multiplicador en un ciclo de instrucción para realizar operaciones de multiplicación/acumulación.

El TMS320C25 tiene un alto grado de paralelismo, es decir, que mientras está operando sobre la CALU puede realizar operaciones aritméticas en la unidad aritmética de registros auxiliares (ARAU). Tal paralelismo resulta en un poderoso conjunto de operaciones aritméticas, lógicas y manipulación de bits que se ejecutan en un solo ciclo de máquina.

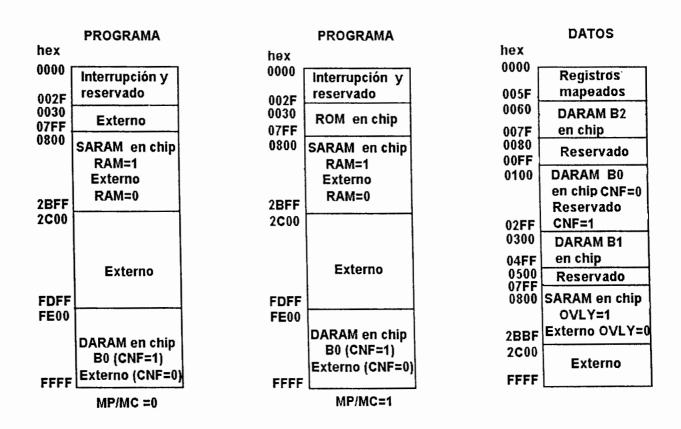

# 1.5 Organización de la memoria

El TMS320C25 posee un total de 544 palabras de 16 bits de RAM interna, de las cuales 288 palabras son siempre memoria de dato y las 256 restantes pueden ser configuradas como memoria de programa o dato. También provee 4k-palabras mascarables en programa ROM.

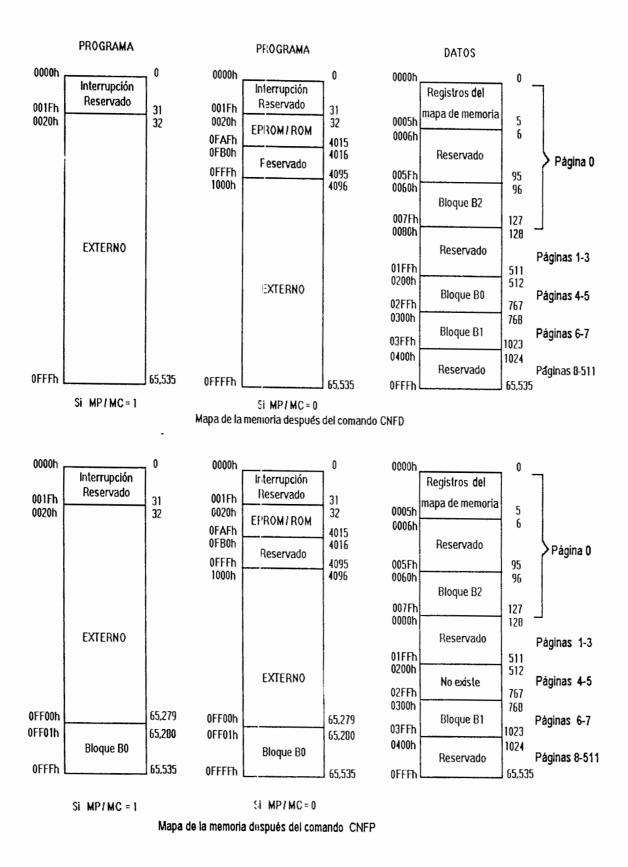

Las 544 palabras de RAM interna se dividen en tres bloques separados: B0, B1 y B2. El bloque B0 de 256 palabras es configurado como memoria de programa o dato por medio de instrucciones (CNFP o CNFD). Como memoria de dato dato, B0 reside en las páginas 4 y 5 del mapa de memoria de datos, y como memoria de programa de > FF00 a > FFFF, pudiéndose utilizar la instrucción BLKP (movimiento de bloque de memoria de programa a memoria de dato) para cargar la información del programa al bloque B0 cuando éste es configurado como RAM de datos. Las 288 palabras (bloques B1 y B2) siempre son configuradas como memoria de dato. B1 está localizado en las páginas 6 y 7, y abarca 256 localidades, mientras que B2 está en las 32 localidades superiores de la página 0.

La memoria de dato interna y las localidades reservadas para registros son mapeadas dentro de las primeras 1024 palabras del espacio total de memoria de dato (configuración con la instrucción CNFD).

Las 4k-palabras de ROM interna pueden ser un programa mascarable. Esta área de memoria permite la ejecución de programas a máxima velocidad sin necesidad de memorias externas veloces para almacenar el programa. El mapeo de estas 4k-palabras se realiza por medio del pin de selección MP/MC (microprocesador/microcomputadora). Manteniendo MP/MC en alto, el TMS mapea este bloque de memoria como externo, y MP//MC en bajo lo mapea en ROM interna (Ver mapa de memoria en la figura 1.2).

El TMS provee tres espacios de direccionamiento para memoria de programa, memoria de dato e I/O. Estos espacios son distinguidos externamente por medio de las señales /PS, /DS e /IS (programa, dato e I/O). Las señales /PS, /DS, /IS y /STRB son activadas sólo cuando un espacio externo de memoria se direcciona. Durante un direccionamiento interno, estas señales permanecen en estado inactivo alto para prevenir conflictos de direccionamiento cuando el B0 es configurado como memoria de programa.

## Registros mapeados en memoria

En el mapa de memoria, los registros pueden ser accesados de igual manera como un dato localizado en la memoria de dato, excepto el movimiento de bloques que usa la instrucción BLKD, la cual no puede ser ejecutada en las localidades de memoria de los registros.

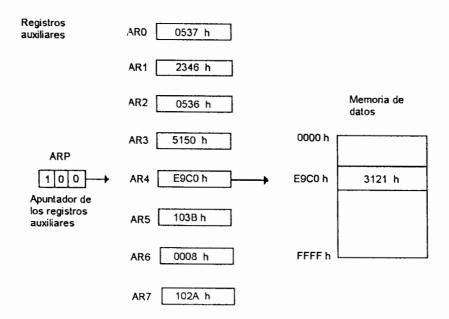

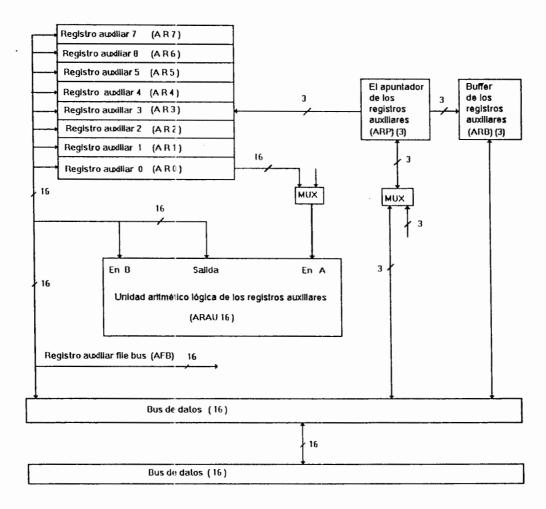

## Registros auxiliares

El TMS posee 8 registros auxiliares seleccionados por un apuntador de registros auxiliares de 3 bits (ARP), cargándose con los valores de 0 a 7 para designar desde AR0 a AR7, respectivamente. Dichos registros pueden ser utilizados para direccionamiento indirecto de la memoria de dato, o almacenamiento temporal de datos, como se observa en las figuras 1.3 y 1.4. Además, permiten posicionarse en una dirección de memoria de dato de un operando de una instrucción.

Figura 1.2. Mapa de la memoria

Figura 1.3. Registros en la memoria

Figura 1.4. Registros auxiliares ΛR0-AR7

Los registros auxiliares están conectados a una unidad aritmética de registros auxiliares (ARAU). Esta unidad puede autoindexar el registro actual, mientras la localización del dato está siendo direccionada. Como resultado, la CALU no accesa a tablas de información para manipuleo de direcciones, de este modo realiza libremente otras operaciones.

ARAU efectúa las siguientes operaciones:

```

AR(ARP) + AR0 \Longrightarrow AR(ARP).

AR(ARP) - AR0 \Longrightarrow AR(ARP).

AR(ARP) + 1 \Longrightarrow AR(ARP).

AR(ARP) - 1 \Longrightarrow AR(ARP).

AR(ARP) \Longrightarrow AR(ARP) \land AR(ARP) \Rightarrow AR(ARP) \Rightarrow

```

Aunque la unidad ARAU es útil para la manipulación de direccionamiento en paralelo con otras operaciones, ésta puede servir como una unidad aritmética adicional de propósito general, ya que los registros auxiliares pueden comunicarse directamente con la memoria de datos. La unidad ARAU utiliza aritmética no signada de 16 bits, mientras que con la unidad CALU, aritmética modo dos complemento de 32 bits.

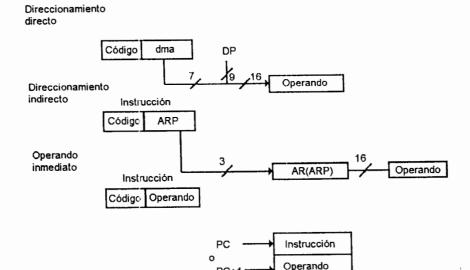

#### Modos de direccionamiento de memoria

El TMS puede direccionar un total de 64k-palabras de memoria de programa y 64k-palabras de memoria de datos, como puede observarse en la figura 1.5. Los 16 bits del bus de direcciones (DAB) direcciona la memoria de datos de dos formas:

- 1. Direccionamiento directo de bus usando modo de direccionamiento directo.

- 2. Por los registros auxiliares usando el modo de direccionamiento indirecto.

Los operandos también son direccionados por el contenido del contador de programa en el modo de direccionamiento inmediato.

#### a) Modo de direccionamiento directo

Utiliza 9 bits del apuntador de página DP, el cual puede apuntar 512 páginas de 128 palabras cada una. El dato de memoria direccionado es especificado por los 7 bits menos significativos de la instrucción para apuntar la palabra deseada dentro de la página.

#### b) Modo de direccionamiento indirecto

Los 16 bits de la dirección son seleccionados por el registro auxiliar en uso, direccionando el dato de memoria a través del bus de registro auxiliar file (AFB).

Cuando un operando inmediato es empleado, la palabra de la instrucción contiene el operando; en el caso de operandos inmediatos de 16 bits, éstos constituyen la siguiente palabra del código de instrucción.

Figura 1.5. Modos de direccionamiento

#### Movimiento de memoria a memoria

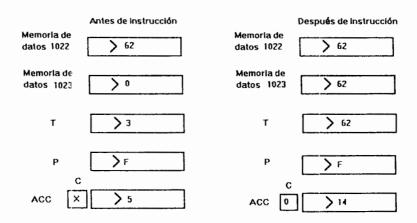

Las instrucciones que permiten el movimiento de datos y programa determinan que se utilice eficazmente la configuración de la RAM interna. La instrucción BLKD mueve un bloque dentro de la memoria dato y BLKP un bloque de programa a memoria de datos. Para el empleo eficiente de estas instrucciones, se utilizan las de repetición RPT y RPTK.

La instrucción DMOV copia una palabra de la dirección actual en la memoria de dato en RAM interna a la próxima localización alta, mientras el dato de la dirección de localización está siendo operado en el mismo ciclo por CALU. Una operación de la ARAU también puede ejecutarse en el mismo ciclo cuando se usa el modo de direccionamiento indirecto.

La función de DMOV es útil en los algoritmos donde se utilizan operadores de retardo  $Z^{-1}$ , tales como convolución y filtrado digital donde el dato es pasado a través de una ventana de tiempo. La función de movimiento de dato puede ser utilizada dentro de los bloques B0, B1 y B2. Las instrucciones TBLR y TBLW (tabla de lectura y escritura) transfieren palabras entre el espacio de programa y de dato.

#### Unidad aritmética lógica central (CALU)

Una unidad aritmética lógica central contiene un registro de corrimiento de 16 bits, un multiplicador paralelo de 16 × 16 bits, una unidad aritmética lógica (ALU) de 32 bits, un acumulador de 32 bits (ACC), el cual está dividido en parte alta ACCH y parte baja ACCL, corrimientos de salida para el acumulador y el multiplicador. Las instrucciones SFL y SFR indican los corrimientos a la izquierda y derecha respectivamente.

Pasos en la ejecución de una instrucción típica en la CALU:

- 1) El dato se busca RAM a través del bus de datos.

- 2) El dato se pasa a través del registro de corrimiento y en la CALU se ejecuta la operación.

- 3) El resultado es movido dentro del acumulador.

Una entrada a la ALU es siempre dada por el acumulador y la otra puede ser transferida del registro producto (PR) del multiplicador o del registro de corrimiento que es cargado de la memoria dato. Después de ejecutar la operación aritmética o lógica, la ALU almacena el resultado en el acumulador.

El TMS soporta operaciones de punto flotante requeridas para grandes rangos dinámicos. La instrucción NORM (normalizar) es utilizada para normalizar el punto fijo del número en el acumulador por ejecución de corrimientos a la izquierda. La instrucción LACT desnormaliza un número de punto flotante por corrimiento aritmético a la izquierda de la mantisa a través de la entrada del registro de corrimiento.

El modo de saturación de sobreflujo en el acumulador puede ser programado a través de las instrucciones SOVM y ROVM. Cuando el acumulador está en modo de saturación de sobreflujo y un sobreflujo ocurre, la bandera de sobreflujo es fijada y el acumulador es cargado con cada uno de los números más positivos o negativos, dependiendo de la dirección de sobreflujo (> 7FFFFFFFF para positivo, y > 80000000 para negativo).

Se pueden implantar una variedad de instrucciones de salto a una dirección específica dependiendo del estado de la ALU y del acumulador. El acumulador tiene asociado un acarreo (carry), el cual puede ser puesto en uno (set) o cero (reset), según las operaciones que se realizan. También existen instrucciones para corrimientos y rotamientos del acumulador a la izquierda o a la derecha.

#### Registro de corrimiento

Puede producir corrimientos de 0 a 16 bits a un dato de entrada según sea programado en la instrucción. Los bits menos significativos se llenan de ceros y los más significativos pueden ser llenados con ceros o signo extendido, dependiendo del estado programado en el modo de signo extendido SXM.

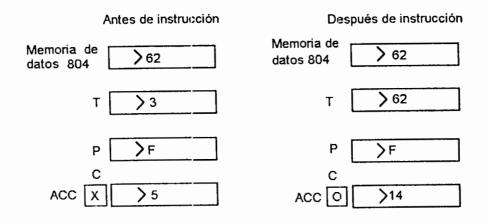

#### Multiplicador, registros T y P

El TMS utiliza un hardware capaz de efectuar multiplicaciones de 16×16 bits en un ciclo de máquina. Todas las instrucciones de multiplicación, excepto MPYU (multiplicación no signada), realizan operaciones de multiplicación signada en el multiplicador. Es decir, que dos números pueden ser multiplicados como números en modo dos complemento y el resultado es un número de 32 bits complementado a dos. Los registros asociados a la multiplicación son:

- TR: registro temporal de 16 bits que mantiene uno de los operandos por multiplicar.

- PR: registro producto de 32 bits que mantiene el producto.

La salida del registro producto puede ser corrida a la izquierda 1 o 4 bits, esto es útil para la implantación de aritmética fraccionaria o justificación de productos fraccionales. La salida PR también puede ser corrida a la derecha en 6 bits, lo cual posibilita la ejecución de 128 multiplicaciones/acumulación sucesivas sin sobreflujo. El registro T normalmente es cargado con la instrucción LT, la cual le provee uno de los operandos (del bus de datos), y la instrucción MPY (multiplicación) proporciona el segundo operando también del bus de

datos. Una multiplicación también puede ser ejecutada con un operando inmediato, con la instrucción MPYK. En los dos casos, el producto es obtenido cada dos ciclos.

Las instrucciones de multiplicación/acumulación (MAC y MACD) emplean totalmente el ancho de cálculo de la multiplicación, lo cual permite que ambos operandos sean procesados simultáneamente.

Las instrucciones SQRA (cuadrado/suma) y SQRS (cuadrado/resta) pasan el mismo valor a ambas entradas de la multiplicación para elevar al cuadrado un valor de la memoria dato.

La instrucción MPYU permite multiplicaciones no signadas que facilitan la precisión de operaciones aritméticas.

Hay disponibles cuatro modos de corrimiento a través del registro producto (PR), los cuales son útiles cuando se ejecutan operaciones de multiplicación/acumulación, aritmética fraccional o justificación fraccional de productos. El registro PM ocupa 2 bits en el registro de estado ST1, que especifica el modo del producto (PM), como se indica en la tabla 1.1.

| PM | PM Modo de corrimiento                |

|----|---------------------------------------|

| 00 | No existe corrimiento.                |

| 01 | Corrimiento de 1 bit a la izquierda.  |

| 10 | Corrimiento de 4 bits a la izquierda. |

| 11 | Corrimiento de 6 bits a la derecha.   |

Tabla 1.1. Registro PM modo de corrimiento

## 1.6 Sistema de control

Está dado por el contador de programa, el stack, la señal de reset externo, las interrupciones, los registros de estado, el timer interno y el contador de repetición.

## El contador de programa y el stack

El contador de programa (PC) consta de 16 bits, lo que permite direccionar hasta 64kdirecciones de memoria programa externas o internas en la búsqueda de las instrucciones. El stack consta de 8 localidades de 16 bits para almacenar el PC durante las interrupciones o las transferencias a subrutinas.

El PC direcciona la memoria programa, vía el bus de dirección de programa (PAB). A través del PAB, se busca una instrucción de la memoria programa y se carga en el registro de instrucción (IR). Cuando el IR ha sido cargado, el PC está listo para iniciar un nuevo ciclo de búsqueda. El PC puede direccionar la RAM interna del bloque B0 cuando éste ha sido configurado como memoria de programa o la ROM interna del TMS. El PC también direcciona la memoria de programa cuando es memoria externa a través del bus externo de direcciones A15-A0 y el bus externo de datos D15-D0. Al inicio del nuevo ciclo de búsqueda,

el PC es cargado con PC+1 o con una dirección de salto. En el caso de no tomar el salto, el PC es incrementado una vez más desde la localización de la instrucción de salto.

También el TMS tiene una característica que le permite ejecutar en el próximo ciclo simple N+1 veces una instrucción, donde N es definido por la carga de 8 bits en el contador de repeticiones RPTC con la instrucción RPTK.

El stack es accesado a través de las instrucciones PUSH y POP. Las instrucciones adicionales de PSHD y POPD permiten utilizar el stack para el almacenamiento temporal de la memoria de datos.

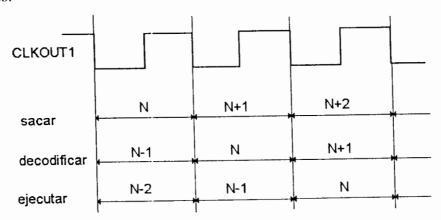

#### Operación de pipeline o encauzamiento

Una instrucción de pipeline consiste en una secuencia de operaciones externas de bus que ocurren durante la ejecución interna de la instrucción. El pipeline de prebúsqueda-decodificación-ejecución es esencialmente transparente al usuario, excepto en algunos casos donde el pipeline debe ser interrumpido con instrucciones, tales como saltos dentro del programa (B, BNZ, etc.). En la operación de pipeline, las operaciones de prebúsqueda, decodificación y ejecución son independientes. Durante algún ciclo dado, dos o tres diferentes instrucciones pueden ser activadas cada una a un estado distinto de realización.

Los diferentes niveles en pipeline no necesariamente afectan la velocidad de ejecución, pero sí la secuencia búsqueda/decodificación. Más instrucciones son ejecutadas en igual número de ciclos.

Figura 1.6. Operación de pipeline a tres niveles

En los tres niveles de pipeline, un contador de prebúsqueda contiene la dirección de la próxima instrucción que será prebuscada. Una vez que una instrucción ha sido prebuscada, entonces se carga en un registro de instrucción (IR), a menos que IR contenga la instrucción en ejecución, en cuyo caso la instrucción prebuscada se carga en un registro de instrucción a la cola (QIR). El contador de prebúsqueda es incrementado y después que la instrucción actual completa la ejecución, la instrucción en QIR se carga en IR para ser ejecutada.

El PC contiene la dirección de la próxima instrucción que va a ejecutarse sin ser usada directamente en las operaciones de búsqueda, pero sirve como un apuntador de referencia para la posición actual dentro del programa. El PC es incrementado cada vez que una instrucción se ejecuta. Cuando ocurre una interrupción o una llamada de subrutina, el

contenido del PC se guarda en el stack para preservarlo al regreso de una interrupción o subrutina.

La prebúsqueda, decodificación y ejecución de la operación de pipeline son independientes, lo cual permite la ejecución de operaciones traslapadas. Durante algún ciclo, tres instrucciones distintas pueden ser activadas cada una a diferente estado de realización.

La operación básica de pipeline es de 3.25 ciclos de duración, donde la secuencia en un dispositivo sobre algún ciclo dado será la siguiente: buscar una tercera instrucción, decodifica una segunda y ejecutar una primera. Si la instrucción se busca en la RAM interna, el pipeline es acortado a 2.5 ciclos, dado que TMS puede buscar la instrucción en la mitad del ciclo, contrario a lo que ocurre cuando se busca en la ROM externa, que requiere de un ciclo completo para la búsqueda.

Cuando existen estados de espera, sólo retardan directamente la operación de pipeline. Cada estado de espera, insertado durante la operación de búsqueda, agrega más ciclos de máquina en la ejecución de pipeline de la instrucción.

#### Acceso externo de memoria de programa o datos

La visibilidad de pipeline requiere el monitoreo de señales /MSC, /STRB, /PS y /DS. La señal /MSC indicada en la caída de CLKUOT2, ya sea o no el ciclo de una nueva instrucción de búsqueda, es decir, que /MSC activa señala la terminación de una instrucción y la adquisición de otra. /PS indica que el bus de datos está siendo utilizado para la búsqueda de una instrucción (aunque no necesariamente la activación de esta señal significa la búsqueda de una instrucción). El monitoreo de la búsqueda de memoria de dato debe hacerse seleccionando conjuntamente /DS y /STRB.

## Reset (/RS)

Es una interrupción externa no mascarable, con la más alta prioridad sobre las demás interrupciones. Puede ser usada en cualquier instante y es aplicada típicamente en el encendido cuando los estados de máquina son alcatorios.

La señal /RS causa que el TMS termine la ejecución y fuerce al contador de programa a ir a la dirección cero, lo cual afecta varios registros y los bits de estado. Para la correcta operación del sistema, la señal de reset debe ser insertada baja, por lo menos tres ciclos de reloj. El bus de datos es puesto en alta impedancia y las señales de control se van a alto mientras dura el reset.

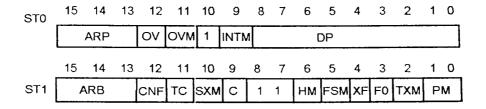

#### Registros de estado

Los registros de estado ST0 y ST1 contienen el estado de varias condiciones y modos de operación del TMS, figura 1.7. Los registros de estado pueden ser almacenados dentro de la memoria de dato y cargados de memoria dato, lo cual permite que el estado de la máquina sea salvado y restaurado para interrupciones y subrutinas. Todos los bits de estado pueden ser escritos y leídos con las instrucciones LST/LST1 y SST/SST1 (excepto INTM, que se carga con LST).

Figura 1.7. Registros de estado

#### Donde:

- ARB: buffer apuntador de registros auxiliares.

- ARP: apuntador de registros auxiliares.

- C: bit de carry.

- CNF: bit de control de configuración de RAM interna.

- DP: apuntador de página de memoria dato.

- FO: bit de formato para cada puerto serie.

- FSM: bit de modo de estructura de sincronización.

- IIM: bit de modo hold.

- INTM: bit de modo de interrupción, 0 = habilitado, 1 = deshabilitado.

- OV: bit de bandera de sobreflujo.

- OVM: bit de modo de sobreflujo.

- PM: modo de corrimiento de producto.

- SXM: bit de modo de signo extendido.

- TC: bandera de control de prueba de bit.

- TMX: bit de modo de transmisión.

- XF: bit de estado del pin XF.

## Operación del timer

El TMS posec un registro timer (TIM) y un registro período (PRD) de 16 bits. El timer cuenta descendentemente en la caída de CLKOUT1. Los registros TIM y PRD son fijados a su máximo valor > FFFF en el reset. Una interrupción del timer (TINT) es generada cada vez que el TIM llega a cero, el TIM es recargado con el valor de PRD en el próximo ciclo. Esta característica es útil para operaciones de control y sincronización de muestreos o escritura de periféricos.

Si el timer no es utilizado, TINT debe ser mascarable o todas las interrupciones deben ser deshabilitadas por la instrucción DINT.

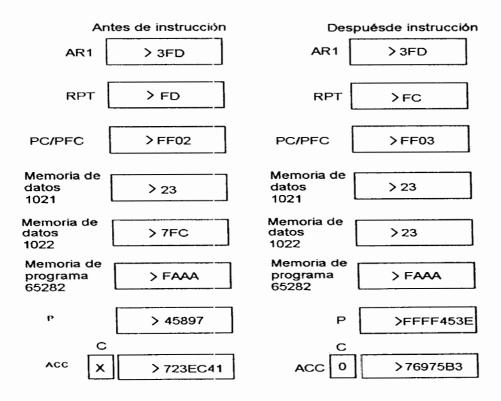

#### Contador de repetición (RPTC)

Es de 8 bits y cuando es cargado con un número N causa que la siguiente instrucción sea ejecutada N+1 veces. El RPTC puede ser cargado con un número de 0 a 255 mediante las instrucciones RPT o RPTK. Se utiliza en las instrucciones de multiplicación/acumulación, movimiento de bloques, transferencias de 1/O y tablas de lectura/escritura.

#### Memoria externa e interfaz I/O

La interfaz local de memoria consta de los siguientes elementos:

- Bus de datos paralelos de 16 bit D15-D0.

- Bus de direcciones A15-A0.

- Señales de selección de espacio programa, dato e I/O, /PS, /DS y /IS, respectivamente.

- Varias señales del sistema de control.

La señal de lectura/escritura R/W provee la dirección de transferencia y la señal /STRB el tiempo de transferencia de control.

El microcontrolador tiene 16 puertos de entrada y 16 de salida, con 16 bits para datos de entrada o salida. Para entrada o salida se utilizan de manera respectiva las instrucciones de IN y OUT, que típicamente ocupan dos ciclos; sin embargo, con el contador de repeticiones la operación se convierte en un ciclo simple.

#### Combinación de memoria

La secuencia exacta de las operaciones ejecutadas de una instrucción depende de las áreas de memoria donde la instrucción y los operandos son localizados. Las seis posibles combinaciones de programa y dato, dada la información, pueden ser localizadas en memoria RAM interna, memoria ROM externa o interna:

- Pl/DI: programa interno RAM/dato interno.

- PI/DE: programa interno RAM/dato externo.

- PE/DI: programa externo/dato interno.

- PE/DE: programa externo/dato externo.

- PR/DI: programa interno ROM/dato interno.

- PR/DE: programa interno ROM/dato externo.

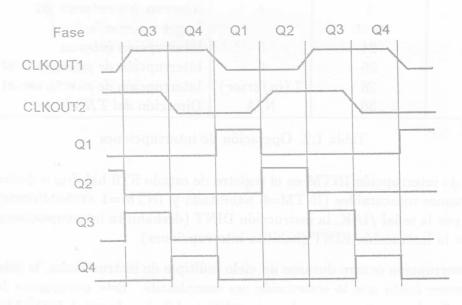

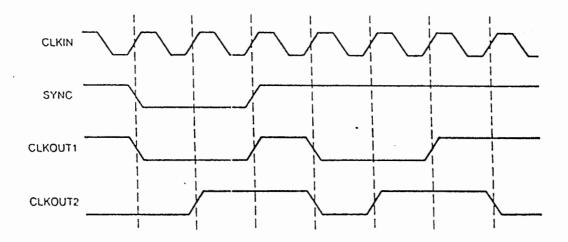

## Relaciones de tiempo del reloj interno

El cristal o la fuente de frecuencia externa es dividida para producir cuatro fases de reloj, definidas como CLKOUT1 y CLKOUT2.

#### Interrupciones

El TMS tiene tres interrupciones externas mascarables (/INT2, /INT1, /INT0), disponibles para dispositivos externos que interrumpan al microprocesador. Dos interrupciones internas generadas por el puerto serie (RINT y XINT), una por el timer (TINT) y otra más por software a través de la instrucción TRAP, aunque esta última no tiene prioridad.

Figura 1.8. Reloj interno

#### Operación de las interrupciones

Cada dirección de interrupción ha sido espaciada cada dos localidades, de tal modo que se puedan acomodar instrucciones para realizar saltos cuando así se desea, tabla 1.2. Cuando una interrupción ocurre, ésta es almacenada en un registro de bandera de interrupción de 6 bits (IFR). Este registro es fijado por el uso de interrupciones externas /INT(2-0) y las interrupciones RINT, XINT y TINT. Cada interrupción es almacenada en el registro IFR hasta que es identificada y automáticamente borrada por el reconocimiento de interrupciones (/IACK) o el reset (/RS). /RS no es almacenado en el registro IFR. Ninguna instrucción puede leerse o escribirse en IFR.

El TMS tiene un mapa de memoria para registro de interrupciones mascarables (IMR) para mascarar las interrupciones internas y externas (figura 1.9).

El IMR, que habilita la correspondiente interrupción colocando un cero, es accesible para operaciones de lectura y escritura, excepto cuando se usa BLKD. IMR no es afectado por reset.

|     | 15 | 14 | 13 | 12  | 11   | 10  | 9 | 8 | 7               | 6 | 5   | 4    | 3    | 2    | 1    | 0    |

|-----|----|----|----|-----|------|-----|---|---|-----------------|---|-----|------|------|------|------|------|

| IMR |    |    |    | RES | SERV | ADO |   |   | WESTERN MODELLA |   | INT | RINT | TINT | INT2 | INT1 | INTO |

Figura 1.9. Mapa de memoria para registro de interrupciones

| Nombre            | Localización  | Prioridad    | Función                       |

|-------------------|---------------|--------------|-------------------------------|

| de interrupción   | en la memoria |              |                               |

| RS                | 0             | 1 (suprema)  | Reset externo                 |

| $\overline{INT0}$ | 2             | 2            | Interrupción $externa$ #0     |

| $\overline{INT1}$ | 4             | 3            | Interrupción externa #1       |

| $\overline{INT2}$ | 6             | 4            | Interrupción externa #2       |

|                   | 8-23          |              | Lugar reservado               |

| LIML              | 24            | 5            | Interrupción interna          |

| RINT              | 26            | 6            | Interrupción de puerto serial |

| XINT              | 28            | 7 (inferior) | Interrupción de puerto serial |

| TRAP              | 30            | N/A          | Dirección del TRAP            |

Tabla 1.2. Operación de interrupciones

El modo de interrupción INTM en el registro de estado STO habilita o deshabilita todas las interrupciones mascarables (INTM=0 habilitado y INTM=1 deshabilitado). INTM es fijado a uno por la señal /IAK, la instrucción DINT (deshabilita interrupciones) y por reset, y en cero por la instrucción EINT (habilita interrupciones).

Si una interrupción ocurre durante un ciclo múltiple de instrucciones, la interrupción no puede procesarse hasta que la instrucción sea completada. Este mecanismo de protección también es aplicado a instrucciones de ciclo múltiple debido a la señal de READY. Tampoco se permite que se procesen interrupciones cuando una instrucción está siendo repetida por medio de RPTK, la interrupción es almacenada en el registro IFR hasta que el ciclo de repetición se termine, después la interrupción es procesada. Las interrupciones no pueden ser procesadas entre la instrucción EINT y la próxima instrucción en la secuencia del programa. También una interrupción no es reconocida cuando el /HOLD está activado.

## Multiprocesamiento y acceso directo de memoria (DMA)

El TMS puede ser configurado para satisfacer amplios rangos de requerimiento de sistemas. Algunas configuraciones son:

- Sistema estándar (proceso simple).

- Multiprocesamiento con dispositivos en paralelo.

- Multiprocesos huésped/esclavo con espacio de memoria dato compartida.

- Proceso a periféricos interfaceados mediante señales de control de procesos para otros dispositivos.

Estas configuraciones son posibles con la señal externa de entrada /SYNC, la interfaz de memoria global y la implantación de la función hold con los pines de /HOLD y /HOLDA.

#### Sincronización

Esta señal externa de entrada puede ser utilizada con gran facilidad entre procesos, lo cual provoca que cada TMS en el sistema se sincronice con su reloj interno y el proceso corra

amarrado a los pasos de la operación. La transición negativa de /SYNC fija a cada proceso a un cuarto de fase interna (Q1). Esta transición debe ocurrir sincronizada con la bajada del reloj CLKIN. En el TMS hay dos ciclos de retardo CLKIN que permiten que la señal /SYNC vaya abajo, por lo tanto, ocurre la sincronización Q1.

Normalmente /SYNC es aplicado mientras /RS está activado para evitar situaciones no predecibles del procesador.

Figura 1.10. Sincronización

#### Memoria global

Para aplicaciones de multiprocesamiento, el TMS tiene la capacidad de localizar un espacio de memoria global de datos y comunicarse con éste a través de /BR (requerimiento de bus) y la señal de control READY.

La memoria global es compartida por más de un procesador, por lo tanto, su acceso debe ser arbitrado. Cuando se utiliza memoria global, el espacio de direccionamiento del procesador es dividido en secciones: local y global. La sección local es usada por el procesador para ejecutar funciones individuales y la sección global para comunicarse con otros procesadores.

El registro de mapeo de memoria global (GREG) especifica la parte de memoria de datos del TMS como memoria global externa. GREG es mapeado como memoria de datos en la localización 5, es un registro de 8 bits conectados con los 8 bits menos significativos del bus de datos.

El contenido de GREG determina el tamaño del espacio de memoria global. El valor de GREG y el correspondiente espacio se indican en la tabla 1.3.

Cuando un dato es direccionado directa o indirectamente de memoria global (definido por GREG), entonces la señal /BR es activada bajo mediante la señal /DS para indicar al procesador que se desea accesar de memoria global.

La lógica externa arbitra el control de memoria global con la señal READY.

| Valor de GREG | Memorie     | ı local  | Me     | moria global |          |

|---------------|-------------|----------|--------|--------------|----------|

|               | Rango       | Palabras | Rango  |              | Palabras |

| 000000xx      | 0h - 0FFFFh | 65,536   |        |              | 0        |

| 10000000      | 0h - 07FFFh | 32,768   | 08000h | -0FFFFh      | 32,768   |

| 11000000      | 0h - 0BFFFh | 49,152   | 0C000h | -0FFFFh      | 16,384   |

| 11100000      | 0h - 0DFFFh | 57,344   | 0E000h | -0FFFFh      | 8,192    |

| 11110000      | 0h - 0EFFFh | 61,440   | 0F000h | -0FFFFh      | 4,096    |

| 11111000      | 0h - 0F7FFh | 63,488   | 0F800h | -0FFFFh      | 2,048    |

| 11111100      | 0h - 0FBFFh | 64,512   | 0FC00h | -0FFFFh      | 1,024    |

| 11111110      | 0h - 07DFFh | 65,024   | 0FE00h | -0FFFFh      | 512      |

| 11111111      | 0h - 07EFFh | 65,280   | 0FF00h | -0FFFFh      | 256      |

Tabla 1.3. Valor de GREG

# Capítulo 2

# Instrucciones del DSP TMS320C25

El TMS320C25 cuenta con un conjunto de 133 instrucciones, 97 de ellas son ejecutadas en un ciclo simple de instrucción, otras 36 requieren ciclos adicionales, 21 involucran saltos, llamadas de rutinas y retornos (las cuales rompen la ejecución de la operación pipeline), otras siete instrucciones son de dos palabras (instrucciones largas inmediatas). Las ocho restantes (IN, OUT, BLKD, BLKP, TBLR, TBLW, MAC y MACD) soportan transferencia de I/O y de datos entre espacio de memoria, o son utilizadas para operaciones en paralelo en el procesador. Adicionalmente estas ocho instrucciones se convierten en un ciclo simple cuando son utilizadas en conjunto con el contador de repeticiones.

Estas instrucciones utilizan los modos de direccionamiento del TMS. Además explotan el paralelismo del procesador, lo cual permite cálculos complejos que son desarrollados con pocas instrucciones.

Las instrucciones las podemos clasificar de la siguiente manera:

- aritmético-lógicas que trabajan con el acumulador,

- para multiplicación,

- para saltos del programa,

- para comunicación con los circuitos entrada/salida,

- para la modificación de direcciones de registros y

- dirigidas.

De la tabla 2.1 hasta la 2.6 se muestran las instrucciones del DSP, su sintaxis y características.

| SINTAXIS EN ENSAMBLADOR                                                                                   | TÍTULO                                   | DESCRIPCIÓN DE OPERACIONES                               |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------|

| ADD < dma > [, < shift >]                                                                                 | Suma al acumulador<br>con desplazamiento | $(ACC) + [(dma) \times 2^{shift}] \rightarrow ACC$       |

| $\begin{array}{ c c c }\hline ADD < ind > [, < shift > [, < nextARP >]]\\\hline ADDC < dma > \end{array}$ | C                                        | (400) + (1 ) + (0) + 400                                 |

| ADDC < dma >                                                                                              | Suma al acumulador con carry             | $(ACC) + (dma) + (C) \rightarrow ACC$                    |

| ADDC < ind > [, < nextARP >]                                                                              | con carry                                |                                                          |

| ADDH < dma >                                                                                              | Suma a la parte alta del                 | $(ACC) + [(dma) \times 2^{16}] \rightarrow ACC$          |

|                                                                                                           | acumulador                               |                                                          |

| ADDH < ind > [, < nextARP >]                                                                              |                                          |                                                          |

| ADDK < constant >                                                                                         | Suma valor corto in-                     | $(ACC) + 8$ -bit constant $\rightarrow ACC$              |

| ADDC                                                                                                      | mediato al acumulador                    | (100) (1) 100                                            |

| $\mathbf{ADDS} < dma >$                                                                                   | Suma a parte baja del                    | $(ACC) + (dma) \rightarrow ACC$                          |

|                                                                                                           | acum, sin extensión del                  |                                                          |

| ADDS < ind > [, < nextARP >]                                                                              | signo                                    |                                                          |

| ADDT < dma >                                                                                              | Suma al acumulador                       | $(ACC) + [(dma) \times 2^{(Treg)}] \rightarrow ACC$      |

| ADDI ( unu )                                                                                              | con desplazamiento da-                   | $(100) + ((ama) \times 2 \times 3) \rightarrow 100$      |

|                                                                                                           | do por T                                 |                                                          |

| ADDT < ind > [, < nextARP >]                                                                              | do por 1                                 |                                                          |

| ADLK < constant > [, < shift >]                                                                           | Suma constante con                       | $(ACC) + [16-bit constant \times 2^{shift}] \rightarrow$ |

|                                                                                                           | desplazamiento                           | ACC                                                      |

| AND < dma >                                                                                               | AND con el acumulador                    | $(ACC(15-0)).AND.(dma) \rightarrow ACC(15-0)$            |

| AND < ind > [, < nextARP >]                                                                               |                                          | $0 \to ACC(31 - 16)$                                     |

| ANDK < constant > [, < shift >]                                                                           | AND constante con                        | (ACC(30 - 0)).AND.[16-bit constant                       |

|                                                                                                           | acumulador                               | $\times 2^{shift}] \rightarrow ACC(30-0)$                |

|                                                                                                           |                                          | $0 \rightarrow ACC(31 - 0 \text{ unoccupied})$           |

| CMPL                                                                                                      | Complemento al                           | $(\overline{ACC}) \to \overline{ACC}$                    |

|                                                                                                           | acumulador                               |                                                          |

| $\mathbf{LAC} < dma > [, < shift >]$                                                                      | Carga el acumulador                      | $(dma) \times 2^{shift} \to ACC$                         |

|                                                                                                           | con desplazamiento                       |                                                          |

| LAC < ind > [, < shift > [, < nextARP >]]                                                                 |                                          | 166                                                      |

| LACK < constant >                                                                                         | Carga valor inmediato                    | 8-bit constant $\rightarrow ACC$                         |

|                                                                                                           | al acumulador                            | offred 155                                               |

| LACT < dma >                                                                                              | Carga al acumulador                      |                                                          |

|                                                                                                           | con desplazamiento da-                   |                                                          |

| T.A.CIT                                                                                                   | do por T                                 |                                                          |

| LACT < ind > [, < nextARP >]                                                                              | (C                                       | $16-\text{bit constant} \times 2^{shift} \to ACC$        |

| LALK < constant > [, < shift >]                                                                           | Carga valor inmediato                    |                                                          |

|                                                                                                           | largo al acumulador con                  |                                                          |

|                                                                                                           | desplazamiento                           |                                                          |

Tabla 2.1. Instrucciones del DSP TMS320C25 que trabajan con el acumulador

| SINTAXIS EN ENSAMBLADOR                                                                                                                                                                  | TITULO                                                           | DESCRIPCIÓN DE OPERACIONES                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| NORM < ind >                                                                                                                                                                             | Normaliza el contenido del acumulador                            | por ejemplo para transferencia del<br>punto fijo a punto flotante                                                        |

| OR < dma >                                                                                                                                                                               | OR entre contenido de        | $(ACC(15 - 0)).OR.(dma) \rightarrow ACC(15 - 0)$                                                                         |

| OR < ind > [, < nextARP >]                                                                                                                                                               |                                                                  |                                                                                                                          |

| $\mathbf{ORK} < constant > [, < shift >]$                                                                                                                                                | OR entre valor inmedi-<br>ato y acumulador con<br>desplazamiento | (ACC(30 - 0)).OR.[16-bit constant]<br>$\times 2^{shift}] \rightarrow ACC(30 - 0)$                                        |

| ROL                                                                                                                                                                                      | Rotamiento del acumu-<br>lador a la izquierda                    | $(ACC(30-0)) \to ACC(31-1)$ $(C) \to ACC(0)  (ACC(31)) \to C$                                                            |

| ROR                                                                                                                                                                                      | Rotamiento del acumu-<br>lador a la derecha                      | $(C) \to ACC(0), (ACC(31)) \to C$ $(ACC(31-1)) \to ACC(30-0)$ $(C) \to ACC(31), (ACC(0)) \to C$                          |

| $egin{aligned} \mathbf{SACH} &< dma > [, < shift >] \ \\ \mathbf{SACH} &< ind > [, < shift > [, < nextARP >]] \end{aligned}$                                                             | Carga parte al-<br>ta del acumulador con<br>desplazamiento       | $ (C) \to ACC(31), (ACC(0)) \to C $ $ [(ACCH) \times 2^{shift}] \to dma $                                                |

| $egin{aligned} \mathbf{SACL} &< dma > [, < shift >] \ \\ \mathbf{SACL} &< ind > [, < shift > [, < nextARP >]] \end{aligned}$                                                             | Carga parte ba-<br>ja del acumulador con<br>desplazamiento       | $[(ACCL) \times 2^{shift}] \to dma$                                                                                      |

| SBLK < constant > [, < shift >]                                                                                                                                                          | Sustrae constante con desplazamiento                             | $ \frac{(ACC) - [16 - \text{bit constant } \times 2^{shift}] \rightarrow}{ACC} $                                         |

| SFL                                                                                                                                                                                      | Corrimiento del acumu-<br>lador a la izquierda                   | $(ACC(30-0)) \to ACC(31-1)$ $0 \to ACC(0)$                                                                               |

| SFR.                                                                                                                                                                                     | Corrimiento del acumu-<br>lador a la derecha                     | $0 \to ACC(0)$ $(ACC(31-1)) \to ACC(30-0)$ if $SXM = 0$ : then $0 \to ACC(31)$ if $SXM = 1$ : then $ACC(31) \to ACC(31)$ |

| SUB < dma > [, < shift >] $SUB < ind > [, < shift > ] < nontABB > []$                                                                                                                    | Valor en dma se<br>sustrae del acumulador<br>con desplazamiento  | 1 ( ) 2 ( ) 2 ( ) 2 ( ) 2 ( )                                                                                            |

| $egin{aligned} \mathbf{SUB} &< ind > 	ext{[}, < shift > 	ext{[}, < nextARP > 	ext{]} \ \\ \mathbf{SUBB} &< dma > \ \\ \mathbf{SUBB} &< ind > 	ext{[}, < nextARP > 	ext{]} \end{aligned}$ | Valor en dma se<br>sustrae del acumulador<br>con préstamo        | $(ACC) - (dma) - (\overline{C}) \rightarrow ACC$                                                                         |

| SUBC < ind > [, < nextARP >] $SUBC < ind > [, < nextARP >]$                                                                                                                              | Valor en dina se<br>sustrae del acumulador<br>condicionalmente   | $ACC - [,(dma).2^{15}]alALU$                                                                                             |

| SUBH < dma >                                                                                                                                                                             | Valor en dma se sus-<br>trae de la parte alta del<br>acumulador  | $(ACC) - [(dma) \times 2^{16}] \to ACC$                                                                                  |

| $\mathbf{SUBH} < ind > [, < nextARP >]$                                                                                                                                                  |                                                                  |                                                                                                                          |

Tabla 2.1 Instrucciones del DSP que trabajan con el acumulador - Continuación

| SINTAXIS EN ENSAMBLADOR                                                                                                            | TÍTULO                                                                            | DESCRIPCIÓN DE OPERACIONES                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| SUBK < constant >                                                                                                                  | Valor inmediato se sus-<br>trae del acumulador                                    | $(ACC) - 8$ -bit constant $\rightarrow ACC$                                    |

| SUBS < dma >                                                                                                                       | Contenido del dma se<br>sustrae del acumulador<br>sin tomar en cuenta el<br>signo | $(ACC) - (dma) \rightarrow ACC$                                                |

| SUBS < ind > [, < nextARP >]                                                                                                       |                                                                                   |                                                                                |

| $\mathbf{SUBT} < dma >$                                                                                                            | Valor en dma se sustrae<br>del ACC con corrimien-<br>to especificado por T        | $(ACC) - [(dma) \times 2^{(Treg)}] \rightarrow ACC$                            |

| $\mathbf{SUBT} < ind > [, < nextARP >]$                                                                                            |                                                                                   |                                                                                |

| XOR < dma >                                                                                                                        | XOR entre contenido<br>de dma y el acumulador                                     | $(ACC(15-0)).XOR.(dma) \rightarrow ACC(15-0)$                                  |

| XOR < ind > [, < nextARP >]                                                                                                        |                                                                                   |                                                                                |

| $\mathbf{XORK} < constant > [, < shift >]$                                                                                         | XOR entre valor in-<br>media-<br>to y el acumulador con<br>desplazamiento         | $(ACC(30 - 0)).XOR.[16-bit constant \times 2^{shift}] \rightarrow ACC(30 - 0)$ |

| ZAC                                                                                                                                | Carga ceros al acumulador                                                         | $0 \to ACC$                                                                    |

| ZALH < dma >                                                                                                                       | Carga ceros al ACCL<br>y contenido de dma al<br>ACCH                              | $(dma) \times 2^{16} \rightarrow ACC$                                          |

| ZALH < ind > [, < nextARP >]                                                                                                       |                                                                                   | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                        |

| ZALR < dma >                                                                                                                       | Carga ceros al ACCL y contenido de dma al ACCII con redondeo                      | $(dma) \times 2^{16} + > 8000 \rightarrow ACC$ $0 \rightarrow ACCL$            |

| $ \begin{array}{ c c } \hline \mathbf{ZALR} < ind > [, < nextARP >] \\ \hline \hline \mathbf{ZALS} < dma > \\ \hline \end{array} $ | Carga ceros al ACCII                                                              |                                                                                |

|                                                                                                                                    | y contenido de dma al ACCL sin tomar en cuente el signo                           |                                                                                |

| $\mathbf{ZALS} < ind > [, < nextARP >]$                                                                                            |                                                                                   | $0 \rightarrow ACCH$                                                           |

Tabla 2.1. Instrucciones del DSP que trabajan con el acumulador - Continuación

| SINTAXIS EN ENSAMBLADOR                   | TÍTULO                                                           | DESCRIPCIÓN DE OPERACIONES                                                  |

|-------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------|

| ADRK < constant >                         | Suma valor inmedia-<br>to corto al registro<br>auxiliar          | $(ARn) + 8$ -bit constant $\rightarrow ARn$                                 |

| CMPR < constant >                         | Se compara el registro<br>auxiliar con<br>el ARO                 | if $AR(ARP).oper.AR0$<br>then $1 \rightarrow TC$<br>else $0 \rightarrow TC$ |

| $\mathbf{LAR} < AR >, < dma >$            | Valo: en dma se carga<br>al registro auxiliar                    | $(dma) \rightarrow ARn$                                                     |

| LAR < AR >, $< ind > [$ , $< nextARP >$ ] |                                                                  |                                                                             |