# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

# FACULTAD DE INGENIERÍA

"Guía para el Diseño del *Stack-Up* de un PCB multicapas."

INFORME DE ACTIVIDADES

QUE PARA OBTENER EL TÍTULO DE

INGENIERO ELÉCTRICO-ELECTRÓNICO

P R E S E N T A

MAURICIO FERNANDO MÉNDEZ ZAMORA

MÉXICO, D.F., ENERO DE 2014

# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO FACULTAD DE INGENIERÍA

#### **INFORME DE ACTIVIDADES**

PARA OBTENER EL TÍTULO DE: INGENIERO ELÉCTRICO ELECTRÓNICO

POR LA OPCIÓN DE TITULACIÓN: TRABAJO PROFESIONAL

DEBERÁ(N) DESARROLLAR: C. MAURICIO FERNANDO MÉNDEZ ZAMORA

# "GUIA DE DISEÑO DEL *STACK-UP* DE UN PCB MULTICAPAS."

EL OBJETIVO DEL PRESENTE PROYECTO ES LA REDACCIÓN DE UNA GUÍA PARA EL DISEÑO DEL *STACK-UP* DE UN PCB MULTICAPAS. PARA ELLO SE HA TOMADO EN CUENTA LO SIGUIENTE: IMPEDANCIAS INVOLUCRADAS EN EL DISEÑO, CARACTERÍSTICAS DE FACTIBILIDAD DE MANUFACTURA, INTEGRIDAD DE SEÑALES, CAPACIDAD DE ENTREGA DE POTENCIA, ADEMÁS DE CONFIABILIDAD Y CALIDAD.

México, D.F., Enero de 2014

#### **ASESORES**

M. I. Luis Arturo Haro Ruiz M.C. Eduardo Barajas Palomino

JEFE DE LA DIVISIÓN DE INGENIERÍA ELÉCTRICA

Dr. en Ing. Francisco Javier García Ugalde

# Agradecimientos

Mi más sincero y profundo agradecimiento a todas aquellas personas que me brindaron su apoyo desinteresado para hacer posible la realización de este trabajo.

De manera muy especial a:

Luis Arturo Haro Ruiz, por su valiosa orientación para la culminación del presente trabajo.

Gabriel Alejandro Jaramillo Morales, por sus valiosos comentarios

Ricardo Garibay Jiménez, por su apoyo para la realización de este trabajo

Rodolfo Peters Lammel, por sus enseñanzas y paciencia que tuvo conmigo

Alejandro Sosa Fuentes, por su apoyo para la elaboración de este trabajo

Eduardo Barajas Palomino, por la confianza y motivación que me brindó para la realización de este proyecto.

Eduardo De La Paz Rizo, por su invaluable apoyo para la conclusión de este proyecto.

Octavio Gonzáles Castolo, por sus valiosas enseñanzas y tiempo dedicado a la revisión de este trabajo.

Pedro Hermosillo Villalobos, por la confianza y apoyo demostrados.

Julio C. Tinoco Magaña, por su amistad, invaluables enseñanzas y por el tiempo invertido en el anteproyecto de tesis que por situaciones ajenas a la misma no se pudo concluir.

Andrea G. Martínez López., por su amistad, invaluables enseñanzas y por el tiempo invertido en el anteproyecto de tesis que por situaciones ajenas a la misma no se pudo concluir.

A mis Padres Celia y Othón, por el cariño e invaluable apoyo que me brindaron siempre.

A mis hermanos Celia M. y Othón por su comprensión y apoyo.

A mis abuelos por los consejos y orientaciones que siempre me han brindado

#### Resumen

En el presente documento describo el proceso llevado a cabo para diseñar el *stack-up*<sup>a</sup> de un circuito impreso o PCB (del inglés *Printed Circuit Board*), con la intención de su futura implementación.

En última instancia, este documento pretende servir como una fuente donde se puedan consultar los pasos a seguir para el diseño del *stack-up* de un PCB, agilizando con esto su elaboración.

En este documento realizo un breve recorrido sobre los conceptos básicos, previo a la puesta en marcha del diseño. Asimismo, me ha parecido importante mencionar cómo afecta la estructura interna del PCB en el diseño final de un producto.

<sup>&</sup>lt;sup>a</sup> **Stack-up** (del inglés apilado) es la forma en como se refiere a la construcción interna del PCB.

# Índice

| Agradecimientos                     | 3  |

|-------------------------------------|----|

| Resumen                             | 4  |

| Índice                              | 5  |

| 1Introducción                       | 6  |

| 2Objetivo                           | 8  |

| 3Marco Teórico                      | 10 |

| 3.1Breve Historia del PCB           | 10 |

| 3.2Componentes de un PCB            | 12 |

| 3.3Integridad de Señales de un PCB  | 17 |

| 3.4Fabricación y ensamblado del PCB | 22 |

| 4Definición del Problema            | 24 |

| 5Análisis y Metodología             | 25 |

| 6Participación Profesional          | 43 |

| 7Resultados y Aportaciones          | 44 |

| Bibliografía                        | 45 |

| Mesografía                          | 45 |

| Tabla de Contenidos                 | 47 |

| Tabla de Figuras                    | 48 |

| Referencias Biográficas             | 49 |

#### 1. Introducción

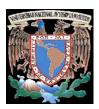

En la Electrónica, un circuito impreso, tarjeta de circuito impreso o PCB es una superficie constituida por trazos o pistas de material conductor laminadas sobre una base no conductora. El PCB se utiliza para conectar eléctricamente (a través de los caminos conductores) y sostener mecánicamente (por medio de la base) un conjunto de componentes electrónicos. Los caminos conductores son generalmente trazos de cobre, mientras que la base se fabrica de resinas de fibra de vidrio reforzada (la más conocida es la FR4<sup>b</sup>), cerámica, plástico, teflón o polímeros como la baquelita. La Figura 1, muestra los diferentes productos ofrecidos por Isola para aplicaciones digitales de alta velocidad; se observa en rojo los materiales más comunes para fabricación en volumen, mientras que en amarillo se indican los nuevos productos para aplicaciones en alta frecuencia (Isola-Group,2013)

Figura 1.-Productos de Isola para aplicaciones digitales de alta velocidad.

<sup>b</sup> El **FR4** es un material compuesto de fibra de vidrio tejida más un aglutinante de resina epoxi que es resistente a las llamas.

La producción de los PCB y el montaje de los componentes en el mismo suelen ser procesos altamente automatizados. Esto permite que, en ambientes de producción en masa, resulten más económicos y confiables que otras alternativas de montaje. En la Figura 2, a la izquierda, se observa el PCB de la tarjeta *Raspberry Pi*, sin ensamblar; a la derecha, se muestra el producto completamente terminado.

Figura 2.-Tarjeta Raspberry Pi

Dentro de un ambiente de desarrollo existen factores cruciales para que un producto pueda ser posicionado dentro del mercado, entre ellos: la definición del producto, el cliente meta y el tiempo de entrada en el mercado son de las más importantes. La definición del producto y el cliente meta nos ayudan a establecer parámetros de diseño para el *stack-up*. Por otro lado, un eficiente proceso de diseño del *stack-up* nos permite ahorrar tiempo y costos durante el ciclo de diseño.

# 2. Objetivo

El objetivo principal del presente proyecto es la elaboración de una guía para el diseño del *stack-up* de un PCB multicapas. Para ello he tomado en cuenta factores que influyen en el diseño de una tarjeta electrónica, como los retos de integridad de señal<sup>c</sup>, capacidad para la distribución de alimentación<sup>d</sup>, las características de factibilidad de manufactura, además, confiabilidad y calidad del mismo.

Los retos de integridad de señal que presentan los diferentes protocolos de comunicación dentro de un diseño electrónico deben ser atacados cuando se diseña un PCB. Esto es, las señales se reflejan, tienen tiempo finito de propagación, la calidad de transmisión de las mismas son afectadas por las discontinuidades y hasta existen diafonías, donde las propias señales interfieren entre sí. Una de las formas más efectivas para mitigar todos estos efectos es el control de impedancia de los trazos conductores; para ello, la correcta definición de planos de referencia es precisa.

De la misma forma, un PCB contiene diferentes circuitos o sub-circuitos que deben ser alimentados con diferentes requerimientos de voltaje y corriente, y esto no puede ser obviado a la hora del diseño del *stack-up* de un PCB. Es importante destacar que una deficiente capacidad de distribución de potencia conlleva a problemas de eficiencia energética y malfuncionamiento del sistema. Es por esto, que el correcto cálculo de la capacidad de entrega de potencia de los diferentes planos de poder es crucial.

Finalmente, el *stack-up* debe ser optimizado para su rendimiento<sup>e</sup>, repetitividad<sup>f</sup> y durabilidad<sup>g</sup>; estos, además de los puntos anteriores, garantizan un buen diseño del PCB y, por tanto, un buen producto terminado con alta calidad y confiabilidad.

<sup>&</sup>lt;sup>c</sup> Se le denomina integridad de señal a los estudios relacionados con las líneas de transmisión, que nos permiten conocer la calidad con la que se transmiten y reciben las señales dentro de un PCB.

<sup>&</sup>lt;sup>d</sup> La capacidad de distribución de alimentación abarca la planeación, estudio, desarrollo, construcción, análisis y operación de las estructuras diseñadas para la entrega de potencia de un PCB.

<sup>&</sup>lt;sup>e</sup> La optimización del rendimiento nos permite mostrar todas las cualidades del producto con eficacia y calidad.

<sup>&</sup>lt;sup>f</sup> La repetitividad de un producto nos permite la fabricación en masa con mínimas probabilidades de fallas en manufactura o diseño.

<sup>&</sup>lt;sup>g</sup> La optimización de la durabilidad nos permite garantizar a los clientes una vida útil de cierto tiempo y que el producto no fallará antes de ese tiempo, bajo condiciones normales de uso.

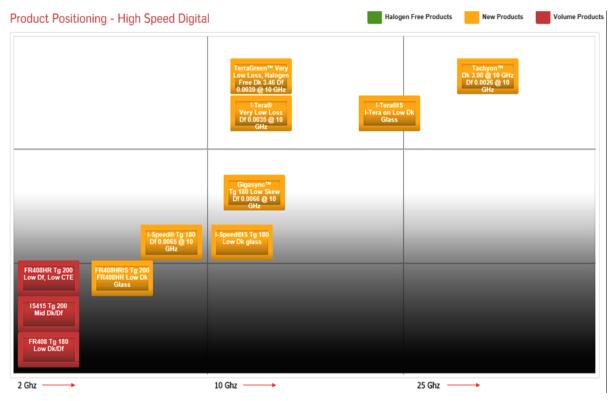

En la Figura 3 vemos una tarjeta ASUS de doble socket en tamaño ATX para procesadores Intel Xeon (Brainiac, 2013).

$\textit{Figura 3.-Tarjeta ASUS Z8NA-D para procesadores Intel $\mathbb{R}$ Xeon $^{\texttt{TM}}$.}$

#### 3. Marco Teórico

Un PCB es un medio que permite conectar eléctricamente componentes electrónicos a través de rutas de material conductor<sup>h</sup> sobre un sustrato no conductor.

Existen varios tipos de PCB, donde el multicapa es el más habitual en el ámbito comercial. Estos suelen tener diverso número de capas dependiendo la complejidad del sistema del que forman parte. Debido al aumento en la integración de componentes dentro de un sistema, el número de interconexiones se ha incrementado de manera significativa. Del mismo modo, los requerimientos tecnológicos son cada vez más demandantes. Por todo ello, un buen diseño de *stack-up* es indispensable.

Como se menciona en la nota de aplicación de ALTERA (Altera Corporation, 2010): "el PCB juega un papel central en el rendimiento de todo el sistema [...] El PCB es el sustrato sobre el cual todos los componentes del diseño son ensamblados. El diseño pobre del *stack-up*, aunado a la selección de materiales inadecuados, puede degradar el rendimiento de la transmisión de señales, entrega de poder, factibilidad de manufactura y confiabilidad de largo plazo del producto terminado [...] En contraste, un PCB diseñado de manera eficiente, reduce emisiones electromagnéticas e interferencia y y mejora la integridad de señal, produciendo una red de distribución de poder con baja inductancia".

#### 3.1.Breve Historia del PCB

La idea del PCB proviene del inventor alemán Albert Hanson<sup>1</sup>, quien propuso la idea de tener conductores llanos de papel de aluminio fijados sobre una placa aislante

<sup>&</sup>lt;sup>h</sup> Los materiales conductores son aquellos cuya resistencia al flujo de la carga eléctrica es muy baja. Los mejores conductores eléctricos son metales, como el cobre, el oro, el hierro y el aluminio, y sus respectivas aleaciones, aunque existen otros materiales no metálicos que también poseen la propiedad de conducir la electricidad, como el grafito o las disoluciones y soluciones salinas (por ejemplo, el agua de mar) o cualquier material en estado de plasma. (Fundación Wikimedia, Inc, 2014)

<sup>&</sup>lt;sup>i</sup> La emisión electromagnética es un tipo de campo electromagnético variable, es decir una combinación de campos eléctricos y magnéticos oscilantes, que se propagan a través del espacio transportando energía de un lugar a otro. <sup>j</sup> La interferencia eléctrica en un PCB tiene su origen en la interacción de la radiación electromagnética y los conductores, estas interferencias pueden producir mal funcionamiento y es por ello que siempre se buscan minimizarles.

formando múltiples capas (Newbury Electronics LTD, 2013). Posteriormente, Thomas Edison<sup>2</sup> experimentó con métodos químicos para desarrollar conductores sobre el papel de lino en 1904. Por su parte Arthur Berry<sup>3</sup> en 1913, patentó un método de impresión y grabado en Gran Bretaña; al mismo tiempo, Max Schoop<sup>4</sup> obtuvo su patente "metal flame-spray sobre una tabla a través de una máscara de modelado".

Posteriormente en 1927, Charles Ducarse<sup>5</sup> patentó un método de galvanoplastia de patrones de circuitos (WebAcademia, 2013).

Hasta la Segunda Guerra Mundial los circuitos se hacían de alambre con forro aislante y uniones soldadas. Durante la Guerra se comenzaron a emplear los circuitos impresos, los cuales trasladaron las técnicas de las artes gráficas a la electrónica. En efecto, la tinta seca era un conductor eléctrico y el circuito quedaba impreso sobre un aislante. Esto facilitaba la producción en serie, ahorraba peso y volumen, además aumentaba la fiabilidad al eliminar o reducir el número de uniones soldadas. En 1947, J.A. Sargrove<sup>6</sup> introdujo en Gran Bretaña el proceso ECME, diseñado para la producción en serie de receptores de radio. Éste implicaba el estarcido de todos los elementos básicos de un circuito sobre una base de plástico mediante la pulverización con cinc líquido (Williams, 1987).

Posterior a la guerra, EEUU libera la tecnología del circuito impreso para uso comercial. Para mediados de 1950 los circuitos impresos se vuelven populares en la electrónica de consumo; ello debido al proceso de auto-ensamblaje desarrollado por la Armada Estadunidense. Dicho proceso, que consistía en insertar los pines de los componentes en una lámina de cobre con el patrón de interconexión, para luego ser soldados, es una contribución que mucho se debe a Moe Abramson y Stanilus F. Danko (Mitzner, 2009)<sup>7</sup>.

Más tarde, en 1958, con la invención del circuito integrado, por parte de Jack Kilby y Robert Noyce<sup>8</sup>, y el consecuente aumento de la densidad de interconexiones (hecho que revolucionó los conceptos de integración de un sistema), el circuito impreso se volvió imprescindible en la electrónica de consumo. Fue en 1961, como consecuencia directa de este elevado nivel de integración, que el primer PCB multicapa vino a luz y, con el tiempo, cada vez más fabricantes de electrónicos se mudaron al uso del PCB.

Todo esto llevó al desarrollo de nuevas combinaciones de laminados para materiales aislantes además de metodologías de grabado del PCB, haciendo que en 1990 el ataque químico mediante sustancias fotosensibles dominara la industria del PCB. (Advanced Circuits, 2013).

# 3.2.Componentes de un PCB

En términos generales, la base sobre la que se construye un PCB se trata de un material aislante (generalmente FR4) laminado con cobre en una o ambas caras; éste es atacado mecánica o químicamente para eliminar partes de cobre y formar así los caminos conductores. Posteriormente, los diferentes laminados se apilan y son presionados entre sí junto con láminas aislantes adicionales y de esta forma se construye un PCB multicapa. A este apilado se le conoce como el **stack-up**. Durante el proceso, las diferentes estructuras que componen el PCB son plasmadas con diferentes finalidades:

• Pistas o trazos: son las líneas de metal (generalmente cobre) que establecen una conexión eléctrica entre dos o varios puntos del circuito. Los diferentes protocolos de comunicación requieren diferentes tipos de trazos dentro del diseño del sistema; es decir, los hay simples o sencillos, que son aquellos que solo requieren un trazo por dato, pero también los hay diferenciales, los cuales demandan un par de trazos acoplados para transmitir la información.

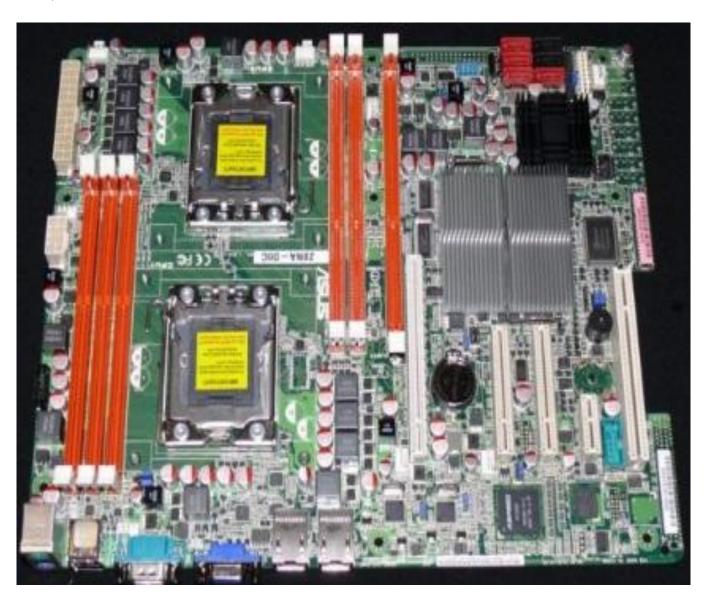

Existen varias alternativas a la hora de implementar una línea diferencial en un PCB. La Figura 4 muestra varios ejemplos: el caso (a) presenta una línea diferencial *microstrip* en el cual las pistas se encuentran en la capa externa de la placa y presentan un acoplamiento horizontal. Los casos (b) y (c) son un par diferencial *stripline* con acoplamiento horizontal y vertical, respectivamente. Estos últimos se encuentran siempre en capas interiores de la placa. Nuevamente, para calcular la impedancia característica de este tipo de líneas es preciso recurrir a algunas de las muchas fórmulas publicadas; incluso, existen aplicaciones online que permiten introducir los parámetros geométricos de una

estructura dada y proporcionan un cálculo muy aproximado de la impedancia característica.

Figura 4.- Tipos de líneas diferenciales en un PCB.

También es muy importante que ambas líneas de un par diferencial midan la misma longitud, evitando así que las señales lleguen a su destino a destiempo (*skew*<sup>k</sup>). Para ello a menudo se utilizan geometrías que nos permitan compensar errores en la longitud de los trazos causados por giros en el trayecto, como se muestra en la Figura 5.

13

<sup>&</sup>lt;sup>k</sup> El **skew** es un problema de tiempo causado por diferentes retardos dentro de un grupo de pulsos que deberían llegar nominalmente al mismo tiempo a un nodo (IPC, 2004).

Figura 5.-Ajuste de longitud en el par diferencial.

Además, las líneas de un par diferencial deben recorrer todo su camino juntas, manteniendo siempre la distancia calculada entre ellas para evitar discontinuidades en la impedancia característica. Si es inevitable una separación, debe minimizarse en lo posible la longitud del trayecto que realizan separadas, el cual tiene un máximo determinado por reglas a fin de evitar problemas en la transmisión de la señal.

- Plano: es una superficie ininterrumpida de cobre que cubre amplias áreas, si no toda la superficie, de la placa. Se usan para distribuir la energía entre numerosos puntos de la placa que alimentarán los circuitos montados en ella; también son útiles para el apantallamiento de señales contra interferencias, y además de que proporcionan un camino de retorno de corriente para pistas en capas adyacentes.

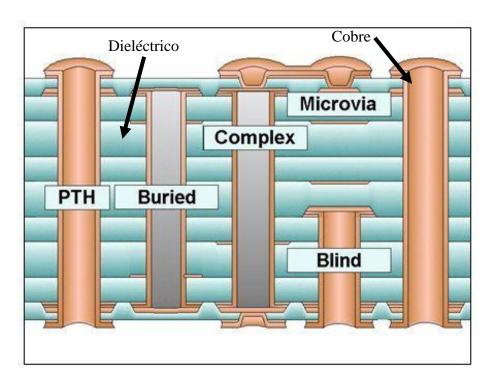

- Vías: son agujeros que atraviesan en vertical el PCB (entre dos capas específicas) y cuya superficie interior ha sido metalizada. Esta metalización proporciona una manera de interconectar las diferentes capas de la placa que atraviesa la vía según sea necesario. Es decir, representan una conexión en el eje Z. Existen diferentes tipos de vías, como se muestra en la Figura 6.

Figura 6.-Sección transversal de las interconexiones típicas (Reid, 2012).

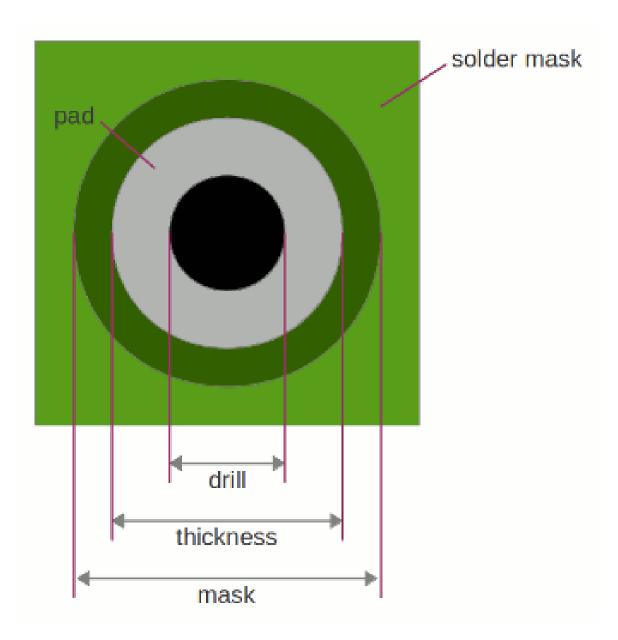

• Pads y antipads: los pads son pequeñas superficies de cobre; éstas permiten la soldadura de los componentes de montaje superficial en las capas externas de la placa o la conexión entre una pista y una vía. Un antipad es el cobre que ha sido eliminado alrededor de un pad para evitar que éste entre en contacto con un plano u otras pistas, evitando corto-circuitos. En la Figura 7 se muestran las diferentes partes de la estructura de una vía: la perforación (la parte negra), el pad (el anillo gris) y el antipad (anillo verde obscuro).

Figura 7.-Perforación, pad y antipad de una vía.

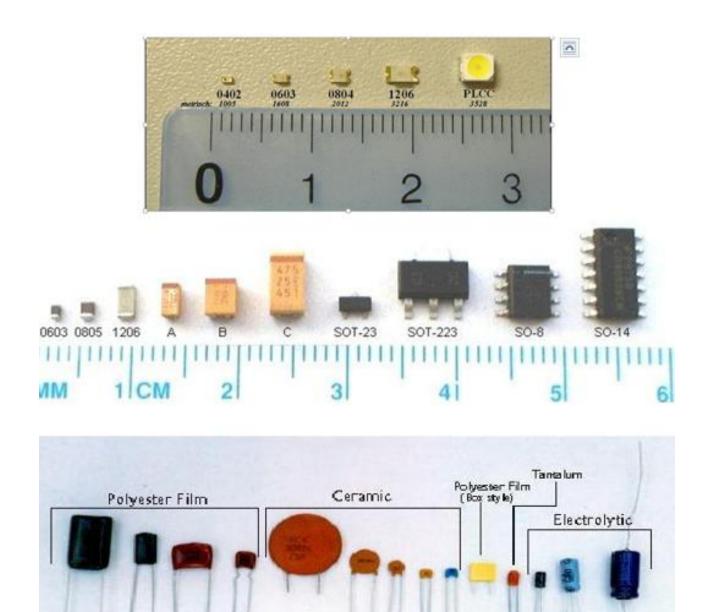

Componentes: son todos los elementos activos y pasivos que se montan sobre la tarjeta (Véase la Figura 8). Existen componentes de montaje superficial o SMD (del inglés Surface Mount Device), y aquéllos con terminales que atraviesan la tarjeta o THM (del inglés Thru Hole Mount).

Figura 8.- Diferentes tipos y tamaños de componentes SMD y THM.

# 3.3.Integridad de Señales en un PCB

Aparte de las estructuras arriba mencionadas que componen a un PCB, éste debe garantizar en lo posible que las señales se transmitan de manera correcta. En un PCB, las señales se ven afectadas por los siguientes fenómenos físicos:

- Reflexión de señal: ésta se presenta cuando una corriente que viaja en una dirección se encuentra con un obstáculo y provoca que una parte de ella cambie su dirección de movimiento, lo cual resulta en ruido que afectará la integridad de la señal transmitida. Esto ocurre, por ejemplo, cuando hay una discontinuidad en la impedancia del trazo sobre el cual circula la señal.

- Tiempo de viaje de la señal: en algunos protocolos de comunicación la información se envía simultáneamente a través de varias pistas; esto es conocido como comunicación en paralelo. En este tipo de comunicación es esencial que las señales que viajan a través de los trazos conductores alcancen el otro extremo casi al mismo tiempo (estrictamente hablando, dentro de una ventana de tiempo denominada skew); de no ser así, el circuito podría no funcionar de la manera esperada. Esto es algo a tener muy en cuenta en las interfaces de alta velocidad que son sincronizadas con reloj propio del bus.

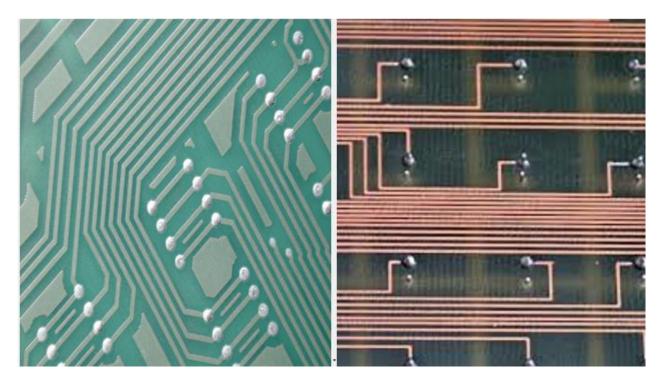

- Discontinuidad en la señal: ésta es definida como el cambio de la resistencia a la corriente; es decir, un cambio de impedancia resultará en una discontinuidad de la señal. En circuitos donde las señales alternan a alta velocidad, las pequeñas discontinuidades pueden degradarla de manera significativa provocando malfuncionamiento. Un ejemplo común son los ángulos rectos o agudos al cambiar de sentido una señal. Estos provocan discontinuidades debido al incremento de la sección transversal justo en la esquina. Además, se presentan otros fenómenos electromagnéticos como la concentración de carga en el vértice, el cual redunda en radiación de la energía, o fenómenos autoinducidos por la cercanía de ambos segmentos del trazo. También, existen riesgos de manufactura causados por posibles trampas de ácido en los vértices.

Figura 9.- Tarjeta con ángulos suavizados (izquierdo) y ángulos rectos (derecha).

• Diafonía: éste es un fenómeno físico causado por la interacción de los campos electromagnéticos que son el resultado de las corrientes de las señales que viajan por dos trazos conductores próximos. Esta interacción introduce ruido a las señales, degradándolas. A este fenómeno se le conoce como crosstalk en inglés. En señales de alta velocidad, la rapidez del cambio de la corriente en las pistas produce grandes campos electromagnéticos. La manera de atacar este problema es separando en lo posible los trazos de dichas señales.

Para la medida de la diafonía se envía por el circuito perturbador una señal de un nivel conocido, y se mide el nivel recibido en el circuito perturbado. No obstante, dependiendo de que la medida la hagamos en el mismo extremo desde el que estamos enviando la señal o en el extremo distante tendremos dos valores distintos. Así llegamos a los conceptos de paradiafonía o diafonía de extremo cercano y telediafonía o diafonía de extremo lejano.

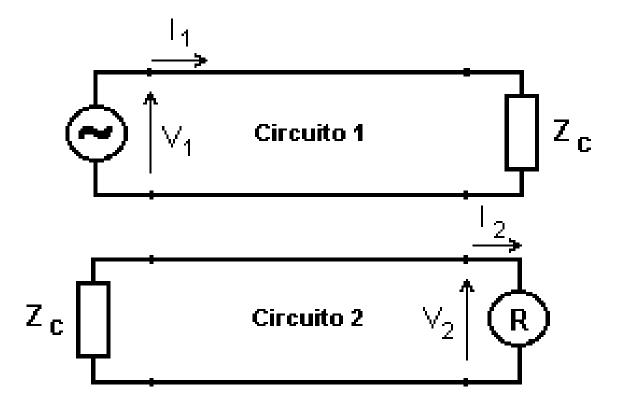

Telediafonía (Fundación Wikimedia, Inc, 2013). La disposición de elementos para la medida de la telediafonía o diafonía de extremo lejano, denominada en inglés Far end crosstalk (FEXT), se muestra en la Figura 10, donde vemos como en el Circuito 1 tenemos un generador que envía una señal de nivel V1, en un extremo, mientras que el otro extremo está terminado con una impedancia Zc igual a la impedancia característica del circuito.

- El Circuito 2, está cargado en el extremo emisor con Zc y en el extremo distante tenemos un medidor de nivel (R) en el que mediremos un cierto nivel de señal V2 correspondiente a la diafonía.

- A la relación en decibeles existente entre V1 y V2 es a lo que se denomina atenuación de telediafonía (αt),y es igual a:

$$\alpha_t = 20 \times log \frac{V_1}{V_2}$$

Figura 10 .-Disposición de elementos para la medida de telediafonía.

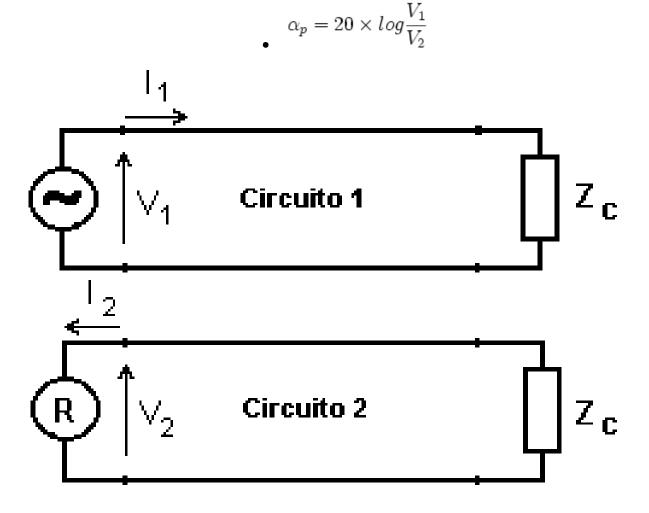

Paradiafonía (Fundación Wikimedia, Inc, 2013). La disposición de elementos que calcula la potencia de medidas para la medida de la paradiafonía o diafonía de extremo cercano, denominada en inglés Near end crosstalk (NEXT), se muestra en la Figura 11, en la cual aparecen ambos circuitos terminados en su impedancia característica Zc en el extremo distante, mientras que en el extremo cercano el emisor se halla conectado en el Circuito 1 y el medidor en el Circuito 2.

A la medida de la relación en decibeles entre las señales emitida y recibida, obtenida con esta disposición de los instrumentos de medida, es a lo que se denomina atenuación de paradiafonía (αp), cuyo valor es igual a:

Figura 11.- Disposición de elementos para la medida de paradiafonía.

En la actualidad, muchos de los circuitos integrados en el mercado, constan de una guía de diseño donde se establecen los requerimientos que surgen del análisis de la integridad de señales.

Algunos de los valores más importantes de dicha guía de diseño son justo los relacionados con la diafonía. En la Figura 12 (Intel Corporation, 2000), se muestra un ejemplo de una tabla de requerimientos de la solución de trazado de la memoria del sistema de una plataforma. En ella, se establece el ancho de trazo, el espaciamiento requerido entre trazos, así como las longitudes permitidas para cada interfaz.

| Signal                      | Top. | Trac  | Trace Lengths (inches) |      |      |      |      |      |      |      |      |      |      |      |      |

|-----------------------------|------|-------|------------------------|------|------|------|------|------|------|------|------|------|------|------|------|

|                             |      |       |                        | A    |      | В    |      | С    |      | D    |      | E    |      | F    |      |

|                             |      | Width | Spacing                | Min. | Max. |

| SCS[3:2]#                   | 3    | 5     | 10                     |      |      |      |      |      |      | 1    | 4.5  |      |      |      |      |

| SCS[1:0]#                   | 2    | 5     | 10                     |      |      |      |      | 1    | 4.5  |      |      |      |      |      |      |

| SMAA[7:4]                   | 4    | 10    | 10                     |      |      |      |      |      |      |      |      | 0.4  | 0.5  | 2    | 4    |

| SMAB[7:4]#                  | 5    | 10    | 10                     |      |      |      |      |      |      |      |      | 0.4  | 0.5  | 2    | 4    |

| SCKE[3:2]                   | 3    | 10    | 10                     |      |      |      |      |      |      | 3    | 4    |      |      |      |      |

| SCKE[1:0]                   | 2    | 10    | 10                     |      |      |      |      | 3    | 4    |      |      |      |      |      |      |

| SMD[63:0]                   | 1    | 5     | 10                     | 1.75 | 4    | 0.4  | 0.5  |      |      |      |      |      |      |      |      |

| SDQM[7:0]                   | 1    | 10    | 10                     | 1.5  | 3.5  | 0.4  | 0.5  |      |      |      |      |      |      |      |      |

| SCAS#, SRAS#, SWE#          | 1    | 5     | 10                     | 1    | 4.0  | 0.4  | 0.5  |      |      |      |      |      |      |      |      |

| SBS[1:0],<br>SMAA[12:8,3:0] | 1    | 5     | 10                     | 1    | 4.0  | 0.4  | 0.5  |      |      |      |      |      |      |      |      |

Figura 12 .- Solución del trazado de la memoria del sistema para 2-DIMM

# 3.4. Fabricación y ensamblado del PCB

Sólo cuando las especificaciones y restricciones del sistema se cumplen se puede enviar el diseño a fabricación. Durante el desarrollo del proyecto he tenido que contactar con fabricantes, solicitar asistencia técnica, consejo y varios presupuestos.

Desde que se tiene el diseño analizado hasta que se tiene el PCB en las manos se puede decir que hay que realizar tres operaciones comerciales. La primera de ellas es el envío de los archivos *gerbers*<sup>1</sup> correspondientes al diseño del PCB a una empresa especializada para que proceda a la fabricación del mismo. Las reglas de diseño para fabricación, como por ejemplo el ancho mínimo de una pista, el espaciamiento mínimo entre trazos o el mínimo diámetro de las vías, son consideraciones que se deben

Los **gerbers** (formato de fichero desarrollado por Gerber System Corp.) son los archivos que contienen la información necesaria para la fabricación de un circuito impreso o PCB (Fundación Wikipedia Inc, 2013).

cumplir y aclarar con la empresa para garantizar la factibilidad de manufactura del diseño realizado. Otras especificaciones que debemos considerar", son los tipos de tecnologías a utilizar y el estándar de manufactura.

La segunda de las operaciones corre en paralelo con la primera, si no es que previa a ella. Esta consiste en la compra de los componentes, también llamado el  $BOM^m$ , que se han de montar en el PCB. Si bien todos los componentes pasivos y muchos de los circuitos integrados son fáciles de adquirir, algunos componentes más complejos, como la FPGAs, los controladores de VRs o ciertos conectores, pueden estar sujetos a fabricación bajo pedido, lo que conlleva a demoras en la obtención de los mismos de varias semanas. El retraso mencionado puede impactar seriamente al calendario de la entrega del producto final, por lo que es necesario anticiparse a ello.

Por último, la tercera de las operaciones, es el ensamblado del conjunto PCB más BOM. Esta operación consiste en montar y soldar todos los componentes en la placa. Por lo general, el ensamblado es un proceso altamente automatizado. Sin embargo, pueden llegar a existir casos donde el montaje tenga que ser hecho a mano, caso en el cual se suele especificar detalladamente. Para componentes SMD, el proceso de ensamblado más común consiste en realizar perforaciones con láser a una plantilla de metal que se usa como máscara sobre el PCB para depositar una pasta de soldar. Luego, los componentes se depositan en su sitio en la placa (usando brazos robóticos con inspección visual automatizada) donde quedan sujetos por esta pasta para pasar a su posterior fijación mediante horneado. Finalmente, el PCB es introducido en un horno especial con temperatura controlada, la cual funde la soldadura en pasta y fija los componentes sobre la placa. Además, la fuerza tensorial del estaño al fundirse corrige las pequeñas desviaciones que se pueden haber producido durante el montaje de los componentes sobre la tarjeta empastada. En lo que respecta a, si los componentes lo permiten, la tarjeta es nuevamente introducida a la máquina de ensamble automatizado para colocar así todos los componentes THM. Sin embargo, existen componentes THM de mayor tamaño, conectores principalmente, que necesitan

\_

<sup>&</sup>lt;sup>m</sup> **BOM** (del inglés *Bill Of Materials*) es el conjunto de componentes que se han de montar en un PCB, como parte del diseño de la tarjeta.

ser colocados manualmente. Cabe mencionar que estos procesos varían entre fabricantes, tipos de tarjetas y volumen de las mismas.

#### 4.- Definición del Problema

En el desarrollo y fabricación de prototipos electrónicos, es necesaria la realización de un diseño preliminar en el cual se puedan evaluar las características generales del prototipo. En todos los casos, esto obliga la creación de un PCB. El correcto diseño del PCB disminuye la probabilidad de falla del prototipo, proveyendo así una base sólida para la experimentación.

El desconocimiento de los conceptos básicos para el desarrollo del stack-up de un PCB ocasiona retrasos en el ciclo de diseño. Un ciclo de diseño extendido implica costos más elevados y pérdida de competitividad al no poder salir a tiempo al mercado. Por ello, el desarrollo de una guía de diseño del stack-up de un PCB es importante para el ahorro de costos y tiempo. Es por esto que fui asignado a la tarea de crear este documento.

# 5.- Análisis y Metodología

Para la elaboración de este documento, me di a la tarea de enriquecer mi conocimiento de un PCB, por lo que recurrí la investigación en medios electrónicos e impresos.

- "Es una tarjeta o placa utilizada para realizar el emplazamiento de los distintos elementos que conforman el circuito y las interconexiones eléctricas entre ellos" (Cohen, 2010).

- 2. "Es la estructura física para montar y retener los componentes electrónicos, así como, la interconexión eléctrica de los componentes" (Khandpur, 2005).

- 3. "Es una tarjeta impresa que posee conexiones punto a punto y componentes impresos en un arreglo predeterminado sobre una base común" (IPC, 2011).

Luego, vino la comprensión de los elementos que conforman a un PCB, los cuales ya han sido descritos en una sección anterior.

El siguiente paso consistió en obtener las restricciones tecnológicas aplicables al segmento del mercado en el cual se va a introducir el producto final. En lo referente a las tecnologías de fabricación de un PCB, existen una gran variedad de conceptos que deben ser considerados (IPC, 2013):

- 1. El tipo de laminado

- a. Rígido.

- b. Flexible.

- c. HDI.

- 2. El tipo de enchapado o acabado

- a. Enchapado electrolítico de níquel sumergido en oro (ENIG).

- b. Enchapado por inmersión en plata.

- c. Enchapado por inmersión en estaño.

- d. Enchapado electrolítico de níquel/paladio inmerso en oro (ENEPIG).

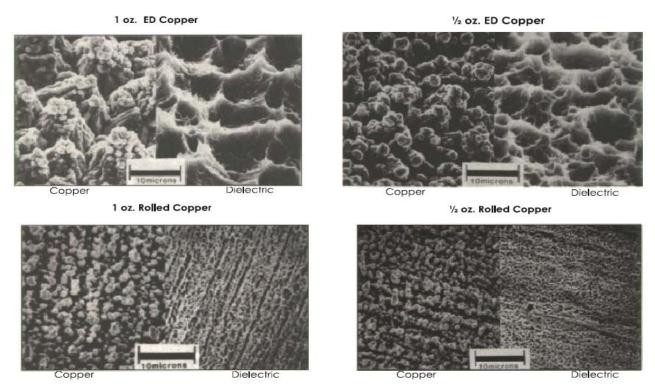

- 3. El tipo de rugosidad de las láminas de cobre

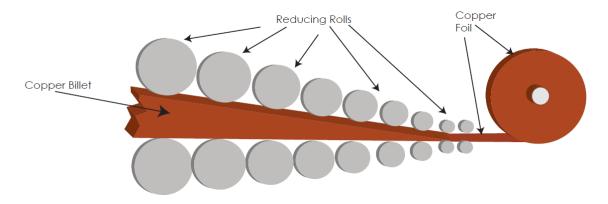

# a. Láminas de cobre rolado (baja rugosidad).

Figura 13 Proceso de manufactura del cobre rolado (Rogers Corporation, 2011).

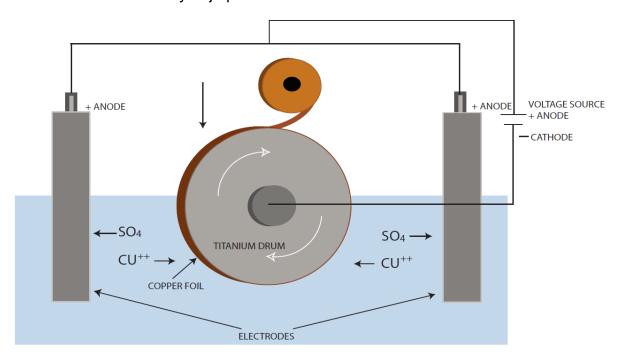

- b. Láminas de cobre electro-depositado.

- i. Alto perfil.

- ii. Perfil estándar.

- iii. Bajo perfil.

- iv. Muy bajo perfil.

Figura 14.-Proceso de manufactura del cobre electro-depositado (Rogers Corporation, 2011).

Figura 15.- Comparación de la rugosidad entre una lámina de cobre rolado y una de cobre electro-depositado estándar (Rogers Corporation, 2011).

Una vez reunida toda esta información, pasé al diseño propio del stack-up de un PCB.

# 1. Seleccionando el número de capas correcto.

"El número total de capas requerido para un diseño dado depende de la complejidad del mismo. La complejidad de un PCB incluye el número de señales que deben salir de un dispositivo, el número de planos de poder, y la densidad y tipos de empaquetados asociados al BGA" (Altera Corporation, 2010).

Una vez encontrado el número mínimo de capas de señal necesarias para el break-out<sup>n</sup> de todas las señales del BGA, con el arreglo más denso de pines, se debe tomar en consideración que cada capa de señal debe tener plano adyacente que pueda ser usado como plano de referencia para las interfaces de alta velocidad.

-

<sup>&</sup>lt;sup>n</sup> **Break-out** es el término utilizado para referirse a la sección de trazo que pasa por debajo de un componente y es utilizado para dar un escape a las señales del campo de pines. Por lo general este requiere una geometría más compacta.

# a. Break-out de componentes.

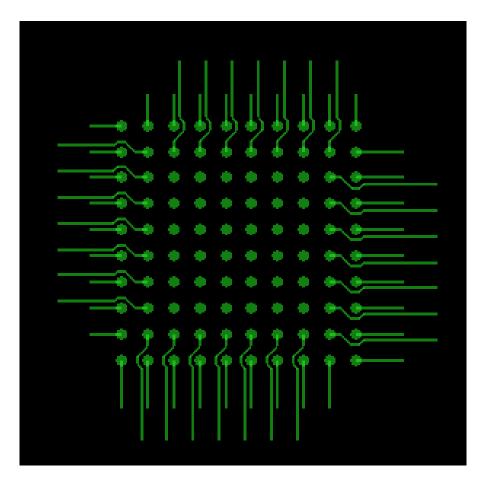

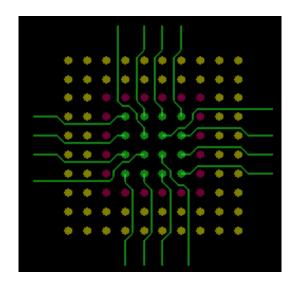

Para obtener el mínimo número de capas para un BGA se hace de la siguiente manera. Considere un BGA cualquiera para nuestro ejemplo utilizaremos el mostrado en la siguiente figura:

Figura 16.-BGA de 100 pines.

De la figura anterior, consideraremos que el componente está colocado en la capa superior de nuestra tarjeta. Sobre esta misma capa se podrían extraer las primeras dos hileras de pines de nuestro BGA, como se muestra en la Figura 16; así definimos nuestra primera capa de señal.

Figura 17.-Break-out de la tercera hilera de pines del BGA.

Debido a la densidad de pines en este dispositivo, las capas subsecuentes no serán tan productivas como la primera, por lo que solo se podrán hacer la extracción de una sola línea de pines a la vez. Quedando definida nuestra segunda capa de señal (ver Figura 17).

Figura 18.- Break-out de los pines más internos del BGA.

Por último, podemos extraer el resto de las señales en esta última capa. Gran parte del trabajo del ingeniero de CAD es optimizar los canales disponibles para el break-out de señales, para minimizar en lo posible el número total de capas (ver Figura 18).

Una vez hecho este ejercicio, podemos considerar que el mínimo número de capas de señal para hacer el break-out, de este BGA, es tres (esto sin considerar otro tipo de restricciones, sólo las implicaciones físicas). Recordando que cada capa de señal debe tener adyacente a sí un plano de referencia, podríamos decir que el mínimo necesario para elaborar un producto donde se use este BGA sería de 5 capas (este tipo de ensamble no es común; sin embargo, es factible). Lo más común es encontrar ensambles de un número par de capas. En una segunda etapa de este mismo proceso se puede intentar reducir el número de capas jugando con las capas de alimentación de señal (esto no se recomienda para interfaces de alta velocidad).

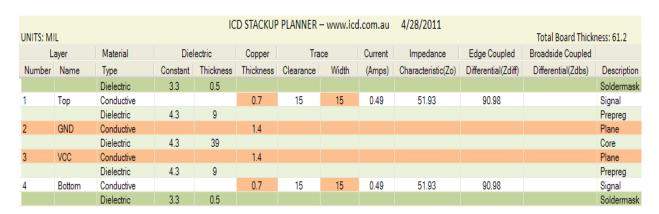

Figura 19.- Ejemplo de un stack-up de 4 capas (Altera Corporation, 2010).

| ICD STACKUP PLANNER – www.icd.com.au |         |            |            |           |           |                 |    |         | 4/28/2011                 |                     |                    |             |  |

|--------------------------------------|---------|------------|------------|-----------|-----------|-----------------|----|---------|---------------------------|---------------------|--------------------|-------------|--|

| UNITS: MI                            | L       |            |            |           |           |                 |    |         | Total Board Thickness: 63 |                     |                    |             |  |

| Layer                                |         | Material   | Dielectric |           | Copper    | Trace           |    | Current | Impedance                 | Edge Coupled        | Broadside Coupled  |             |  |

| Number                               | Name    | Туре       | Constant   | Thickness | Thickness | Clearance Width |    | (Amps)  | Characteristic(Zo)        | Differential(Zdiff) | Differential(Zdbs) | Description |  |

|                                      |         | Dielectric | 3.3        | 0.5       |           |                 |    |         |                           |                     |                    | Soldermask  |  |

| 1                                    | Тор     | Conductive |            |           | 0.7       | 12              | 12 | 0.42    | 50.81                     | 89.45               |                    | Signal      |  |

|                                      |         | Dielectric | 4.3        | 7         |           |                 |    |         |                           |                     |                    | Prepreg     |  |

| 2                                    | GND     | Conductive |            |           | 1.4       |                 |    |         |                           |                     |                    | Plane       |  |

|                                      |         | Dielectric | 4.3        | 15        |           |                 |    |         |                           |                     |                    | Core        |  |

| 3                                    | Inner 3 | Conductive |            |           | 1.4       | 12              | 12 | 0.69    | 52.65                     | 88.5                | 66.91              | Signal      |  |

|                                      |         | Dielectric | 4.3        | 12        |           |                 |    |         |                           |                     |                    | Prepreg     |  |

| 4                                    | Inner 4 | Conductive |            |           | 1.4       | 12              | 12 | 0.69    | 52.65                     | 88.5                | 66.91              | Signal      |  |

|                                      |         | Dielectric | 4.3        | 15        |           |                 |    |         |                           |                     |                    | Core        |  |

| 5                                    | VCC     | Conductive |            |           | 1.4       |                 |    |         |                           |                     |                    | Plane       |  |

|                                      |         | Dielectric | 4.3        | 7         |           |                 |    |         |                           |                     |                    | Prepreg     |  |

| 6                                    | Bottom  | Conductive |            |           | 0.7       | 12              | 12 | 0.42    | 50.81                     | 89.45               |                    | Signal      |  |

|                                      |         | Dielectric | 3.3        | 0.5       |           |                 |    |         |                           |                     |                    | Soldermask  |  |

Figura 20.-Ejemplo de un stack-up de 6 capas (Altera Corporation, 2010).

Analizando las estructuras internas de las Figuras 19 y 20, ambas cuentan con solo una capa de tierra y otra de poder; sin embargo, el stack-up de 6 capas de la Figura 20 cuenta con el doble de capas de señal que el de la Figura 19. Por otro lado, el stack-up de 6 capas cuenta retos diferentes que asimilar. Por ejemplo, debido que no hay capas de alimentación que aísle la capa 3 de la capa 4, existirá acoplamiento entre las señales de cada una de estas capas. Para evitar esto se busca que las señales de alta velocidad que vayan en estas capas sean trazadas en forma lo más ortogonalmente posible para minimizar el tiempo que las señales viajan acopladas.

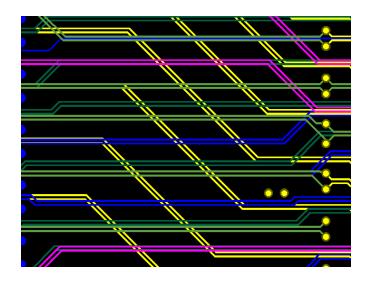

Figura 21.- Trazos de pares diferenciales (gendreaumicrosystems.com, 2012).

Una regla básica en el diseño del stack-up de un PCB es que se debe optimizar el número de capas para no incrementar el costo del mismo. El costo del PCB podría llegar a ser el 30% del costo final de un producto. Es por esto que siempre se buscan estructuras internas donde me maximice el número de capas de ruteo, con el mínimo número de capas totales.

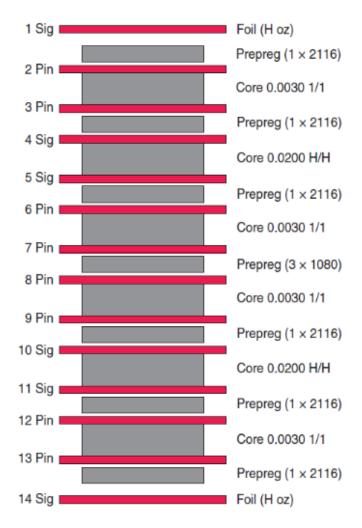

#### b. Análisis de la estructura interna del PCB: El stack-up.

"Un PCB típico es construido de múltiples capas alternadas de núcleos, prepreg y láminas de cobre; comprimidas bajo calor y pegadas juntas." Por ejemplo:

Figura 22.- Composición de un PCB (Altera Corporation, 2010).

En el caso de la figura 22, se define como núcleo (o *core*) a una pieza de fibra de vidrio con láminas de cobre en ambos lados que han sido "curadas" previamente. Los prepreg son capas de fibra de vidrio y resina que se usan para pegar los núcleos entre sí.

### 2. Número y tipo de planos de poder.

El número de planos dependerá de los diferentes niveles de voltajes necesarios a lo largo de toda la tarjeta; algo muy importante a definir es la interacción entre ellos. En ocasiones ciertos niveles de voltajes muy disparejos (12V vs 1.2V) pueden causar acoplamiento de rizo induciendo ruido; sobre todo de los niveles más altos a los más bajos. Un claro ejemplo:

Suponga que una fuente de alimentación de 12V tiene un rizo de 3%; esto quiere decir que ese nivel de voltaje tendrá una componente alternando entre 11.74V y 12.36V. Del mismo modo, imagine un plano que se sobrepone en una capa adyacente. Esto ocasionaría acoplamiento entre ambos planos de alimentación, produciendo que el ruido visto en ambos niveles de voltaje cambie proporcionalmente al nivel de rizo. En el caso del plano de 12V la interacción con el plano de 1.2V puede desmerecer. Sin embargo, en el caso contrario, donde el plano de 1.2V es agredido por el rizo plano de 12V, debido a la magnitud del rizo, podríamos ver una variación en los niveles del plano de varias décimas de volt. Si se considera que cierta lógica con transistores es alimentada a 1.2V, declarando 0 lógico entre 0-0.3 V y 1 lógico entre 0.9 y 1.2V, un ruido de varias décimas de volt podría causar inestabilidad de nuestra lógica declarando niveles lógicos espurios.

En cuanto a cómo esta definición de número y tipos de planos de poder afecta la selección de número de capas, hay que hacer un estudio de cuántos planos son necesarios y dónde se necesitan para evitar sobreponerlos. Este estudio es un caso muy particular para cada sistema.

# 3. Orden y secuencia de las capas del stack-up.

En un PCB se colocan los componentes en las capas superior (TOP) e inferior (BOTTOM) del mismo. Estas dos capas pudieran ser mixtas, tanto para ruteo de trazos de señal como para colocar planos de poder.

Otro dogma en el diseño de PCB es que la estructura interna debe ser simétrica del centro hacia los extremos capa a capa. Esto es de vital ayuda desde el punto de vista mecánico, de integridad de señal, calidad y manufactura.

El siguiente punto importante es que todas las señales de transición rápida requieren que su plano de referencia sea sólido y lo más limpio de ruido posible. Es por ello que por lo general les referenciamos a tierra, puesto que los planos de tierra en un PCB suelen ser sólidos en toda la tarjeta. Por el contrario, los planos de potencia suelen ser seccionados o segmentados desde el punto de vista del trazo de la señal; esto porque hay diferentes voltajes alimentando el diseño. Por otro lado si no se tienen capas dedicadas a entrega de poder los planos pueden ser colocados en capas de señal haciendo el debido análisis.

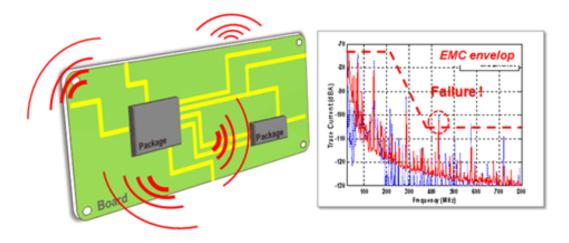

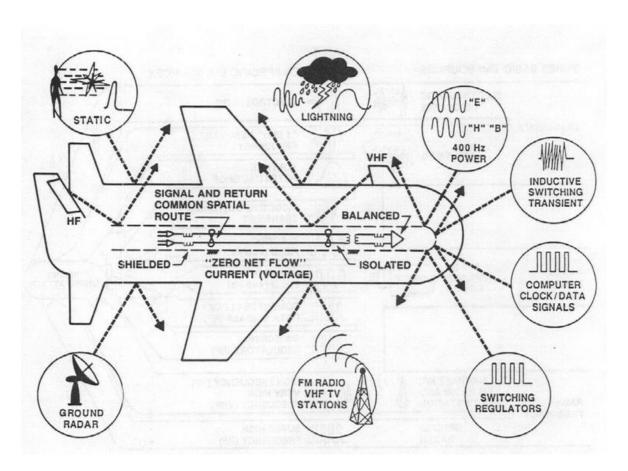

El tener un par de capas dedicadas a tierra sólida reduce las emisiones electromagnéticas de nuestros circuitos. En la actualidad, existen varias regulaciones relacionadas con las emisiones que nuestros dispositivos deben soportar sin fallar del mismo modo aquellas que pueden irradiar para evitar malfuncionamiento de otros circuitos electrónicos así como dañar la salud.

Figura 23.- Emisiones Electromagnéticas emitidas por los circuitos.

# 4. Espacio entre capas.

El espacio entre capas determina la factibilidad de manufactura, así como el costo de los procesos requeridos para la manufactura. La parte más importante de determinar el espacio entre capas es que éste determina la impedancia de los trazos que entre ellas coexisten.

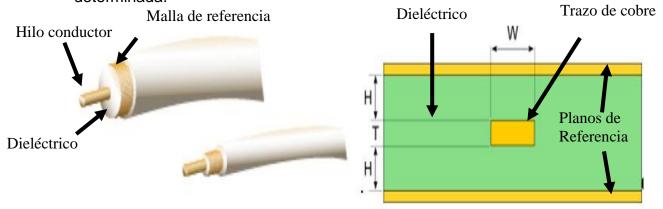

La impedancia (Z) generalmente se define como la oposición total que ofrece un dispositivo o un circuito al flujo de una corriente a una frecuencia determinada.

Figura 24.- Comparación que podríamos realizar entre un cable coaxial y un PCB

Una comparación que podríamos realizar sería entre un cable coaxial y un PCB, donde la malla circundante representaría el plano de referencia, el aislante sería el material dieléctrico entre capas o distancia entre la pista y plano de referencia, y el conductor estaría representado por la pista (Figura 24).

#### a. Definición de impedancias.

Si se considera un diseño de alta velocidad con impedancia controlada, a menudo son los componentes y cables de entrada y salida los que determinan los valores de impedancia de la línea de transmisión (IPC, 2004).

Por otro lado, el ancho del trazo conductor para las líneas de trasmisión varía entre 0.003in y 0.03in, esto limita en cierto sentido las opciones de interconexión. Así mismo, el grosor del dieléctrico es un factor más que restringe las opciones del diseño físico de las líneas de transmisión. El rango

de la permitividad relativa de los dieléctricos se encuentra entre 2.9 a 4.7, también existen materiales exóticos usados en aplicaciones de muy alta frecuencia, sin embargo, los principios de economía dictan que los materiales más comunes deben ser usados para las aplicaciones comerciales y de consumo. (IPC, 2004)

En internet se pueden encontrar varias páginas que contienen calculadoras de impedancias para trazos en PCB. Ciertos fabricantes de PCB ayudarán a resolver este tipo de cuestiones, puesto que son los más experimentados al respecto.

Figura 25.- Calculadora de impedancias en línea. (Aspen Labs, LLC, 2013)

Las ecuaciones utilizadas en estas páginas son las siguientes aproximaciones (IPC, 2000) (IPC, 2004):

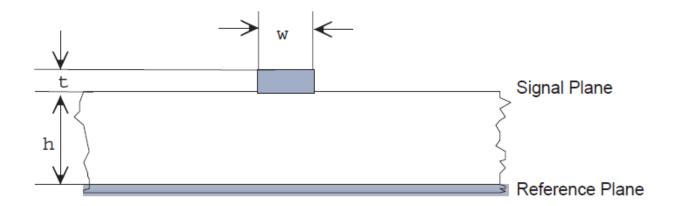

Figura 26.- Trazo microstrip.

$$\begin{split} Z_{0,surf} &= \frac{\eta_0}{2\sqrt{2\pi}\sqrt{\varepsilon_{r,eff}+1}} \ln \left\{ 1 + 4\frac{h}{w'} \left[ 4 \left( \frac{14\varepsilon_{r,eff}+8}{11\varepsilon_{r,eff}} \right) \frac{h}{w'} \right. \right. \\ &+ \left. \sqrt{16 \left( \frac{14\varepsilon_{r,eff}+8}{11\varepsilon_{r,eff}} \right)^2 \left( \frac{h}{w'} \right)^2 + \frac{\varepsilon_{r,eff}+1}{2\varepsilon_{r,eff}} \pi^2} \right] \right\} \end{split}$$

Donde  $\eta_0$  es la impedancia de la onda en el espacio libre, w' es el ancho efectivo de trazo.

$$w' = w + \frac{t}{\pi} \ln \left\{ \frac{4e}{\sqrt{\left(\frac{t}{h}\right)^2 + \left(\frac{t}{w\pi + 1.1t\pi}\right)^2}} \right\} \left( \frac{\varepsilon_{r,eff} + 1}{2\varepsilon_{r,eff}} \right)$$

$$\begin{split} \varepsilon_{r,eff} &= \left\{ \frac{\varepsilon_{r,eff} + 1}{2} + \frac{\varepsilon_{r,eff} - 1}{2} \left\{ \sqrt{\frac{w}{w + 12h}} + 0.04 \left(1 - \frac{w}{h}\right)^2 \right\}; \frac{w}{h} < 1 \right\} \\ & \bullet \\ \varepsilon_{r,eff} &= \left\{ \frac{\varepsilon_{r,eff} + 1}{2} + \frac{\varepsilon_{r,eff} - 1}{2} \left\{ \sqrt{\frac{w}{w + 12h}} \right\}; \frac{w}{h} \ge 1 \right\} \end{split}$$

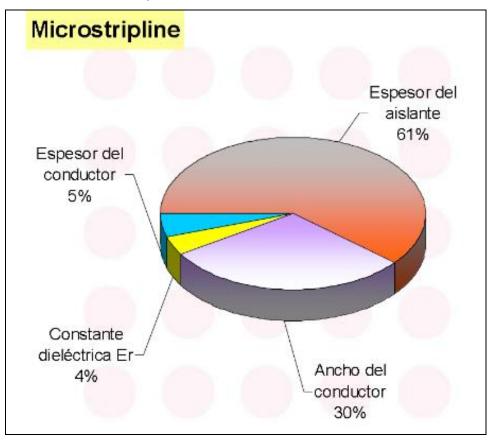

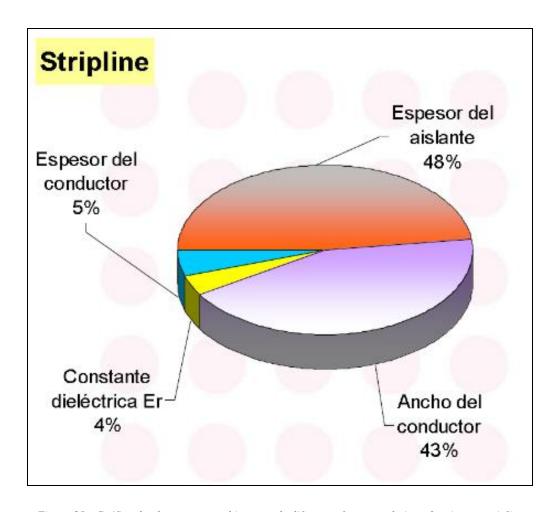

Si se quiere conseguir un diseño con interconexiones de impedancia controlada. Se debe considerar: (IPC, 2004)

- Sección transversal del conductor: los trazos conductores, particularmente en capas externas, son sensibles a las variaciones causadas por el enchapado y la formación dispareja del trazo. Líneas más gruesas tienen impedancia más baja que las más delgadas.

- Tipo de estructura de la línea de transmisión: esto es, dados una permitividad relativa, espaciamiento y ancho de trazo, los valores de la impedancia serán mayores en las capas externas que en las internas.

- Permitividad Relativa  $(\varepsilon_r)$ : de una permitividad más elevada nos resulta una impedancia menor y por tanto se incrementa el tiempo de propagación.

- Separación dieléctrica entre señal y tierra: la impedancia decae mientras la separación se reduce.

Figura 27.- Gráfica donde se muestra el impacto de diferentes factores a la impedancia para microstip

Figura 28.- Gráfica donde se muestra el impacto de diferentes factores a la impedancia para stipline

Otros factores de menor importancia a considerar para el diseño, con impedancias controladas son (IPC, 2004):

- Use la lámina de cobre más delgada que satisfaga sus necesidades,

la impedancia decrece ligeramente cuando el espesor de cobre incrementa. Esto como resultado del incremento de la capacitancia causada por los bordes más gruesos de la línea de transmisión.

- Mantenga conductores de impedancia controlada y planos de referencia que se encuentren localizados en la misma capa, suficientemente lejos para evitar acoplamiento. La regla de dedo es que el espaciamiento deber ser mayor a seis veces el ancho del conductor más grueso o seis veces la distancia entre las señales y el plano de referencia.

- El retorno de corriente para señales de alta velocidad es por lo general el plano de referencia más cercano a la señal. El recorrido de retorno no debe encontrar discontinuidades, esto es; que este se corte en algún punto durante el camino. Discontinuidades en el plano de referencia podrían causar ruido adicional en el circuito, incrementar la interferencia electromagnética (EMI por sus siglas en inglés). e incrementar la impedancia del plano.

- Las señales críticas del sistema deben ser incorporadas en una capa embebida interna o externa.

- De ser posible, evite diseñar tarjetas que se acerquen a los límites de manufactura.

- Use diferentes anchos de trazo para cada valor de impedancia en cada capa.

- Permita que el fabricante ajuste el stack-up dentro de ciertos márgenes de diseño, para poder lograr las impedancias.

- En lo posible evite planos de poder y tierra cruzados, esto incrementa la impedancia del plano.

- Se obtienen mejores resultados si se limita a dos el número de capas de señal adyacentes a un plano de referencia (tierra o voltaje).

- Si se tienen más de dos capas de señal adyacentes a un plano de referencia las señales entre dos capas de señal adyacentes deberán ser ruteadas ortogonalmente.

Aún más importante que saber el cálculo de la impedancia es conocer el efecto de cada uno de los factores que la determinan. Tener comprensión sobre esto ayudará a optimizar la estructura interna teniendo mejores trazos y poder controlar de mejor manera la impedancia de la línea de transmisión.

#### b. Interferencia Electromagnética.

La interferencia electromagnética es la perturbación que ocurre en cualquier circuito, componente o sistema eléctrico causado por una fuente de radiación electromagnética externa al mismo. La fuente de la interferencia puede ser cualquier objeto, artificial o natural, que posea corrientes eléctricas que varíen rápidamente como un circuito eléctrico, el Sol o las auroras boreales. (Fundación Wikimedia, Inc., 2013)

Los requerimientos de EMI son generalmente establecidos por agencias regulatorias. Los productos deben cumplir las especificaciones de radiación y conducción de emisiones, así como, la susceptibilidad a la radiación y la conducción antes de ser introducido en un mercado. Algunas de las agencias regulatorias son las FCC Class A/B, EN 55022 Class A/B, VCCI Class 1/2, etc. (IPC, 2004)

Las EMI pueden provenir tanto de fuentes terrestres como extraterrestres (satélites, naves espaciales). Las fuentes de ruido EMI son debidas fundamentalmente a emisores de comunicaciones y navegación (banda comercial, comunicaciones de navegación aérea y radares) y a equipos industriales y de consumo, o incluso las explosiones nucleares, todas ellas debidas al hombre. Pero también hay que tener en cuenta fuentes de interferencia electromagnética externas naturales, tales como rayos, descargas electrostáticas, ruido solar y cósmico entre otros

Figura 29.- Fuentes de Radiaciones Electromagnéticas.

### **6.- Participación Profesional**

Durante el tiempo que he laborado en la empresa, he desempeñado actividades como ingeniero de diseño de PCB's, donde una de las actividades que realizo es la propuesta de stack-ups para prototipos de plataformas y con el tiempo he adquirido las habilidades analíticas para el diseño de stack-ups.

Sin embargo también he aprendido que existen factores de tecnología para la manufactura que cada empresa maneja de manera particular, teniendo como resultado variaciones en los parámetros del stack-up. Es por ello que recomiendo una estrecha comunicación con el fabricante para optimizar el diseño.

## 7.- Resultados y Aportaciones

El presente documento es una descripción del proceso que se lleva a cabo durante el diseño del stack-up de un PCB. Esto con la finalidad de permitir que otros ingenieros de diseño cuenten con las bases y los conceptos necesarios a tener en cuenta a la hora de la implementación de prototipos en un PCB.

#### Bibliografía

- Barceló, M. (2008). Una Historia de la Informática. Editorial OUC.

- Khandpur, R. S. (2005). *Printed Circuit Boards: Design, Fabrication, Assembly and Testing*. Nueva Delhi: Tata-McGraw-Hill.

- Mitzner, K. (2009). Complete PCB design using OrCAD Capture and PCB editor. Elsevier.

- Rogers Corporation. (2011, Febrero). Copper Foild for High Frecquency Materials. Chandler, AZ, EEUU.

- Williams, T. I. (1987). Historia de la tecnología (II). In T. I. Williams, *Historia de la tecnología* (II). Siglo XXI de España Editores.

#### Mesografía

- Advanced Circuits. (2013). *PCB Overview*. Retrieved Diciembre 2013, from 4PCB: http://www.4pcb.com/pcb/

- Altera Corporation. (2010, Octubre). www.Altera.com. Retrieved Septiembre 2013, from Literature: http://www.altera.com/literature/an/an613.pdf

- Aspen Labs, LLC. (2013). *toolbox:microstrip-impedance*. Retrieved from microstrip-impedance: http://www.eeweb.com/toolbox/microstrip-impedance

- Brainiac. (2013). *ASUS Z8 SERIES DUAL XEON MOTHERBOARDS* + 2x W5580. Retrieved Diciembre 15, 2013, from www.TREADLAYERS.com: http://www.treadlayers.com/PC Hardware/Motherboards/Asus/Z8/Z8s W5580 1.shtml

- Cohen, P. (2010). Conceptos y terminología utilizada en Circuitos Impresos (PCB). Viña del Mar, Chile. Retrieved from http://www.pcb.electrosoft.cl/04-articulos-circuitos-impresos-desarrollo-sistemas/01-conceptos-circuitos-impresos/conceptos-circuitos-impresos-pcb.html

- Fundación Wikimedia, Inc. (2013, Nov 5). *Diafonía*. Retrieved from http://es.wikipedia.org: http://es.wikipedia.org/wiki/Diafon%C3%ADa

- Fundación Wikimedia, Inc. (2014, Enero 27). *Conductor eléctrico*. Retrieved from Wikipedia®: http://es.wikipedia.org/wiki/Conductor\_el%C3%A9ctrico

- Fundación Wikimedia, Inc. (2013, septiembre 29). wiki:Interferencia\_electromagn%C3%A9tica.

Retrieved from Interferencia\_electromagn%C3%A9tica:

http://es.wikipedia.org/wiki/Interferencia\_electromagn%C3%A9tica

- Fundación Wikipedia Inc. (2013, Octubre 20). Gerber(formato de fichero). Retrieved from http://es.wikipedia.org/wiki/Gerber\_(formato\_de\_fichero)

- Gendreaumicrosystems.com. (2012). Tips / Best Practices. Rustburg, VA, EEUU.

- Intel Corporation. (2000, Junio). *Intel*® *815E Chipset Platform*. (C. ©. 2000, Ed.) Retrieved Enero 2014, from http://download.intel.com/design/chipsets/designex/: http://download.intel.com/design/chipsets/designex/29823401.pdf

- IPC. (2000, Junio). Design Guide for High desity Interconnects (HDI) and Microvias. Borthbrook, IL, EEUU. Retrieved from www.ipc.org

- IPC. (2004, Marzo). Design Guide for High-Speed Controlled Impedance Circuit Boards. NothBrook, IL, EEUU. Retrieved from http://www.huishangpcb.com/userfiles/IPC-

- 2141A-

- 2004\_%E9%98%BB%E6%8A%97%E5%8F%97%E6%8E%A7%E9%AB%98%E9%80 %9F%E7%94%B5%E8%B7%AF%E6%9D%BF%E8%AE%BE%E8%AE%A1%E6%8 C%87%E5%8D%97.pdf

- IPC. (2011, Octubre). Term and Definitions. *IPC-T-50J*. Northbrook, IL, EEUU. Retrieved from http://www.docstoc.com/docs/77852677/IPC-T-50-TERMS-AND-DEFINITIONS

- IPC. (2013, Septiembre). IPC Standards Tree. Bannockburn, IL, EEUU.

- Isola-Group. (2013). *Products Positioning*. Retrieved Diciembre 15, 2013, from Isola-Group: http://www.isola-group.com/product-positioning#.Uq2e16yA2Uk

- Ken Gilleo, P. (2014, Enero). *The First 105 Years of Flexible Circuitry*. Retrieved from http://magazines007.com: http://magazines007.com/pdf/KGilleo.pdf

- Newbury Electronics LTD. (2013). *Fabricacion Electronica: La historia mas profunda del PCB*. Retrieved Diciembre 15, 2013, from PCBTrain.es/blog:

- http://www.pcbtrain.es/blog/fabricacion-electronica/la-historia-mas-profunda-del-pcb/

- Reid, P. (2012, Marzo 15). *Columns:Reid on Reliability: Design and Construction Effects on PWB Reliability*. Retrieved from Reid on Reliability: Design and Construction Effects on PWB Reliability:

- http://www.pcbdesign007.com/pages/columns.cgi?clmid=46&artid=82487&\_pf\_=1 WebAcademia. (2013). *Articulos-utiles: articulo 100667*. Retrieved Diciembre 15, 2013, from WebAcademia.com: http://centrodeartigos.com/articulos-utiles/article\_100557.html

## **Tabla de Contenidos**

| Agradecimientos                  | 3  |

|----------------------------------|----|

| Análisis y Metodología           | 25 |

| Bibliografía                     | 45 |

| Componentes de un PCB            | 12 |

| Definición del Problema          | 24 |

| Índice                           | 5  |

| Introducción                     | 6  |

| Marco Teórico                    | 10 |

| Breve Historia del PCB           | 10 |

| Fabricación y ensamblado del PCB | 22 |

| Integridad de Señales de un PCB  | 17 |

| Objetivo                         | 8  |

| Participación Profesional        |    |

| Referencias Biográficas          | 49 |

| Resultados y Aportaciones        | 44 |

| Resumen                          | 4  |

| Tabla de Contenidos              | 47 |

| Tabla de Figuras                 | 48 |

# Tabla de Figuras

| Figura 1Productos de Isola para aplicaciones digitales de alta velocidad           | 6    |

|------------------------------------------------------------------------------------|------|

| Figura 2Tarjeta Raspberry Pi                                                       |      |

| Figura 3Tarjeta ASUS Z8NA-D para procesadores Intel® Xeon™                         | 9    |

| Figura 4 Tipos de líneas diferenciales en un PCB.                                  |      |

| Figura 5Ajuste de longitud en el par diferencial.                                  | . 14 |

| Figura 6Sección transversal de las interconexiones típicas (Reid, 2012)            | . 15 |

| Figura 7Perforación, pad y antipad de una vía                                      |      |

| Figura 8 Diferentes tipos y tamaños de componentes SMD y THM                       | . 17 |

| Figura 9 Tarjeta con ángulos suavizados (izquierdo) y ángulos rectos (derecha)     |      |

| Figura 10Disposición de elementos para la medida de telediafonía                   | . 20 |

| Figura 11 Disposición de elementos para la medida de paradiafonía                  | . 21 |

| Figura 12 Solución del trazado de la memoria del sistema para 2-DIMM               | . 22 |

| Figura 13 Proceso de manufactura del cobre rolado (Rogers Corporation, 2011)       | . 26 |

| Figura 14Proceso de manufactura del cobre electro-depositado (Rogers Corporatio    | n,   |

| 2011)                                                                              | . 26 |

| Figura 15 Comparación de la rugosidad entre una lámina de cobre rolado y una de    |      |

| cobre electro-depositado estándar (Rogers Corporation, 2011)                       | . 27 |

| Figura 16BGA de 100 pines                                                          |      |

| Figura 17Break-out de la tercera hilera de pines del BGA                           | . 29 |

| Figura 18 Break-out de los pines más internos del BGA                              | . 29 |

| Figura 19 Ejemplo de un stack-up de 4 capas (Altera Corporation, 2010)             | . 30 |

| Figura 20Ejemplo de un stack-up de 6 capas (Altera Corporation, 2010)              | . 31 |

| Figura 21 Trazos de pares diferenciales (gendreaumicrosystems.com, 2012)           | . 31 |

| Figura 22 Composición de un PCB (Altera Corporation, 2010)                         | . 32 |

| Figura 23 Emisiones Electromagnéticas emitidas por los circuitos                   | . 34 |

| Figura 24 Comparación que podríamos realizar entre un cable coaxial y un PCB       | . 35 |

| Figura 25 Calculadora de impedancias en línea. (Aspen Labs, LLC, 2013)             | . 36 |

| Figura 26 Trazo microstrip.                                                        | . 37 |

| Figura 27 Gráfica donde se muestra el impacto de diferentes factores a la impedane | cia  |

| para microstip                                                                     | . 38 |

| Figura 28 Gráfica donde se muestra el impacto de diferentes factores a la impedand | cia  |

| para stipline                                                                      | . 39 |

| Figura 29 Fuentes de Radiaciones Electromagnéticas                                 | . 42 |

#### Referencias Biográficas

\_\_\_\_

<sup>&</sup>lt;sup>1</sup> Albert Hanson, Inventor Alemán cuyas patentes de 1902 y 1903 en Alemania y Gran Bretaña son las precursoras de los circuitos multi-capas que permiten una mayor densidad de conexiones eléctricas. (Ken Gilleo, 2014)

<sup>&</sup>lt;sup>2</sup> Thomas Edison. (Milan, Ohio, 1847-1931) fue un inventor estadounidense que registró más de mil patentes, Edison contribuyó a cimentar las bases de las industrias: eléctricas, de comunicación telefónica fija, y del cine. Thomas Edison experimentó con métodos químicos de conductores de placas en el papel de lino en 1904.

<sup>&</sup>lt;sup>3</sup> Arthur Berry. Ingeniero Británico que en el año de 1913 patentó un método de impresión y grabado para los circuitos electrónicos.

<sup>&</sup>lt;sup>4</sup> Max Ulrich Schoop. (1903-1990) fue un inventor suizo que en 1914 descubrió la proyección térmica con llama, también conocida como "flame spray" o metalización. Se trata de que una llama de oxi-combustible funda el metal de aportación (polvo o hilo) y por medio de un gas propulsor proyecta las partículas líquidas sobre el sustrato. Este procedimiento se suele emplear para protección contra la corrosión (cinc, aleaciones de aluminio,...) y contra el desgaste, pero también ayudaron a la tecnología de la elaboración de PCB.

<sup>&</sup>lt;sup>5</sup> Charles Ducarse. en 1927 patentó un método de galvanoplastia de patrones de circuitos.

<sup>&</sup>lt;sup>6</sup> J.A. Sargrove. (1906-1974) ingeniero inglés, pionero de la automatización. Experimentó con la idea de crear circuitos mediante la atomización de metal sobre una placa de Bakelita. Fue capaz de crear placas de bakelita con resistencias, condensadores y bobinas, así como las conexiones eléctricas entre ellos.

<sup>&</sup>lt;sup>7</sup> Moe Abramson y Stanilus F. Danko en 1949 de la United States Army Signal Corps, desarrollaron el proceso de auto-ensamblaje, donde las patas de los componentes del circuito electrónico eran insertadas en una lámina de cobre con el patrón de interconexión y luego eran soldadas. Con el desarrollo de la laminación en tarjetas y técnicas de grabados este concepto evolucionó en el proceso estándar de fabricación de circuitos impresos usado en la actualidad.

<sup>&</sup>lt;sup>8</sup> Jack Kilby. (1923-2005) físico e ingeniero nacido en los EEUU que formó parte del proceso de invención del circuito electrónico mientras trabajaba en Texas Instruments en 1958. Fue galardonado con el Premio Nobel de Física en el año 2000, es considerado junto con Robert Noyce, como el inventor del circuito integrado o microchip. También es inventor de la calculadora de bolsillo y la impresora térmica.