### centro de educación continua división de estudios superiores facultad de ingeniería, unam

## A LOS ASISTENTES A LOS CURSOS DEL CENTRO DE EDUCACION CONTINUA

Las autoridades de la Facultad de Ingeniería, por conducto del Jefe del Centro de Educación Continua, otorgan una constancia de asistencia a quienes cumplan con los requisitos establecidos para cada curso. Las personas que deseen que aparezca su título profesional precediendo a que nombre en la constancia, deberán entregar copia del mismo o de su cedula a más tardar el SEGUNDO DIA de clases, en las oficinas del Centro con la señorita encargada de inscripciones.

El control de asistencia se llevará a cabo a través de la persona encar gada de entregar las notas del curso. Las inasistencias serán computadas por las autoridades del Centro, con el fin de entregarle constancia solamente a elos alumnos que etengan un mínimo del 80% de asistencia.

Serrecomienda\_a\_los-asistentes-participarzactivamente-con\_sus\_ideas\_y experiencias; pues-los-cursos que-ofrece-el-Centro-están-planeados para-que-los-profesores:expongan=una tesis, pero-sobre todo; para-que-coordi-nen-las-opiniones-de todos-los-interesados-constituyendo-verdaderos se-minarios...

Es muy importante que todos los asistentes llenen y entregen su hoja - de inscripción al inicio del curso. Las personas comisionadas por alguna institución deberán pasar a inscribirse en las oficinas del Centro en la misma forma que los demás asistentes, entregando el oficio respectivo.

Con objeto de mejorar los servicios que el Centro de Educación Continua ofrece, al final del curso se hará una evaluación a tráves de un cues-tionario diseñado para emitir juicios anónimos por parte de los asistentes.

# centro de educación continua

ingeniería,

de estudios superiores división facultad d e

unam

| CUESTIONARIO PARA EL DIRECTORIO GENERAL                                                                              | PARA USO EXCLUSIVO DEL C E C                                                                |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                                                                                                      | ALTA SI MODIFICACION SI                                                                     |

| 1,— INSTRUCCIONES GENERALES.                                                                                         | <u> </u>                                                                                    |

|                                                                                                                      | ara contestar las preguntas en las líneas ó en os semicuadros escriba, letras y en los cua- |

| B. — Escriba un solo caracter por di                                                                                 | ros pondrá números según sea la respuesta                                                   |

| NOTA : No se haga ninguna anotación                                                                                  | ue se pide,<br>n en los cuadros sombreados.                                                 |

|                                                                                                                      |                                                                                             |

| NOMBRE DEL CURSO :                                                                                                   | FOLIO: 1 5                                                                                  |

|                                                                                                                      |                                                                                             |

| NOTA : Separe mediante una coma (,) el (los)  2.— REGISTRO FEDE RAL DE CAUS.:  42  AÑO MES DIA 51  4.— TELEFONO  5.— | 3 CEDULA PROFESIONAL:                                                                       |

| 7 DIRECCION PARTICULAR :                                                                                             |                                                                                             |

| CALLE, NUMERO Y N                                                                                                    | NUMERO INTERIOR. 41                                                                         |

| COLONIA Y/O CIU                                                                                                      | JDAD. ZONA POSTAL 72 73                                                                     |

| ESTADO 74 76                                                                                                         | 8- TITULO PROFESIONAL 76 77                                                                 |

ESPECIALIDAD

|                      | •                            |                |           |            | ·          |

|----------------------|------------------------------|----------------|-----------|------------|------------|

| 10.— DIRECCION DE OF | ICINA:<br>CALLE, NUMERO Y NU | JMERO INTERIOR |           |            | 41         |

| 42                   | COLONIA Y/O CIUD             | )AD.           |           | ZON<br>POS | TAL: 72 73 |

| ESTAC                | DO 74 76                     |                |           | A 3        | M 7        |

| 17.— ASOCIACIONES A  | LAS QUE PERTENECE :          |                | •         |            |            |

| PRINCIPAL :          |                              |                |           |            |            |

| OTRAS:               |                              |                |           |            |            |

| ,                    |                              | [              | 2 13      | A 4        | M 8        |

|                      |                              |                |           |            |            |

|                      | DE<br>CHA DE ELABORACION     | _DE 19         |           | FIRMA      | · ~ -      |

|                      |                              |                |           |            |            |

|                      | RA USO EXCLUSIVO DEL O       | ENTRO DE EDUC  | ACION CON | TINUA      |            |

| CODIFICO:            | REVISO:                      | ОВ             | SERVAC    | IONES:     |            |

|                      |                              |                |           |            |            |

| Fecha        | ,<br>Duración | INTRODUCCION A LAS MINICOMPUTADORAS (FDP-11)<br>1979 | Profesor                                 |

|--------------|---------------|------------------------------------------------------|------------------------------------------|

| lulio 6      | 17 a 21 h     | I ELEMENTOS DE UNA COMPUTADORA                       | ING. MARCIAL PORTILLA<br>ROBERTSON       |

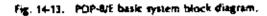

| " 7          | 9 a 13 h      | II ARQUITECTURA DE PDP-11                            | DR. ADOLFO GUZMAN<br>ARENAS              |

| " 7          | 13 a 14 h     | COMIDA -                                             |                                          |

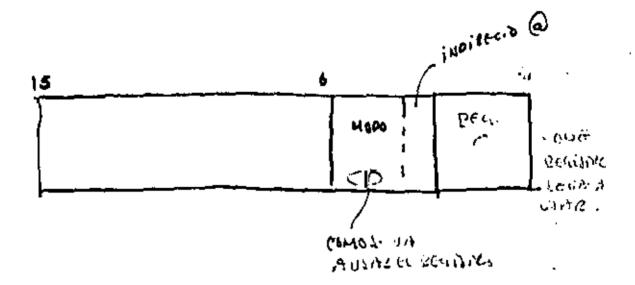

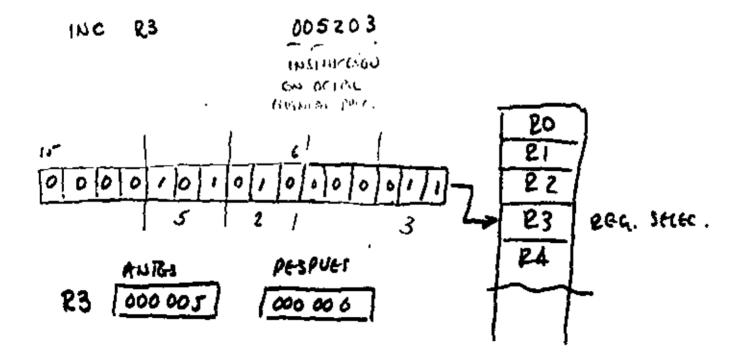

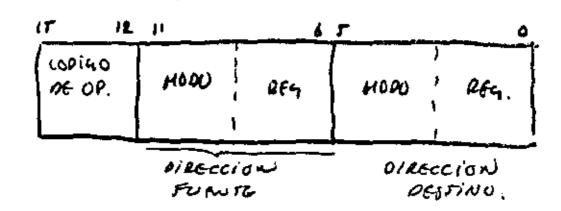

| " 7          | 14 a 18 h     | III MODOS DE DIRECCIONAMIENTO                        | ING. LUIS CORDERO BARBOA                 |

| " 13         | 17 a 21 h     | IV CONJUNTO DE INSTRUCCIONES                         | M. EN C. MARCIAL PORTILLA<br>ROBERTSON   |

| '' 14        | 9 a 13 h      | IV CONJUNTO DE INSTRUCCIONES                         | FI 17 +1                                 |

| " 14         | 13 a 14 h     | COMIDA .                                             | •                                        |

| " 14         | 14 a 18 h     | V MANEJO DE SUBRUTINAS                               | DR. ADOLFO GUZMAN<br>ARENAS              |

| " 20         | 17 a 21 h     | VI MANEJO DE ENTRADA/SALIDA                          | ING. DANIEL RIOS ZERTUCHE                |

| " 21         | 9 a 13 h      | LABORATORIO (Lab.de Computación, F.I.)               | ING. LUIS CORDERO BARBOA                 |

|              | 13 a 14 h     | COMIDA                                               |                                          |

|              | 14 a 18 h     | LABORATORIO                                          | 11 11 11 11                              |

| " <b>2</b> 7 | 17 a 21 h     | VII APLICACIONES                                     | DR. VICTOR GEREZ GREISER                 |

| " <b>2</b> 8 | 9 a 13 h      | LABORATORIO (Lab. de Computación, F.I.)              | ING, DANIEL RIOS ZERTUCHE                |

|              | 13 a 14 h     | COMIDA                                               |                                          |

|              | 14 a 15 h     | LABORATORIO .                                        | tt n · · · · · · · · · · · · · · · · · · |

| ¹ nd         | 00            |                                                      |                                          |

|   |  |  | ~ |

|---|--|--|---|

|   |  |  |   |

| · |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

# DIRECTORIO DE PROFESORES DEL CURSO INTRODUCCION A LAS MINICOMPUTADORAS (PDP-11) 1979.

ING. LUIS CORDERO BARBOA

Jefe de Laboratorio de Computación

Facultad de Ingeniería

UNAM

México 20, D.F.

Tel. 550.52.15 Ext. 4750

DR. VICTOR GEREZ GREISER Profesor Titular Ingeniería Mecánica y Electrica Facultad de Ingeniería UNAM México 20,D.F. Tel. 550,52,15 Ext.3746

DR. ADOLFO GUZMAN ARENAS Investigador Instituto de Investigaciones en Matemáticas Aplicadas y en Sistemas UNAM México 20, D.F. Tel. 550. 52. 15 Ext. 4584 y 4585

M. EN C. MARCIAL PORTILLA ROBERTSON (Coordinador)

Jefe de la Sección de Computación

Edificio de Ingeniería Mecánica y Eléctrica

Facultad de Ingeniería

UNAM

México 20, D.F.

Tel.550.52.15 Ext.3746

ING. DANIEL RIOS ZERTUCHE ORTUÑO

Jefe del Porte Técnico

Coordinación de Informática

S.H.C.P.

Palacio Nal. Edif. 6-2°

México 1,D.F.

Tel. 522, 37, 81

|          |  | 1   |

|----------|--|-----|

|          |  | I   |

|          |  | 1   |

|          |  | I   |

|          |  |     |

|          |  | I   |

| <b>¢</b> |  | . 1 |

|          |  | 1   |

|          |  |     |

|          |  | I   |

|          |  | 7   |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

|          |  |     |

CURSO: INTRODUCCION A LAS MINICOM-PUTADORAS (PDP-11) MANT. DEL INTERES (AMENJDAD, FACILIDAD DE EXPRESION, COMU NICACION CON LOS ASISTENTES) EFICIENCIA EN EL USO DE AYUDAS AUDIOVISUALES DOMINIO DEL TEMA FECHAS: Del 6 al 28 de Julio, 1979. Elementos de una Computadora(Portilla) ^rquitectura de PDP-11 (Guzmán) Modos de Direccionamiento (Cordero) Conjunto de Instrucciones (Portilla) Manejo de subrutinas (Guzmán) Manejo de entrada/salida (Ríos) Laboratorio (Cordero) Aplicaciones (Gerez) Laboratorio (Ríos) escala de Evaluaçión del 1 al 10 'enas. 27, VI, 79.

|   |   | • |  |  |

|---|---|---|--|--|

|   |   |   |  |  |

| ~ | • |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

|   |   |   |  |  |

### EVALUACION DEL CURSO

|    | CONCEPTO                                        | EVALUACION |

|----|-------------------------------------------------|------------|

| 1. | APLICACION INMEDIATA DE LOS CONCEPTOS EXPUESTOS |            |

| 2. | CLARIDAD CON QUE SE EXPUSIERON LOS TEMAS        |            |

| •  | GRADO DE ACTUALIZACION LOGRADO CON EL CURSO     |            |

| 4. | CUMPLIMIENTO DE LOS OBJETIVOS DEL CURSO         |            |

| 5. | CONTINUIDAD EN LOS TEMAS DEL CURSO              |            |

| 6. | CALIDAD DE LAS NOTAS DEL CURSO                  |            |

| 7. | GRADO DE MOTIVACION LOGRADO CON EL CURSO        |            |

ESCALA DE EVALUACION DE 1 A 10

| <b>-</b> - |  |  |  |  |

|------------|--|--|--|--|

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

|            |  |  |  |  |

| . 1 | ¿Qué le pareció el             | ambiente del Centro    | de Educación Continua?                      |

|-----|--------------------------------|------------------------|---------------------------------------------|

|     | Muy agradable 🔙                | Agradable [            | Desagradable [                              |

| 2.  | Medio de comunicad             | ción por el que se er  | iteró del curso:                            |

|     | Periódico<br>Excélsior 🔲       | Periódico<br>Novedades | Folleto del<br>Curso                        |

|     | Cartel  mensual                | Radio<br>Universidad   | Comunicación carta, teléfo no, verbal, etc. |

| 3.  | Medio de transpor              | te utilizado para ver  | nir al Palacio de Minerfa;                  |

|     | Automóvil<br>particular        | Metro                  | Otro medio                                  |

| ₽.  | ¿Qué cambios haría             | usted en el program    | na para tratar de perfecci <u>o</u>         |

|     | :Recomendaria al ca            | irso a otras personas  | 3? Si No No                                 |

| •   | ZNCComendalia el co            | ilso a otras personas  | s: 31[_] NO [_]                             |

| 5.  | ¿Qué curso le gusta<br>nua?    | eria que ofreciera el  | Centro de Educación Cont <u>i</u>           |

| ' - | ¿Qué servicios dese<br>cursos? | aría que tuviese el    | CEC para los asistentes a                   |

|     |                                |                        |                                             |

| 3.  | Otras sugestiones:             | -                      | •                                           |

|     |                                |                        |                                             |

|     |                                | ·                      |                                             |

|  |   | • |   |

|--|---|---|---|

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   | I |

|  | • |   |   |

|  |   |   | 1 |

|  |   |   |   |

|  |   |   | I |

|  |   |   |   |

|  |   |   | I |

|  |   |   |   |

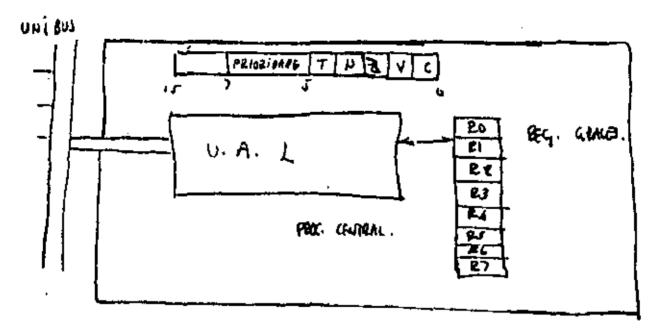

INTRODUCCION A LAS MINICOMPUTADORAS (PDP-11)

CAPITULO 1: ELEMENTOS DE UNA COMPUTADORA

M. en C. MARCIAL PORTILLA R. JULIO-79

1

# SYSTEMS PROGRAMMING JOHN J. DONOVAN

### background

This book has two major objectives: to teach procedures for the design of software systems and to provide a basis for judgement in the design of software. To facilitate our task, we have taken specific examples from systems programs. We discuss the design and implementation of the major system components.

What is systems programming? You may visualize a computer as some sort of beast that obeys all commands. It has been said that computers are basically people made out of metal or, conversely, people are computers made out of flesh and blood. However, once we get close to computers, we see that they are basically machines that follow very specific and primitive instructions.

In the early days of computers, people communicated with them by on and off switches denoting primitive instructions. Soon people wanted to give more complex instructions. For example, they wanted to be able to say X = 30 = Y; given that Y = 10, what is X? Present day computers cannot understand such language without the aid of systems programs. Systems programs (e.g., compilers, loaders, macro processors, operating systems) were developed to make computers better adapted to the needs of their users. Further, people wanted more assistance in the mechanics of preparing their programs.

Compilers are systems programs that accept people-like languages and translate them into machine language. Loaders are systems programs that prepare machine language programs for execution. Macro processors allow programmers to use abbreviations. Operating systems and file systems allow flexible storing and retrieval of information (Fig. 1-1).

There are over 100,000 computers in use now in virtually every application. The productivity of each computer is heavily dependent upon the effectiveness, efficiency, and sophistication of the systems programs.

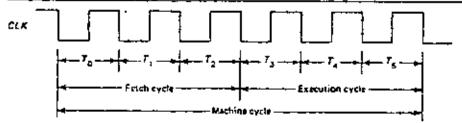

In this chapter we introduce some terminology and outline machine structure and the basic tasks of an operating system.

C.

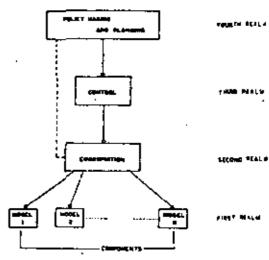

FIGURE 1.1 Foundations of systems programming

### 1.1 MACHINE STRUCTURE

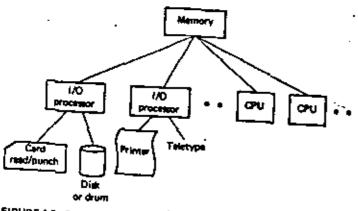

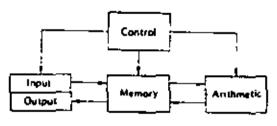

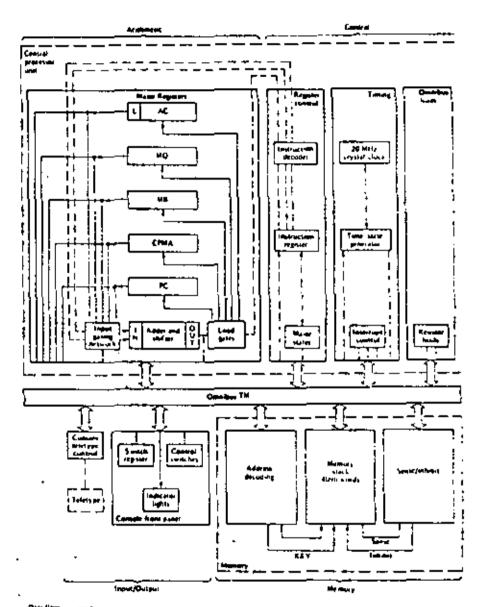

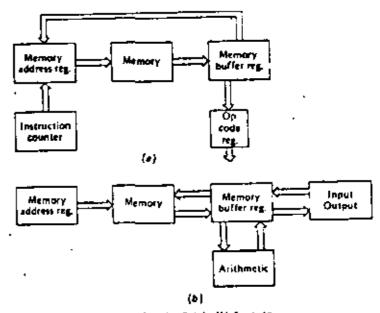

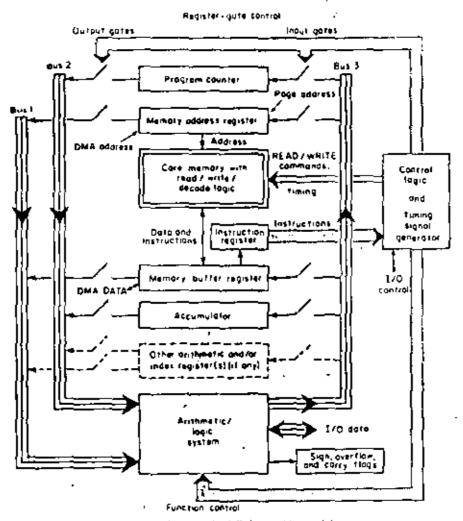

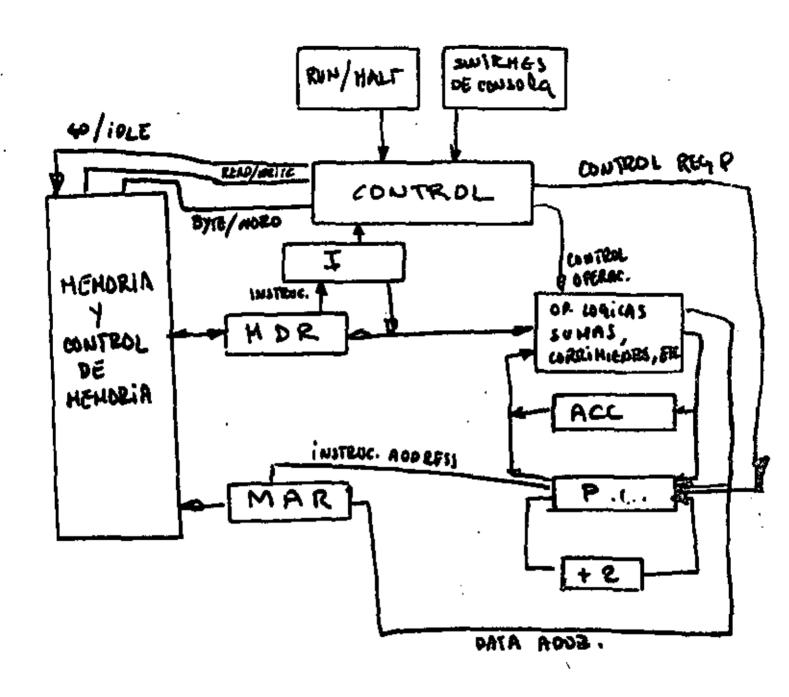

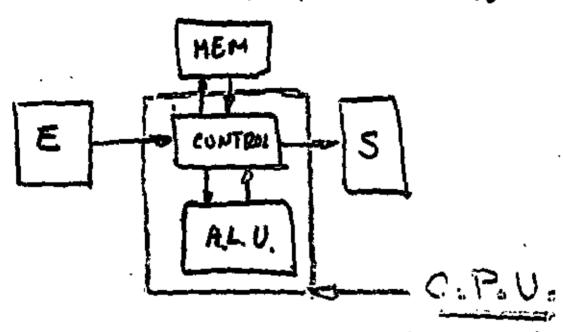

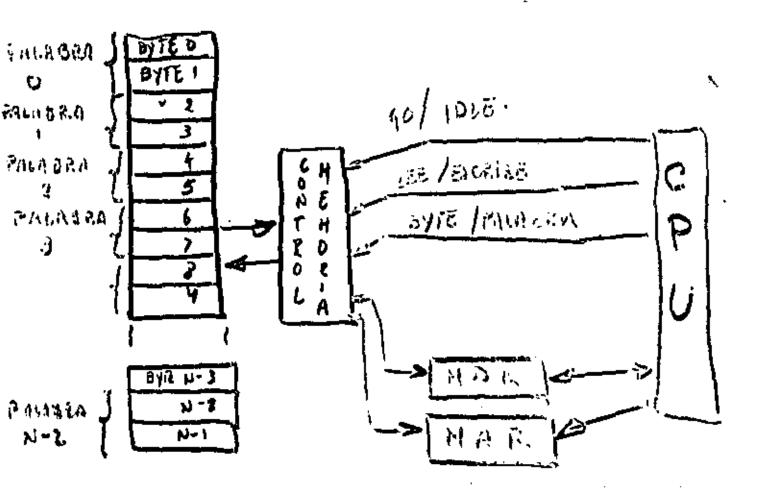

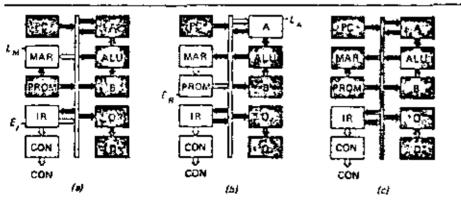

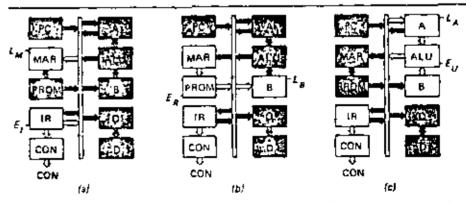

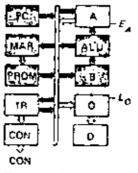

We begin by sketching the general hardware organization of a computer system (Fig. 1.2).

FIGURE 1.2 General hardware organization of a computer system

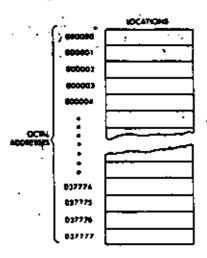

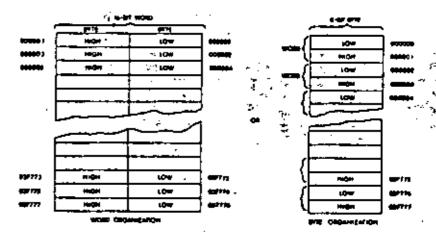

Memory is the device where information is stored. Processors are the devices that operate on this information. One may view information as being stored in the form of ones and zeros. Each one or zero is a separate binary digit called a bir. Bits are typically grouped in units that are called words, characters, or bytes. Memory locations are specified by addresses, where each address identifies a specific byte, word, or character.

The contents of a word may be interpreted as data (values to be operated on) or instructions (operations to be performed). A processor is a device that performs a sequence of operations specified by instructions in memory. A program (or procedure) is a sequence of instructions.

Memory may be thought of as mailboxes containing groups of ones and zeros. Below we depict a series of memory locations whose addresses are 10,000 through 10,002.

| Address | Contents            | 1 |

|---------|---------------------|---|

| 10,000  | 0000 0000 0000 0001 |   |

| 10,001  | 0011 0000 0000 0000 |   |

| 10,002  | 0000 0000 0000 0100 | N |

An IBM 1130 processor treating location 10,001 as an instruction would interpret its contents as a "halt" instruction. Treating the same location as numerical data, the processor would interpret its contents as the binary number 0011 0000 0000 0000 (decimal 12,288). Thus instructions and data share the same storage inedium.

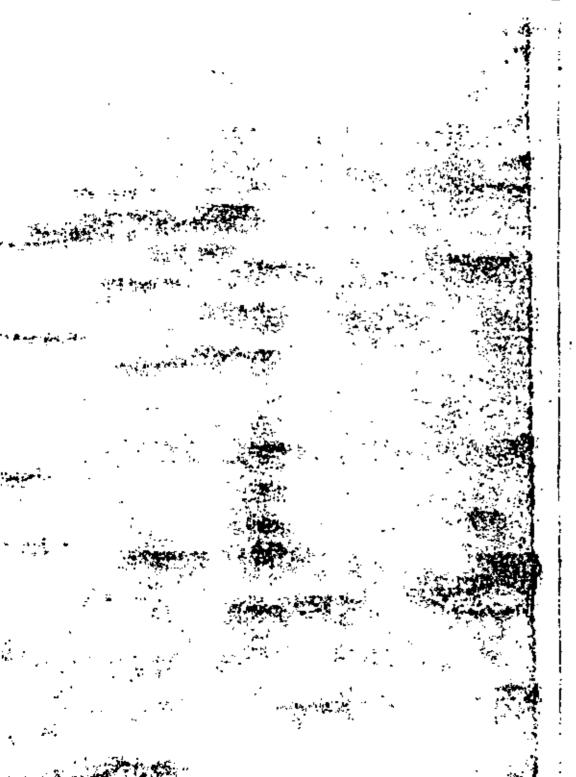

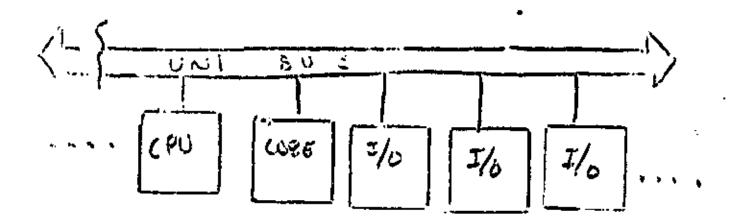

Information in memory is coded into groups of bits that may be interpreted as characters, instructions, or numbers. A code is a set of rules for interpreting groups of bits, e.g., codes for representation of decimal digits (BCD), for characters (EBCDIC, or ASCII), or for instructions (specific processor operation codes). We have depicted two types of processors: Input/Output (I/O) processors and Central Processing Units (CPUs). The I/O processors are concerned with the transfer of data between memory and peripheral devices such as disks, drows, printers, and typewriters. The CPUs are concerned with manipulations of data stored in memory. The I/O processors execute I/O instructions that are stored in memory; they are generally activated by a command from the CPU. Typically, this consists of an "execute I/O" instruction whose argument is the address of the start of the I/O processor (commonly called I/O channels).

The 1/O instruction set may be entirely different from that of the CPU and may be executed stynchronously (simultaneously) with CPU operation. Asynchronous operation of 1/O channels and CPUs was one of the earliest forms of multiprocessing. Multiprocessing means having more than one processes operating on the same memory simultaneously.

Since instructions, like data, are stored in memory and can be treated as data, by changing the bit configuration of an instruction — adding a number to it — we may change it to a different instruction. Procedures that modify themselves are

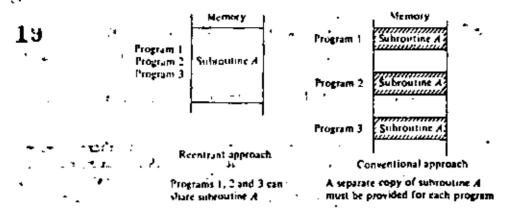

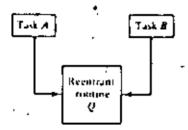

.

called impure procedures. Writing such procedures is poor programming practice. Other programmers find them difficult to read, and moreover they cannot be shared by multiple processors. Each processor executing an impure procedure modifies its contents. Another processor attempting to execute the same procedure may encounter different instructions or data. Thus, impure procedures are not readily reusable. A pure procedure does not modify itself, To ensure that the instructions are the same each time a program is used, pure procedures (re-centrant code) are employed.

# 1.2 EVOLUTION OF THE COMPONENTS OF A PROGRAMMING SYSTEM

### 1.2.1 Assemblers

Let us review some aspects of the development of the components of a programming system.

At one time, the computer programmer had at his disposal a basic machine that interpreted, through hardware, certain fundamental instructions. He would program this computer by writing a series of ones and zeros (machine language), place them into the memory of the machine, and press a button, whereupon the computer would start to interpret them as instructions.

Programmers found it difficult to write or read programs in machine language. In their quest for a more convenient language, they began to use a mnemonic (symbol) for each machine instruction, which they would subsequently translate into machine language. Such a mnemonic machine language is now called an assembly language. Programs known as assemblers were written to automate the translation of assembly language into machine language. The input to an assembler program is called the source program; the output is a machine language translation (object program).

### 1.2.2 Loaders

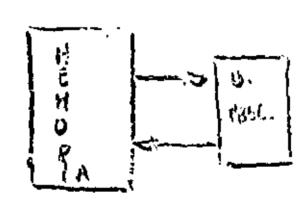

Once the assembler produces an object program, that program must be placed into memory and executed. It is the purpose of the loader to assure that object programs are placed in memory in an executable form.

The assembler could place the object program directly in memory and transfer control to it, thereby causing the machine language program to be executed.

However, this would waste core<sup>1</sup> by leaving the assembler in memory while the user's program was being executed. Also the programmer would have to retranslate his program with each execution, thus wasting translation time. To overcome the problems of wasted translation time and wasted memory, systems programmers developed another component, called the loader.

A loader is a program that places programs into memory and prepares them for execution. In a simple loading scheme, the assembler outputs the machine language translation of a program on a secondary storage device and a loader is placed in core. The loader places into memory the machine language version of the user's program and transfers control to it. Since the loader program is much smaller than the assembler, this makes more core available to the user's program.

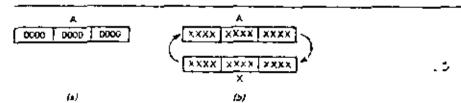

The realization that many users were writing virtually the same programs led to the development of "ready-made" programs (packages). These packages were written by the computer manufacturers or the users. As the programmer became more sophisticated, he wanted to mix and combine ready-made programs with his own. In response to this demand, a facility was provided whereby the user could write a main program that used several other programs or subroutines. A subroutine is a body of computer instructions designed to be used by other routines to accomplish a task. There are two types of subroutines: closed and open subroutines. An open inbroutine or macro definition is one whose code is inserted into the main program (flow continues). Thus if the same open subroutine were called four times, it would appear in four different places in the calling program. A closed subroutine can be stored outside the main routine, and control transfers to the subroutine. Associated with the closed subroutine are two tasks the main program must perform: transfer of control and transfer of data.

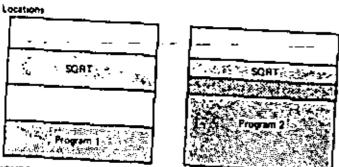

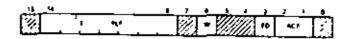

Initially, closed subroutines had to be loaded into memory at a specific address. For example, if a user wished to employ a square root subroutine, he would have to write his main program so that it would transfer to the location assigned to the square root routine (SQRT). His program and the subroutine would be assembled together. If a second user wished to use the same subroutine, he also would assemble it along with his own program, and the complete machine language translation would be loaded into memory. An example of core allocation under this inflexible loading scheme is depicted in Figure 1.3, where core is depicted as a linear array of locations with the program areas shaded.

<sup>&</sup>lt;sup>1</sup>Main memory is typically implemented as magnetic cores; hence memory and core are used armonymously.

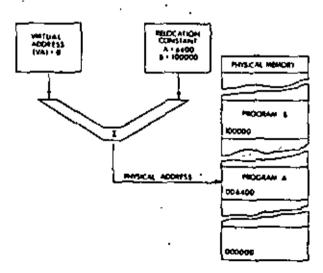

FIGURE 1.3 Example core allocation for absolute loading

Note that program I has "holes" in core. Program 2 overlays and thereby destroys part of the SQRT subroutine.

Programmers wished to use subroutines that referred to each other symbolically and did not want to be concerned with the address of parts of their programs. They expected the computer system to assign locations to their subroutines and to substitute addresses for their symbolic references.

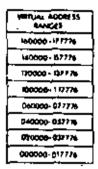

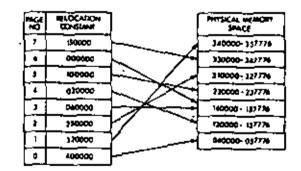

Systems programmers noted that it would be more efficient if subroutines could be translated into an object form that the loader could "relocate" directly behind the user's program. The task of adjusting programs so they may be placed in arbitrary core locations is called relocation. Relocating loaders perform four

- 1. Allocate space in memory for the programs (allocation)

- 2. Resolve symbolic references between object decks (linking)

- 3. Adjust all address-dependent locations, such as address constants, to correspond to the allocated space (relocation)

- 4. Physically place the machine instructions and data into memory (loading).

The various types of loaders that we will discuss ("compile-and-go," absolute. relocating, direct-linking, dynamic-loading, and dynamic-linking) differ primarily in the manner in which these four basic functions are accomplished.

The period of execution of a user's program is called execution time. The period of translating a user's source program is called assembly or compile time. Load time refers to the period of loading and preparing an object program for

### 1.2.3 Macros

To relieve programmers of the need to repeat identical parts of their program,

operating systems provide a macro processing facility, which permits the programmer to define an abbreviation for a part of his program and to use the abbreviation in his program. The macro processor treats the identical parts of the program defined by the abbreviation as a macro definition and caves the definition. The macro processor substitutes the definition for all occurrences of the abbreviation (macro call) in the program.

In addition to helping programmers abbreviate their programs, macro facilities have been used as general text handlers and for specializing operating systems to individual computer Installations. In specializing operating systems (systems generation), the entire operating system is written as a series of macro definitions. To specialize the operating system, a series of macro calls are written. These are processed by the macro processor by substituting the appropriate definitions, thereby producing all the programs for an operating system.

#### 1.24 Compilers

As the user's problems became more categorized into areas such as scientific, business, and statistical problems, specialized languages (high level languages) were developed that allowed the user to express certain problems concisely and easily. These high level languages - examples are FORTRAN, COBOL, ALGOL, and PL/I - are processed by compilers and interpreters. A compiler is a program that accepts a program written in a high level language and produces an object program. An interpreter is a program that appears to execute a source program as if it were machine language. The same name (FORTRAN, COBOL, etc.) is often used to designate both a compiler and its associated language.

Modern compilers must be able to provide the complex facilities that programmers are now demanding. The compiler must furnish complex accessing methods for pointer variables and data structures used in languages like PL/I. COBOL, and ALGOL 68. Modern compilers must interact closely with the operating system to handle statements concerning the hardware interrupts of a computer (e.g. conditional statements in PL/I).

#### 1.2.5 Formai Systems

A formal system is an uninterpreted calculus, it consists of an alphabet, a set of words called axioms, and a finite set of relations called rules of inference. Examples of formal systems are: set theory, boolean algebra, Post systems, and Backus Normal Form. Formal systems are becoming important in the design, implementation, and study of programming languages. Specifically, they can be

¢

### 1.3 EVOLUTION OF OPERATING SYSTEMS

Just a few years ago a FORTRAN programmer would approach the computer with his source deck in his left hand and a green deck of cards that would be a FORTRAN compiler in his right hand. He would:

- Place the FORTRAN compiler (green deck) in the card hopper and press

the load button. The computer would load the FORTRAN compiler.

- Place his source language deck into the card hopper. The FORTRAN compiler would proceed to translate it into a machine language deck, which was punched onto red cards.

- 4. Place his newly translated object deck in the card hopper. The loader would load it into the machine.

- Place in the card hopper the decks of any subroutines which his program called. The loader would load these subroutines.

- Finally, the forder would transfer execution to the user's program, which

might require the reading of data cards.

This system of multicolored decks was somewhat unsatisfactory, and there was strong motivation for moving to a more flexible system. One reason was that valuable computer time was being wasted as the machine stood idle during cardhandling activities and between jobs. (A job is a unit of specified work, e.g., an assembly of a program.) To eliminate this waste, the facility to batch jobs was provided, permitting a number of jobs to be placed together into the card hopper to be read. A batch operating system performed the task of batching jobs. For example the batch system would perform steps I through 6 above retrieving the FORTRAN compiler and loader from secondary storage.

As the demands for computer time, memory, devices, and files increased, the efficient management of these resources became more critical. In Chapter 9 we discuss various methods of managing them. These resources are valuable, and inefficient management of them can be costly. The management of each resource has evolved as the cost and sophistication of its use increased.

In simple batched systems, the memory resource was allocated totally to a

single program. Thus, if a program did not need the entire memory, a portion of that resource was wasted. Multiprogramming operating systems with pertitioned core memory were developed to circumvent this problem. Multiprogramming allows multiple programs to reside in separate areas of core at the same time. Programs were given a fixed portion of core (Multiprogramming with Fixed Tasks (MFT)) or a varying-size portion of core (Multiprogramming with Variable Tasks (MVT)).

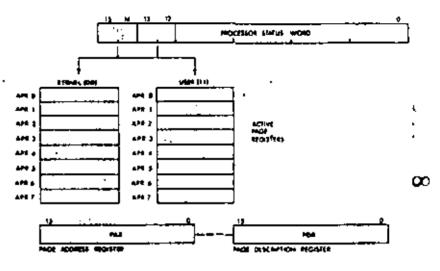

Often in such partitioned memory systems some portion could not be used since it was too small to contain a program. The problem of "holes" or unused portions of core is called fragmentation. Fragmentation has been minimized by the technique of relocatable partitions (Burroughs 6500) and by paging (XDS 940, HIS 645). Relocatable partitioned core allows the unused portions to be condensed into one continuous part of core.

Paging is a method of memory allocation by which the program is subdivided into equal portions or pages, and core is subdivided into equal portions or blocks. The pages are loaded into blocks.

There are two paging techniques: simple and demand. In simple paging all the pages of a program must be in core for execution. In demand paging a program can be executed without all pages being in core, i.e., pages are fetched into core as they are needed (demanded).

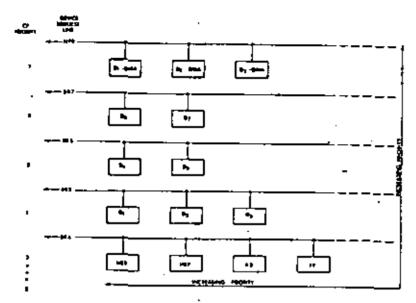

The reader will recall from section 1.1 that a system with several processors is termed a multiprocessing system. The traffic controller coordinates the processors and the processes. The resource of processor time is allocated by a program known as the scheduler. The processor concerned with I/O is referred to as the I/O processor, and programming this processor is called I/O programming.

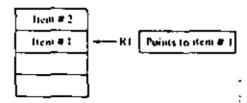

The resource of files of information is allocated by the file system. A segment is a group of information that a user wishes to treat as an entity. Files are segments. There are two types of files: (1) directories and (2) data or programs. Directories contain the locations of other files. In a hierarchical file system, directories may point to other directories, which in turn may point to directories or files.

Thre-sharing is one method of allocating processor time. It is typically characterized by interactive processing and time-slicing of the CPU's time to allow quick response to each user.

A virtual memory (name space, address space) consists of those addresses that may be generated by a processor during execution of a computation. The memory space consists of the set of addresses that correspond to physical memory locations. The technique of segmentation provides a large name space and a good

protection mechanism. Protection and sharing are methods of allowing controlled

# 1.4 OPERATING SYSTEM USER VIEWPOINT: FUNCTIONS

From the user's point of view, the purpose of an operating system (monitor) is to assist him in the mechanics of solving problems. Specifically, the following functions are performed by the system:

- 1. Job sequencing, scheduling, and traffic controller operation

- 2. Input/output programming

- 3. Protecting Itself from the user; protecting the user from other users

- 4. Secondary storage management

- 5. Error handling

Consider the situation in which one user has a job that takes four hours, and another user has a job that takes four seconds. If both jobs were submitted simultaneously, it would seem to be more appropriate for the four-second user to have his run go first. Based on considerations such as this, job scheduling is automatically performed by the operating system. If it is possible to do input and output while simultaneously executing a program, as is the case with many computer systems, all these functions are scheduled by the traffic controller.

As we have said, the I/O channel may be thought of as a separate computer with its own specialized set of instructions. Most users do not want to learn how to program it (in many cases quite a complicated task). The user would like to simply say in his program, "Read," causing the monitor system to supply a program to the I/O channel for execution. Such a facility is provided by operating systems. In many cases the program supplied to the I/O channel consists of a sequence of closely interwoven interrupt routines that handle the situation in this way: "Hey, Mr. t/O Channel, did you receive that character?" "Yes, I received it." "Are you sure you received it?" "Yes, I'm sure," "Okay, I'll send another one." "Fine, send it." "You're sure you want me to send another one?"

An extremely important function of an operating system is to protect the user from being hurt, either muliciously or accidentally, by other users; that is, protect him when other users are executing or changing their programs, files, or data bases. The operating system must insure inviolability. As well as protecting users from each other, the operating system must also protect itself from users who, whether maliciously or accidentally, might "crash" the system.

Students are great challengers of protection mechanisms. When the systems

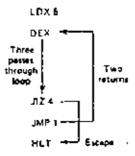

programming course is given at M.I.T., we find that due to the large number of students participating it is very difficult to personally grade every program run on the machine problems. So for the very simple problems - certainly the first problem which may be to count the number of A's in a register and leave the answer in another register - we have written a grading program that is included as part of the operating system. The grading program calls the student's program and transfers control to it. In this simple problem the student's program processes the contents of the register, leaves his knower in another register, and returns to the grading program. The latter checks to find out if the correct number has been left in the enswer register. Afterwards, the grading program prints out a listing of all the students in the class and their grades. For example:

VITA KOHN RACHEL BUXBAUM JOS LEVIN INCORRECT LOFTI ZADEH CORRECT

On last year's run, the computer listing began as follows:

JAMES ARCHER CORRECT **ED MCCARTHY** CORRECT INCORRECT **ELLEN NANGLE** JOHN SCHWARTZ

(We are not sure how John Schwartz did this; we gave him an A in the course.) Secondary storuge management is a task performed by an operating system in confunction with the use of disks, tapes, and other secondary storage for a user's programs and data.

An operating system must respond to errors. For example, if the programmer should overflow a register, it is not economical for the computer to simply stop and wait for an operator to intervens. When an error occurs, the operating system must take appropriate action.

### 1.5 OPERATING SYSTEM USER VIEWPOINT: BATCH CONTROL LANGUAGE

Many users view an operating system only through the batch system control cards by which they must preface their programs. In this section we will discuss a simple monitor system and the control cards associated with it. Other more complex monitors are discussed in Chapter 9.

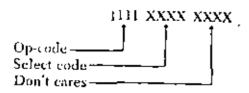

Monitor is a term that refers to the control programs of an operating system. Typically, in a batch system the jobs are stacked in a card reader, and the monitor system sequentially processes each job. A job may consist of several separate programs to be executed sequentially, each individual program being called a job step. In a batch monitor system the user communicates with the system by way of a control language. In a simple batch monitor system we have two classes of control cards: execution cards and definition cards. For example, an execution card may be in the following format:

```

// step name | EXEC | name of program to be autoused, Argument 1, Argument 2

```

The job control card, a definition card, may take on the following format:

```

// job name JOB (User name, identification, expected time was, times to

be printed out, expected number of cards to be printed

out.

```

Usually there is an end-of-file card, whose formal might consist of /\*, signifying the termination of a collection of data. Let us take the following example of a FORTRAN job.

```

//EXAMPLE

JOB

DONOVAN.

T168.1.100.0

//STEP1

EXEC

FORTRAN, NOPURCH

READ 9100.N

DO 1001 = 1.N

12 - [*]

[3 - [*]*]

100 PRINT $100, I, IZ, I3

$100 FORMAT (210)

END

//STEP2

EXECLOAD

//STEP3

EXECOBIECT

```

The first control card is an example of a definition card. We have defined the user to be Donovari. The system must set up an accounting file for the user, noting that he expects to use one minute of time, to output a hundred lines of output, and to punch no cards. The next control card, EXEC FORTRAN, NOPUNCH, is an example of an execution card; that is, the system is to execute the program FORTRAN, given one argument — NOPUNCH. This argument allows the monitor system to perform more efficiently; since no cards are to be punched, it need not utilize the punch routines. The data to the compiler is the FORTRAN program shown, terminated by an end-of-file card /\*.

The next control card is another example of an execution card and in this

case causes the execution of the loader. The program that has just been compiled will be loaded, together with all the routines necessary for its execution, where upon the loader will "bind" the subroutines to the main program. This job step upon the loader will "bind" the subroutines to the main program. This job step upon the loader will "bind" the subroutines to the main program is another execution card, causing the monitor system to execute the object program just compiled. The data card, 10, is input to the program and is followed by the end-of-

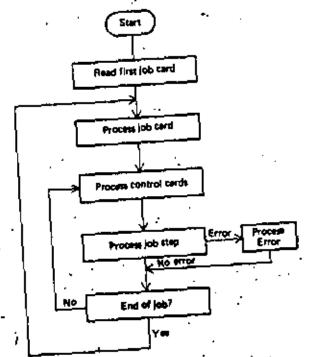

The simple loop shown in Figure 1.4 presents an overview of an implementation of a batch monitor system. The monitor system must read in the first card, presumably a job card. In processing a job card, the monitor saves the user's name, account number, allotted time, card punch limit, and line print limit. If the next control card happens to be an execution card, then the monitor will load the corresponding program from secondary storage and process the job step by transferring control to the executable program. If there is an error during processing, the system notes the error and goes back to process the next job step.

FIGURE 1.4. Main loop of a simple betch monitor system

### 1.8 OPERATING SYSTEM USER VIEWPOINT: FACILITIES

For the applications-oriented user, the function of the operating system is to provide facilities to help solve problems. The questions of scheduling or protoction are of no interest to him; what he is concerned with is the available software. The following facilities are typically provided by modern operating systems:

- 1. Assemblers

- 2. Compilers, such as FORTRAN, COBOL, and FLS

- 3. Subroutine libraries, such as SINE, COSINE, SQUARE ROOT

- 4. Linkage editors and program loaders that bind subroutines together and prepare programs for execution

- 5. Utility routines, such as SORT/MERGE and TAPE COPY

- Application packages, ruch as circuit analysis or simulation.

- 7. De bugging facilities, such as program tracing and "core dumps"

- 8. Data management and file processing

- 9. Management of system hardware

Although this "facilities" aspect of an operating system may be of great interest to the user, we feel that the answer to the question, "Flow many compilets does that operating system have?" may tell more about the orientation of the manufacturer's marketing force than it does about the structure and effectiveness of the operating system.

#### 1.7 SUMMARY

The major components of a programming system are:

#### 1. Assembler

laput to an assembler is an assembly language program. Output is an object prograin plus information that enables the loader to prevere the object program for execution.

### 2. Macro Processor

A metro cell is an abbreviation (or name) for some code. A matro definition is a sequence of code that has a name (macro call). A macro processor is a program that substitutes and specializes macro definitions for mucro calls.

#### 3. Louder

A loader is a routine that loads an object program and prepares it for execution.

### BACKGROUND

There are various loading schemes: absolute, relocating, and direct-linking. In general, the loader must load, relocate, and link the object program.

### 4. Compilers

A compiler is a program that accepts a source program "in a high-level language" and produces a corresponding object program.

### 6. Operating Systems

An operating system is concerned with the allocation of resources and services. such as memory, processors, devices, and information. The operating system correspondingly includes programs to manage these resources, such as a ineffic controller, a scheduler, memory management module, I/O programs, and a file system.

# Input-Output Devices

# DIGITAL PRINCIPLES AND APPLICATIONS

### MALVIO/LEACH

In any digital system it is necessary to have a link of communication between manand machine. This communication link is often called the "man-machine interface" and it presents a number of problems. Digital systems are capable of operating on information at speeds much greater than man's, and this is one of their most important attributes. For example, a large-scale digital computer is capable of performing more than 500,000 additions per second.

The problem here is to provide data input to the system at the highest possible rate. At the same time, there is the problem of accepting data output from the system at the highest possible rate. The problem is further magnified since most digital systems do not speak English, or any other language for that matter, and some system of symbols must therefore be used for communication there is at present a considerable amount of research in this area, and some systems have been developed which will accept spoken commands and give oral responses on a limited basist.

Since digital systems operate in a binary mode, a number of code systems which are binary representations have been developed and are being used as the language of communication between man and machine, to this chapter we discuss a number of these codes and, at the same time, consider the necessary input-output equipment,

The primary objective of this chapter is to acquire the ability to

- 1. Explain how Hollerith code and ASCII code are used in input/output media.

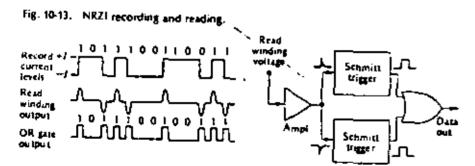

- Discuss techniques for magnetic recording of digital information, including RZ, RZI, and NRZI.

- 3. Describe the limitations of a number of different digital input/output units.

- Draw the logic diagrams for a simple tree decoder and a balanced multiplicative decoder.

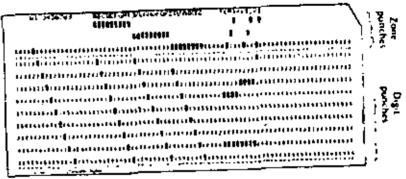

### 10-1 PUNCHED CARDS

One of the most widely used media for entering data into a machine, or for obtaining output data from a machine, is the punched card. Some common examples of these cards are college registration cards, government checks, monthly oil company statements, and bank statements. It is quite simple to use this medium to represent binary information, since only two conditions are required. Typically, a hole in the card represents a 1 and the absence of a hole represents a 0. Thus, the card provides the means of presenting information in hinary form, and it is only necessary to develop the code.

The typical punched card used in large-scale data-processing systems is 7% in long, 3% in wide, and 0.007 in thick. Each card has 80 vertical columns, and there are 12 horizontal rows, as shown in Fig. 10-1. The columns are numbered 1 through 80 along the bottom edge-of the card. Beginning at the top of the card, the rows are designated 12, 11, 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. The bottom edge of the card is the 9 edge, and the top edge is the 12 edge. Holes in the 12, 11, and 0 rows are called zone punches, and holes in the 0 through 9 rows are called digit punches. Notice that row 0 is both a zone-and a digit-punch row. Any number, any letter in the alphabet, or any of several special characters can be represented on the card by punching one or more holes in any one column. Thus, the card has the capacity of 80 numbers, letters, or combinations.

Probably the most widely used system for recording information on a punched card is the Hullerith code, in this code the numbers 0 through 9 are represented by a single punch in a vertical column. For example, a hole punched in the fifth row of column 12 represents a 5 in that column. The letters of the alphabet are represented by two punches in any one column. The letters A through I are represented by a zone punch in row 12 and a punch in rows 1 through 9. The letters I through R are represented by a zone punch in row 11 and a punch in row 0 and a punch in rows 2 through 9. Thus, any of the 10 decimal digits and any of the 26 letters of the alphabet can be represented in a binary fashion by punching the proper holes in the card. In addition, a number of special characters can be represented by punching combinations of holes in a column which are not used for the numbers or letters of the alphabet. These characters are shown with the proper punches in Fig. 10-1.

An easy device for remembering the alphabetic characters is the phrase "IR, is 11." Notice that the letters J through R have an 11 punch, those before have a 12 punch, and those after have a 0 punch, it is also necessary to remember that 5 begins on a 2 and not a 1.

### Example 10-1

Decode the information punched in the card in Fig. 10-2.

### **Solution**

Column 1 has a \* \* \* punch in row 0 and a punch in row 3, It is therefore the letter 1. Column 2 h. \* zone punch in row 12 and another punch in row 8. It is

Fig. 10-1. Standard punched card using Hollenth code.

therefore the letter H. Continuing in this fashion, you should see that the complete message reads, "THE QUICK BROWN FOR JUMPED OVER THE LAZY THOSS WALK."

With this card code, any alphanumeric (alphabetic and numeric) information can be used as input to a digital system. On the other hand, the system is capable of delivering alphanumeric output information to the user. In scientific disciplines, the information might be missile flight number, location, or guidance information such as pitch rate, roll rate, and yaw rate. In business disciplines, the information could be account numbers, names, addresses, monthly statements, etc. In any case, the information is punched on the card with one character per column, and the card is then capable of containing a maximum of 80 characters.

Each Card is considered as one block or unit of information. Since the machine operates on one card at a time, the punched card is often referred to as a "unit record." Moreover, the digital equipment used to punch cards, read cards into a system, surt cards, etc., is referred to as "unit-record equipment."

Occasionally, the information used with a digital system is entirely numeric; that is, no alphabetic or special characters are required, in this case, it is possible to input the information to the system by punching the cards in a straight binary fashion. In this system, the absence of a punch is a binary 0, and a punch is a

Fig. 10-2. Example 10-1.

| **       |      | ٠,,       |           | 11<br>51 ( | ٠,           | -                                 |                | ) 4#1<br>                           | 1           | 10                  |

|----------|------|-----------|-----------|------------|--------------|-----------------------------------|----------------|-------------------------------------|-------------|---------------------|

| *******  |      | •         |           |            |              | 111111                            |                | .,,,,,,,                            |             |                     |

| 10110111 | 1771 | des       | 1111111   | *****      | 71<br> 116   | 1762 }<br>1 <b>4</b> 111 <b> </b> | ,,,,,,         | 1 1 1 4 5 5 5                       | (11131C)C+C | 114114114114114     |

| (11414)  | 1411 | ****      | 4         | ****       |              |                                   | <b>.</b>       | +++ <b>+</b> 4+<br> ++3 <b>7</b> 61 | }           | 11)1-11)1-11)1-1-1  |

| 1101(114 |      | . 1 4 , 8 | hitte<br> |            | <b>Ç</b> 141 |                                   | 4144'<br>      | . <b>.</b>                          | **********  | (10171140111111     |

| 011160   | 100  | ****      | *******   | ******     | (11)         | .,,                               | 1 4 <b>j</b> 1 |                                     | ********    | -Mannana<br>Marking |

| 14111111 |      |           |           | +          |              |                                   |                |                                     |             | <del></del>         |

binary 1, it is then possible to punch 80  $\times$  12 = 960 bits of binary information on one Card.

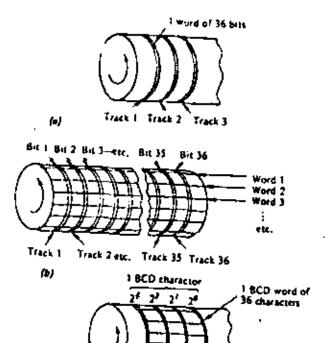

Many large-scale data-processing systems use binary information in blocks of 36 bits. Each block of 36 bits is called a "word," You will recall from the previous chapter that a register capable of storing a 36-bit word must contain 36 flip-flops. There is nothing magical about the 36-bit word, and there are in fact other systems which operate with other word lengths. Even so, let's see how binary information. There

There are two methods. The first method stores the information on the card horizontally by punching across the card from feft to right. The first 36-bit word is punched in row 9 in columns 1 through 36. The second word is also in row 9, in columns 37 through 72. The third word is in row 8, columns 1 through 36, and so on. Thus a total of twenty-four 36-bit words can be punched in the card in straight binary form. It is then possible to store 864 bits of information on the card.

The second method involves punching the information on the card, rather than rows. Beginning in row 12 of column 1, the first 12 bits of the word are punched in rows 12, 11, 0, ..., 9. The next 12 bits are punched in column 2, and the remaining 12 bits are punched in column 3. Thus, a 36-bit word can be punched in every three columns. The card is then capable of containing twenty-six.

The most common method of entering information into punched cards initially is by means of the key-punch machine. This machine operates very much the same as a typewriter, and the speed and accuracy of the operation depend entirely on the operator. The information on the punched cards can then be read into the digital at the rate of 100 to 1,000 cards per minute, depending on the type of card reader.

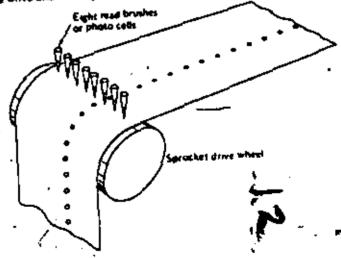

The basic method for changing the punched information into the necessary electrical signals is shown in Fig. 10-3. The cards are stacked in the read hopper and are drawn from it one at a time. Each card passes under the read heads, which are either brushes or photocells. There is one read head for each column on the card, and when a hole appears under the read head an electrical signal is generated.

Fig. 10-3. Card-reading operation.

Thus, each signal from the read heads represents a binary 1, and this Information or can be used to set flip-flops which form the input storage register. The cards then ou pass over other rollers and are placed in the stacker. There is quite often a second rid read head which reads the data a second time to provide a validity check on the limit reading process.

### Example 10-2

Suppose a deck of cards has binary data punched in them, Each card has twenty-ty-four 36-bit words. If the cards are read at a rate of 600 cards per minute, what is the he rate at which data are entering the system?

#### Solution

Since each card contains 24 words, the data rate is  $24 \times 600 = 14,400$  words personal minute. This is equivalent to  $36 \times 34,400 = 518,400$  bits per minute, or or 518,400/60 = 8,640 bits per second.

Punched cards can also be used as a medium for accepting data output from a), digital system. In this case, a stack of blank cards thaving no holes punched in it them) are held in a hopper in a card punch which is controlled by the digital to system. The blank cards are drawn from the hopper one at a time and punched exwith the proper information. They are then passed under read heads, which checking the validity of the punching operation, and stacked in an output hopper. Cardina punches are capable of operating at 100 to 250 cards per minute, depending on the his system used.

Punched cards present a number of important advantages, the first of which is a the fact that the cards represent a means of storing information permanently. Since of the information is in machine code, and since this information can be printed on of the top edge of the card, this is a very convenient means of communication of between man and machine, and between machine and machine. There is also as wide variety of peripheral equipment which can be used to process information of stored on cards. The most common are soriers, collators, calculating punches; reproducing punches, and accounting machines. Moreover, it is very easy to confect or change the information stored, since it is only necessary to remove the fridesired card(s) and replace it (them) with the corrected one(s). Finally, these cards to are quite inexpensive.

#### 10-2 PAPER TAPE

3

Another widely used input-output medium is punched paper tape. It is used in a much the same way as punched cards. Paper tape was developed initially for the appropriate of transmitting telegraph messages over wires. It is now used extensively for storing information and for transmitting information from machine to machine. Paper tape differs from cards in that it is a continuous roll of paper; thus, any amount of information can be punched into a roll. It is possible to record any alphabetic or numeric character, as well as a number of special characters, on paper tape by punching holes in the tape in the proper places.

Input-Output Devices

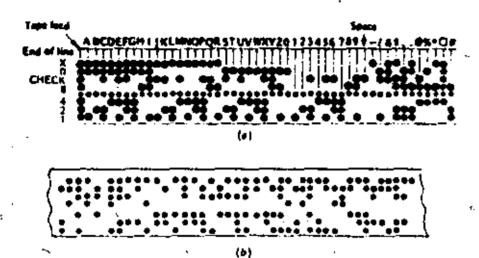

Fig. 10-4, - Punched paper tape. (a) Eight-hole code, (b) Example 10-3,

There are a number of codes for punching data in paper tape, but one of the most widely used is the eight-hole code in Fig. 10-4a. Holes, representing data, are punched in eight parallel channels which run the length of the tape. (The channels : are labeled 1, 2, 4, 8, parity, 0, X, and end of line.) Each character, - numeric. alphabetic, or special. - occupies one column of eight positions across the width of the Upe.

Numbers are represented by punches in one or more channels labeled 0, 1, 2, 4, and 8, and each number is the sum of the punch positions. For example, 0 is represented by a single punch in the 0 Channel; I is represented by a single punch in the 1 channel: 2 is a single punch to channel 2: 3 is a punch in channel 1 and a punch in channel 2, etc. Alphabutic characters are represented by a combination of punches in Channels X, Q, 1, 2, 4, and 8, Channels X and 0 are used much as the zone punches in punched cards. For example, the letter A is designated by punches in channels X, 0, and 1. The special characters are represented by combinations of nunches in all channels which are not used to designate either numbers or letters, A punch in the end-of-line channel signifies the end of a block of information, or the end of record. This is the only time a punch appears in this channel.

As a means of checking the validity of the information punched on the tage, the parity channel is used to ensure that each character is represented by an odd number of holes. For example, the letter C is represented by punches in channels X. 0. 1. and 2. Since an odd number of holes is required for each character, the code for the letter C also has a punch in the parity channel, and thus a total of five punches is used for this letter.

### Example 10-3

What information is held in the perforated tape in Fig. 10-46?

The first character has punches in channels 0, 1, and 2, and this is the letter T. The  $\hat{x}$ second character is the letter H, since there are punches in channels II, O, and B. Continuing, you should see that the message is the same as that punched on the card in Example 10-1.

The row of smaller holes between channels 4 and 6 are guide holes, used to guide and drive the tape under the read positions. The information on the tape can be sensed by brushes or photocells as shown in Fig. 10-5. The method for reaching information from the paper tape and inputting it into the digital system is very simifar to that used for reading punched cards. Depending on the type of reader used. information can be read into the system at a rate of 150 to 1,000 characters second. You will notice that this is only slightly faster than reading information

Paper tape can be used as a means of accepting information output from a digital from punched cards. system, in this case the system drives a tape punch which eners the data on the tape by punching the proper holes. Typical tape punches are capable of operating at rates of 15 characters per second, and the data are punched with 10 characters to the inch. The number of characters per inch is referred to as the "data density." and in this case the density is 10 characters per inch, Recording density is one of the important features of magnetic-tape recording which will be discussed in the

Paper tape can also be perforated by a manual tape punch. This unit is very siminext session. tar to an electric typewriter, and Indeed in some cases electric typewriters with special punching units attached are used. The accuracy and speed of this method are again a function of the machine operator. One advantage of this method is that

Fig. 10-5. Paper-tape drive and reading mechanism.

¢

the typewriter provides a written copy of what is punched into the tape. This copy can be used for verification of the punched information,

### 10-3 MAGNETIC TAPE

Magnetic tape has become one of the most important methods for storing large quantities of information. Magnetic tape offers a number of advantages over punched cards and punched paper tape. One of the most important is the fact that magnetic tape can be erased and used over and over. Reading and recording are much faster than with either cards or paper tape. However, they require the use of a tape-drive unit which is much more expensive than the equipment used with cards and paper tape. On the other hand, it is possible to store up to 20 million characters on one 2,400-ft reel of magnetic tape, and if a high volume of data is one of the system requirements, the use of magnetic tape is well justified. Most commonly, magnetic tape is supplied on 2,400-ft reels. The tape itself is a Va-in-wide strip of plastic with a magnetic oxide coating on one side.

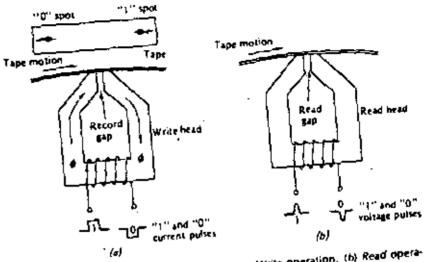

Data are recorded on the tape in seven parallel channels along the length of the tape. The channels are labeled 1, 2, 4, 8, A, B, and C as shown in Fig. 10-6. Since the information recorded on the tape must be digital in form, that is, there must be two states, it is recorded by magnetizing spots on the tape in one of two directions.

A simplified presentation of the write and read operations is shown in Fig. 10-7. The magnetic spots are recorded on the tape as it passes over the write head as shown in Fig. 10-7a. If a positive pulse of current is applied to the write-head coil, as shown in the figure, a magnetic flux is set up in a clockwise direction around the write head. As this flux passes through the record gap, it spreads slightly and passes through the oxide coating on the magnetic tape. This causes a small area on the tape to be magnetized with the polarity shown in the figure, if a current pulse of the opposite polarity is applied, the flux is set up in the opposite direction, and a spot magnetized in the opposite direction is recorded on the tape. Thus, it is possible to record data on the tape in a digital fashion. The spots shown in the figure are greatly exaggerated in size to show the direction of magnetization clearly.

In the read operation shown in Fig. 10-7b, a magnetized spot on the tape sets up a flux in the read head as the tape passes over the read gap. This flux induces a small voltage in the read-head coil which can be amplified and used to set or reset a flip-flop. Spots of Opposite polarities on the tape induce voltages of opposite

Fig. 10-6. Magnetic-tape code.

|             | 0123456749 | ABCOEFGHIJK | LANGEORS TU | ****     | 4.0-54                                        | 1,800         |

|-------------|------------|-------------|-------------|----------|-----------------------------------------------|---------------|

| Check ( C ) |            | 111         | ] [] [      | <u> </u> | ] ] [                                         | 11            |

| Inne ( B    | }          | 111111111   | 111111      |          | 111111                                        |               |

| į.a.        |            | 111111111   | 111         | 11111    | 111                                           | <u> </u>      |

| ∫ •         | <u> </u>   |             |             | <u> </u> | <u></u>                                       | 1111          |

| Numerous d  | <u> </u>   | 111         | <u> </u>    | 111      |                                               | (             |

| 2           | <u> </u>   | <u> </u>    | <u> </u>    | <u> </u> | <u>.                                     </u> |               |

| { r         | <u> </u>   | 1 1 1 1 1   | <u> </u>    | 111      | <u> </u>                                      | <u>11 1 i</u> |

Fig. 10-7. Magnetic-tape recording and reading. (a) Write operation, (b) Read opera-

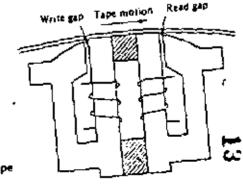

polarities in the read coil, and thus both 1s and 0s can be sensed. There is one read/write head for each of the seven channels on the tape. Typically, read/write heads are constructed in pairs as shown in Fig. 10-8. Thus, the write operation can be set up as a self-checking operation. That is, data recorded on tape are immediately read as they pass over the read gap and can be checked for validity. A coding system similar to that used to punch data on cards is used to record

A coding system similar to that used to punch data on calls in our of seven alphanumeric information on tape. Each character occupies one column of seven bits across the width of the tape. The code is shown in Fig. 10-6. There are two inbits across the width of the tape. The code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape, the code is shown in Fig. 10-6. There are two inbits across the width of the tape. The code is shown in Fig. 10-6. There are two inbits across the width of the tape. The code is shown in Fig. 10-6. There are two inbits across the width of the tape. The code is shown in Fig. 10-6. There are two inbits across the width of the tape.

The first system is a vertical parity bit which is written in channel C of the tape. This is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character check bit" and is written in channel C to ensure that all this is called a "character check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that all this is called a "character-check bit" and is written in channel C to ensure that the character check bit is a charact

Fig. 10-8. Magnetic-tape read/write heads.

The second system is the horizontal parity-check bit. This is sometimes referred to as the longiturinal parity bit, and it is written, when needed, at the end of a block of information or record. The total number of bits recorded in each channel is monitored, and at the end of a record, a parity bit is written if necessary to keep the total number of bits an even number. These two systems form an even-parity system. They could, of course, just as easily be implemented to form an odd-parity system, information can also be recorded on the tape in straight binary form. In this case, a 36-bit word is written across the width of the tape in groups of six bits. Thus

it requires six columns to record one 36-bit word. The vertical spacing between the recorded spots on the tape is fixed by the positions of the read/write heads. The horizontal spacing is a function of the tape speedand the recording speed. Tape speeds vary from 50 to 200 in/s, but 25 and 112,5 in/s are quite common.

The maximum number of characters recorded in 1 in of tape is called the "recording density." and it is a function of the tape speed and the rate at which data are supplied to the write head. Typical recording densities are 200, 556, and 800 bits per inch. Thus it can be seen that a total of 800 x 2,400 x 12 = 23.02 × 10° characters can be stored on one 2.400-ft reel of tape. This would mean that the data would have to be stored with no gaps between characters or groups of characters.

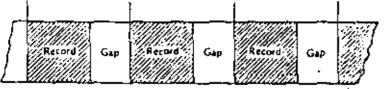

mation in groups or blocks called "records." In between records there is a blank space of rape called the "interrecord gap," This gap is typically a 0.75-in space of blank tape, and it is positioned over the read/write heads when the tape stops. The interrecord gap provides the space necessary for the tape to come up to the proper speed before recording or reading of information can take place. The total number of characters recorded on a tape is then also a function of the record length for the total number of interrecord gaps, since they represent blank space on the tape).

For purposes of locating information on tape, it is most common to record infor-

The data as recorded on the tape, including records factual data) and interrecord gaps, can be represented as shown in Fig. 10-9. If there were no interrecord gaps, the total number of characters recorded could be found by multiplying the length of the tape in inches by the recording density in characters per inch. If the record were exactly the same length as the interrecord gap, the total storage would be out in half. Thus, it is desirable to keep the records as long as possible in order to use the tape most efficiently.

Fig. 10-9. Recording data on magnetic tape.

Input-Output Devices

Given any one tape system and the recording density, it is a simple matter to determine the actual storage capacity of the tape. Consider the length of tape composed of one record and one record gap as shown in Fig. 10-9. This length of tape is repeated over and over down the length of the tape. The total number of characters that could be stored in this length of tape is the sum of the characters in the record R and the characters which could be stored in the record gap. The number of characters which could be stored in the gap is equal to the recording density D multiplied by the gap length G. Thus the total number of characters which could be stored in this length of tape is given by R + GD. The ratio of the characters actually recorded R to the total possible could be called a tape-utilization factor f and is given by

$$F = \frac{R}{R + GD} \quad . \tag{10-1}$$

Examination of the tape-utilization factor shows that if the total number of characters in the record is equal to the number of characters which could be stored in the gap, the utilization factor reduces to 0.5. This utilization factor can be used to determine the total storage capacity of a magnetic tape if the recording density and the record length are known. Thus the total number of characters stored on a tape CHAR is given by

$$CHAR = LDF \tag{10-2}$$

where L = length of tape, in D = recording density, characters per inch.

For a standard 2,400-ft reel of tape having a 0.75-in record gap, the formula in Eq. (10-2) reduces 10

$$CHAR = \frac{2,400 \times 12 \times DR}{R + 0.75D} \tag{10-3}$$

### Example 10-4

What is the total storage capacity of a 2,400-ft reel of magnetic tape if data are recorded at a density of \$56 characters per inch and the record length is 100 characters?

### Solution

The total number of characters can be found using Eq. (10-3).

$$CHAR = \frac{2,400 \times 12 \times 556 \times 100}{100 + (0.75 \times 556)} = 3.10 \times 10^6$$

This result can be checked by calculating the tape-utilization factor.

ĊП

The maximum number of characters that can be stored on the tape is  $2.400 \times 12 \times 556 = 16.0128 \times 10^4$ . Multiplying this by the utilization factor gives

$$CHAR = 16.0128 \times 10^{6} \times \frac{1}{5.17} = 3.10 \times 10^{6}$$

### 10-4 DIGITAL RECORDING METHODS

There are a number of methods for recording data on a magnetic surface. The methods fall into two general categories, called "return-to-zero" and "non-return-to-zero," and they apply to magnetic-tape recording as well as recording on magnetic disk and drum surfaces (magnetic-disk and magnetic-drum storage will be discussed in a later chapter).

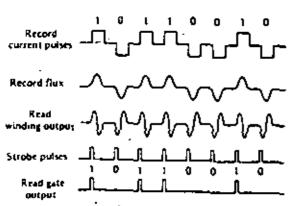

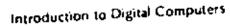

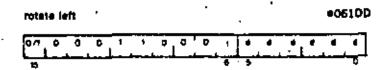

In the previous section, it was stated that digital information could be recorded on magnetic tape by magnetizing spots on the tape with opposite polarities. This type of recording is known as return-to-zero, or RZ for short, recording. The technique for recording data on tape using this method is to apply a series of current pulses to the write-head winding as shown in Fig. 10-10. The current pulses set up corresponding fluxes in the write head, as shown in the figure. The spots magnetized on the tape have polarities corresponding to the direction of the flux waveform, and it is only necessary to change the direction of the input current to write its or 0s. Notice that the input current and the flux waveform return to a zero reference level between individual hits. Thus the term "return to zero."

When it is desired to read the recorded information from the tape, the tape is passed over the read heads and the magnetized spots induce voltages in the read-coil winding as shown in the figure. Notice that there is somewhat of a problem here, since all the pulses have both positive and negative portions. One method of detecting these levels properly is to strobe the output waveform. That is, the output

Fig. 10-10. Return-to-zero recording and reading.

Fig. 10-11. Biased return-to-zero recording and reading.

voltage waveform is applied to one input of an AND gate lafter being amplified), and a clock or strobe pulse is applied to the other input to the gate. The strobe pulse must be very carefully timed to ensure that it samples the output waveform at the proper time. This is one of the major difficulties of this type of recording, and it is therefore seldom used except on magnetic drums. On a magnetic drum, the strobe waveform can be recorded on one track of the drum, and thus the proper timing is achieved.

A second difficulty with this type of recording is the fact that between bits there is no record current, and thus between the spots on the tape the magnetic surface is randomly oriented. This means that if a new recording is to be made over old data, the new data have to be recorded precisely on top of the old data. If they are not, the old data will not be erased, and the tape will contain a conglomeration of information. The tape could be erased by installing another set of erase heads, but this is 'costly and unnecessary.

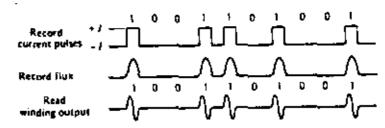

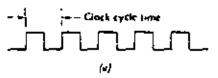

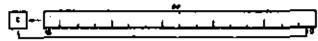

A method for curing these problems is to bias the record head with a current which will saturate the tape in either one direction or the other. In this system, a current pulse of positive polarity is applied only when it is desired to write a 1 on the tape as shown in Fig. 10-11. At all other times the flux in the write heads is sufficient to magnetize the entire track in the 0 direction. Now, recording data over old data is not a problem since the tape is effectively erased as it passes over the record heads. Moreover, the timing is not so critical since it is not necessary to record exactly over the previous data. When data are recorded in this fashion and then played back, a pulse appears at the output of the read winding only when a 1 has been recorded on the tape. This makes reading the information from the tape much simpler.

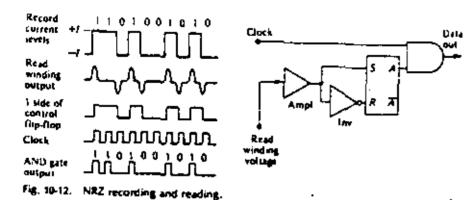

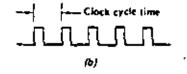

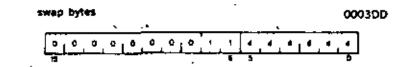

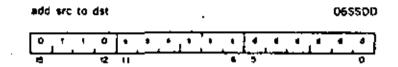

The non-return-to-zero, or NRZ, recording technique is a variation of the RZ technique where the write current pulses do not return to some reference level between bits. The NRZ recording technique can be best explained by examining the record-current waveform shown in Fig. 10-12. Notice that the current is at +1 while recording 1s and at -1 while recording 0s. Since the current levels are always at either +1 or -1, the recording problems of the first RZ system do not exist here.

Notice that the voltage at the read-winding output has a pulse only when the recorded data change from a 1 to a 0 or vice versa. Therefore, some means of sensing the recorded data is necessary for the read operation. If the read-winding voltage is amplified and used to set or reset a flip-flop as shown in the figure, the A side of the flip-flop is high during each time that a 1 is being read. It is low during

any time when the data being read is a 0. Thus if the A output of the flip-flop is used as a control signal at one input of an ANO gate, while the other input is a clock, the output of the AND gate is an exact replica of the digital data being read. Notice that the clock must be carefully synchronized with the data train from the read-head winding. Notice also that the maximum rate of flux changes occurs