#### 2.5 Dispositivo Inversor.

# 2.5.1 Arreglo de transistores tipo Puente H.

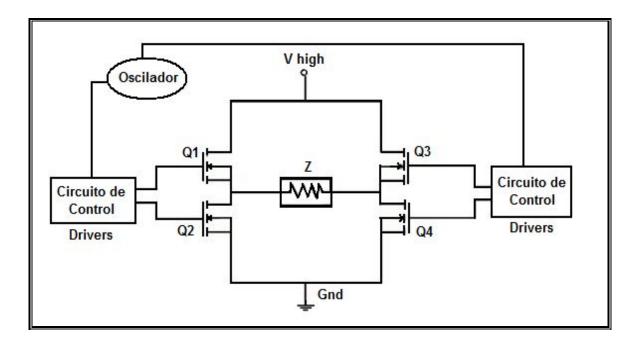

El dispositivo inversor es un circuito electrónico que sirve para generar corriente alterna (AC) a partir de una corriente directa o continua (DC). Se le denomina puente H debido a que su configuración electrónica está formada por cuatro transistores de poder tipo MOSFET ( $Q_1$ ,  $Q_2$ ,  $Q_3$  y  $Q_4$ ) y una resistencia de carga (Z), formando en composición una H. Los MOSFET son manejados por etapas de control a partir de semiconductores denominados drivers. El puente H se basa en un oscilador, el cual gestiona las etapas de control y define la forma de la señal de salida del dispositivo. La estructura del dispositivo inversor se muestra en la siguiente figura:

Fig. 4.6 Dispositivo Inversor tipo Puente H.

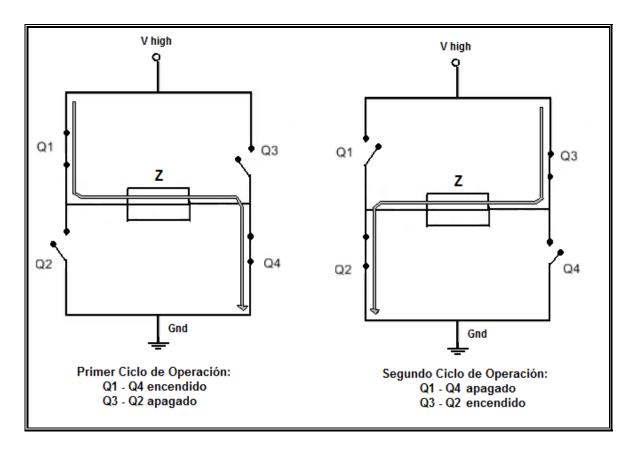

Las etapas de control regulan los ciclos de encendido y apagado de los MOSFETS en pares, para una primera etapa de operación se controlan Q1-Q4 y posteriormente Q3-Q2, nunca se regulan MOSFETS del mismo lado del puente, debido a que si se llegaran a encender los transistores del mismo lado  $(Q_1-Q_2 \circ Q_3-Q_4)$ , estos crearían un corto circuito entre las terminales de Vhigh y Gnd (Tierra del dispositivo).

Para el primer ciclo de operación del puente H, los circuitos de control encienden a Q1 y Q<sub>4</sub>, dejando fluir la corriente de manera positiva en el circuito y, mantienen en apagado a  $Q_2$  y  $Q_3$ ; para el segundo ciclo de operación  $Q_1$  y  $Q_4$  se apagan, y ahora se encienden y conducen el otro par Q2 y Q3, permitiendo un flujo de corriente de manera inverso, o sea negativo(37). La figura 4.7 muestra gráficamente este funcionamiento.

Fig. 4.7 Ciclos de operación del Puente H.

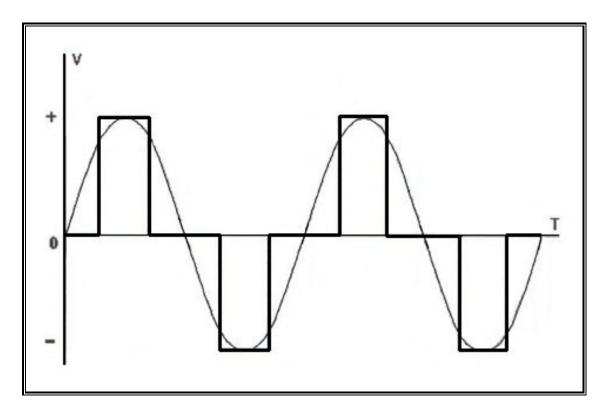

Haciendo uso de la tecnología digital, se ha utilizado un microcontrolador como el circuito oscilador del puente H, esto brinda ventajas como son: una gran estabilidad en la frecuencia de los pulsos, así como un ciclo de trabajo controlable y constante. La señal de salida generada por el puente H deberá ser de forma senoidal, esto para disminuir la distorsión armónica que puede llegar a influir en el correcto funcionamiento de distintos circuitos, motores, etc. Sin embargo, se ha optado por utilizar una forma de señal semi senoidal o también llamada de tres niveles, en primera instancia por su simplicidad para generarla y posteriormente por su buen desempeño en los equipos que pueden trabajar con ella. En la figura 4.8 muestra la señal de salida del puente H.

La utilización de transistores MOSFETS en la estructura del puente H es por una razón principal: mejorar la eficiencia del puente. Los MOSFETS tienen una resistencia entre el drain y el source cuando el transistor está encendido (RDSon), está debe ser de valores muy bajos, esto para garantizar que las pérdidas de voltaje en cada transistor sean mínimas, incluso a altas corrientes. Naturalmente, mientras más bajo sea el valor de la RDSon del transistor, el costo del semiconductor se eleva considerablemente.

Fig. 4.8 Señal semi senoidal de tres niveles del Puente H.

Los MOSFETS son extremadamente sensibles a la corriente estática y por ello es importante tener en cuenta que si se deja la compuerta (Gate) en circuito abierto, éste puede autodestruirse, debido a que el MOSFET es un dispositivo de alta impedancia (más de 10 M $\Omega$ ) y el ruido puede activarlo. Para utilizar el tipo adecuado de transistor debemos considerar que éste debe de trabajar en su área segura de operación, la cual está determinada por tres variables que forman los límites de una operación aceptable.

#### Estos límites son:

- La corriente máxima de drenaje.

- El voltaje máximo de drenaje fuente.

- La temperatura máxima de unión.

#### 2.5.2 Circuito de Control para manejo de MOSFETS (Drivers).

Se busca que el encendido de los MOSFET que conforman la estructura del puente H sea lo más rápido posible para minimizar las pérdidas por conmutación. Para lograr esto, el circuito de control acoplado y conectado a la compuerta (Gate) de los MOSFETS debe ser capaz de suministrar la suficiente corriente para incrementar rápidamente el voltaje al valor requerido, en donde el MOSFET se saturará completamente. Por otro lado, para lograr apagar un MOSFET es necesario reducir en acción inversa el voltaje compuerta-fuente a los especificados en el diseño para encenderlo.

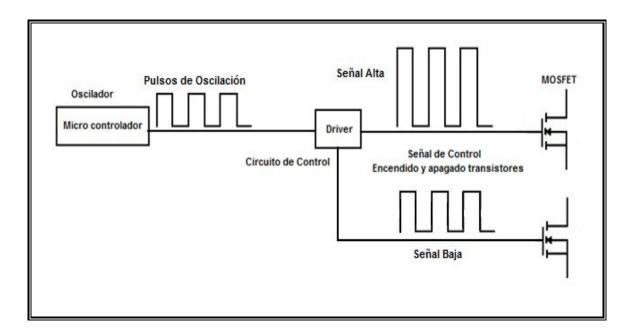

Para controlar el encendido y apagado de los transistores en ambos lados de la estructura del puente H, debemos hacer uso de un circuito integrado llamado driver, el cuál será capaz de recibir las señales lógicas del micro controlador, que funge como oscilador, y a su vez generar una señal de salida que logrará el control hacia los transistores.

Fig. 4.9 Etapa de control del MOSFET.

En la figura 4.9 se muestra las señales de control generadas por el driver hacia los MOSFETS, estas en función del microcontrolador como pulsos a una frecuencia determinada de oscilación. El driver genera dos señales de salida, con la misma forma y frecuencia, pero a un nivel de voltaje diferente, una de un orden mayor (High output) y la otra a un nivel más bajo (Low output).

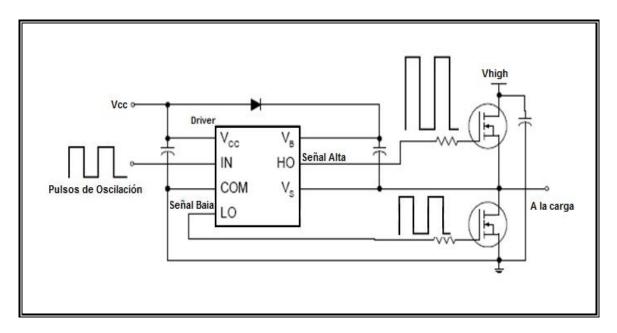

El arreglo funciona de manera que dos transistores cruzados funcionen a la vez, con una frecuencia de alternancia de 60[Hz] debido a que es la frecuencia de oscilación de la señal comercial, y así generar la corriente alterna a la salida de nuestro dispositivo inversor que buscamos. Luego entonces, la estructura del driver se muestra en la figura 5.1.

La elección de este tipo de controladores fue en base a su capacidad de soportar picos de voltaje de hasta 600[V] principalmente. El voltaje alto  $(V_{high})$  con el cuál son alimentados los MOSFETS como voltaje de referencia en su drain es generado por el convertidor de subida (Boost), este es un voltaje de 170[Vpp] aproximadamente, el cúal debe estar en este nivel debido a que estamos buscando generar una señal de corriente alterna lo más parecido a la señal comercial ( $120[V_{pp}]$  a 60[Hz]).

Fig. 5.1 Driver semiconductor ISR2111.

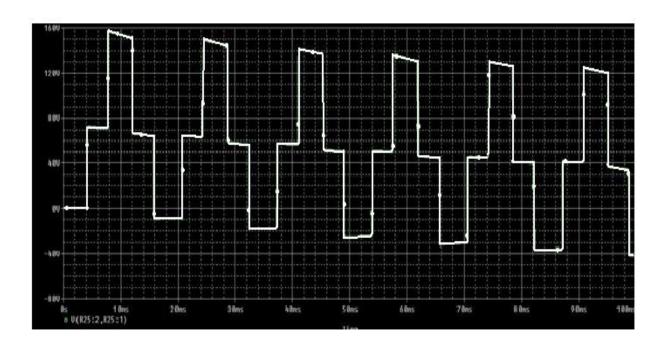

En la siguiente figura se muestra una simulación<sup>(38)</sup> del puente H y la señal de salida que generá el dispositivo inversor a la carga:

Fig. 5.2 Señal de tres niveles del dispositivo inversor tipo puente H.

## 2.5.3 Estructura del algoritmo y programación del Microcontrolador.

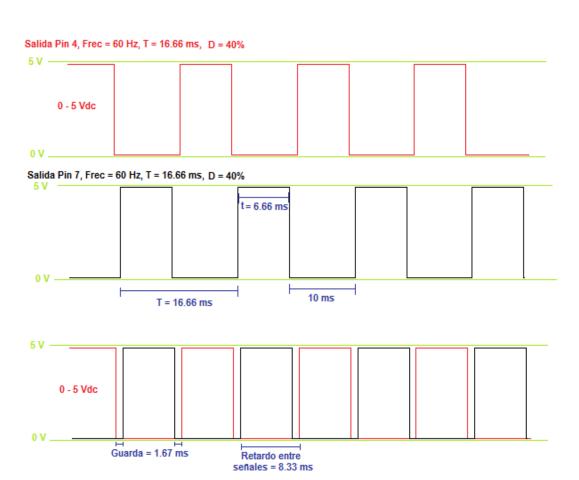

Las señales procedentes del microcontrolador están programadas para mantener una sincronía en el encendido y apagado de los MOSFETS, es por ello que deben de cumplir las características ideales para tal fin. Una de ellas es la frecuencia que debe mantener cada una, la cual será de 60[Hz], ya que es la frecuencia de la línea comercial (red eléctrica) para todos los aparatos electrodomésticos, y la cuál necesitamos emplear para que la señal que generemos de salida en el UPS sea lo más parecido a esta. Otra es el ciclo de trabajo del tren de pulsos (Señal de oscilación), el cual se estableció en 40[%] debido a su alta eficiencia de operación y a que nos permite mantener una guarda de protección, esto para que las señales (Pulsos) nunca se lleguen a transponer y de esta forma evitar corto circuitos en el flujo de corriente del dispositivo inversor.

Teniendo estas consideraciones en cuenta, y las características de polarización, configuración y conexión del microcontrolador, podemos proseguir a generar un algoritmo de programación que nos sirva para la generación de los pulsos de control en el microcontrolador PIC.

## Algoritmo de programación

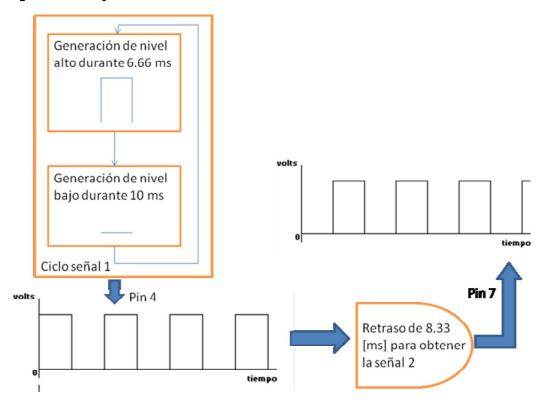

- \* El primer paso consiste en establecer un ciclo que se encuentre constantemente generando pulsos de oscilación.

- Estos pulsos deben oscilar con periodos que cumplan con los tiempos correctos en sus dos estados (0 y 5 V<sub>dc</sub>, señales lógicas), los cuales para una frecuencia de 60[Hz] y un ciclo de trabajo al 40% son:

Pulso Alto: 6.66 [ms]

Pulso Bajo: 10 [ms]

- \* Una vez obtenida ésta señal a través de una de las salidas del PIC, procedemos al segundo paso, que consiste en generar una segunda señal de oscilación.

- Deberá tener una sincronía con la primera señal, teniendo un retraso y una separación entre pulsos de 1.67 [ms].

- Esto lo podemos obtener a partir de establecer un retraso en la primera señal de 8.33 [ms] y dirigiéndola a otro de los pines de salida del PIC.

# Diagrama de Flujo