# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

# **FACULTAD DE INGENIERÍA**

# MANUAL PARA PROGRAMAR FPGA USANDO LENGUAJE VHDL, HARDWARE Y SOFTWARE DE ALTERA

# **MATERIAL DIÁCTICO**

Que para obtener el título de

**Ingeniero Mecatrónico**

## PRESENTA

Gerardo Martínez Urbina

# **ASESOR DE MATERIAL DIDÁCTICO**

Dr. Octavio Días Hernández

Ciudad Universitaria, Cd. Mx., 2023

## **AGRADECIMIENTOS**

Este trabajo es el resultado de la conclusión de la etapa estudiantil vivida desde la etapa de la educación preescolar y este camino siempre hubo personas quienes fueron importantes para lograr todas esas metas. En primer lugar, agradezco a la madre y al padre celestial a quienes siempre encomendé mis logros me dirigen a ser una persona buena. Los siguientes son mi madre y padre quienes siempre me dieron su apoyo y amor incondicional en las buenas y en las malas lo cual me permitió convertirme en un profesional. También agradezco a mi hermana y a mi hermano quienes son mis compañeros de vida y me permiten compartir mis logos para que ellos sigan ese ejemplo. Los abuelos son personas muy sabias a quienes siempre recurría para pedir ayuda y gracias a ellos pude tomar las mejores decisiones. Agradezco a todas las demás personas y seres que forman parte de esta gran familia que con sus valores y su apoyo incondicional forjaron a esta gran persona.

Igualmente se agradece a la comunidad Facultad de Ingeniería de la Universidad Nacional Autónoma de México donde los docentes y estudiantes quienes formaron parte de los equipos de trabajo donde yo tuve la oportunidad de participar durante los cinco años de duración del plan de estudios de la carrera de Ingeniería Mecatrónica. En especial, agradezco al Dr. Octavio Díaz Hernández quien supervisó la elaboración de este trabajo, así como el apoyo personal brindado.

Se agradece a la UNAM-DGAPA que a través del proyecto PAPIME con clave PE102022 y titulado "Diseño de prácticas de laboratorio para las asignaturas del área de electrónica en la Licenciatura de Órtesis y Prótesis", fue realizado este trabajo.

## **PREFACIO**

El presente manual de prácticas es un conjunto de herramientas para el diseño de circuitos, programación y aplicaciones de los dispositivos FPGA. El propósito es que el lector conozca una herramienta adicional para el desarrollo de sistemas digitales y que puedan resolver problemas ingenieriles o de la vida cotidiana.

El alcance principal de este escrito es que los alumnos aprendan a manejar los lenguajes de programación empleados en estos dispositivos, así como el uso de los distintos periféricos que necesitarán los FPGA para formar un sistema más elaborado y que sea útil.

#### **OBJETIVOS**

#### Objetivo general

Proponer un manual para programar FPGA usando lenguaje VHDL, así como el hardware y software de ALTERA requeridos.

#### Objetivos específicos

- Mostrar los comandos y estructuras básicas del lenguaje VHDL

- Implementar circuitos digitales usando lenguaje descriptivo

- Manipular el software Quartus II 13.0sp1 para programar en código VHDL y por diagrama de bloques

- Implementar dispositivos periféricos conectados el FPGA para:

- Obtener información de sensores analógicos

- o Proponer el control de actuadores

- Desplegar información en pantallas LCD

#### **CARRERAS AFINES**

- Ingeniería Eléctrica y Electrónica

- Ingeniería Mecatrónica

- Ingeniería en Sistemas Biomédicos

- Licenciatura en Órtesis y Prótesis

Nota

La asignatura donde está contenida el tema de los FPGA es la de circuitos digitales para las carreras de Ingeniería Mecatrónica, Sistemas Biomédicos y Licenciatura en Órtesis y Prótesis. En el caso de la carrera de Ingeniería Eléctrica y Electrónica es la asignatura de diseño digital.

# POR QUÉ ES APOYO A LA DOCENCIA

Este manual pretende que los docentes de las carreras que involucren la electrónica digital en sus planes de estudio puedan incluir en sus cursos el estudio e implementación de los FPGA. Se pretende que las prácticas propuestas formen parte de la evaluación de los alumnos con el objetivo de que puedan tener una herramienta más para resolver problemas de ingeniería.

# **JUSTIFICACIÓN**

Los FPGA son un tipo de dispositivo electrónico programable donde su estructura interna posee un número determinado de bloques los cuales contienen miles de compuestas lógicas, por lo tanto, esta se puede implementar cualquier tipo de circuito digital.

Su principal ventaja es que pueden ejecutar procesos de forma paralela y usar altas frecuencias de trabajo lo que permite aumentar el rendimiento de los sistemas implementados en el FPGA.

# A QUIÉN VA DIRIGIDO

Se ha mencionado que este manual tiene el propósito a aquellos alumnos de ingeniería que estudien el área de electrónica, para poder extraer el conocimiento de este documento es importante que los alumnos tengan los conocimientos que se enlistan a continuación:

- Interpretación de diagramas electrónicos

- Algebra de Boole

- Circuitos digitales combinacionales

- Circuitos digitales secuenciales (por ejemplo, máquinas de estado)

Además, se requieren conocimientos básicos de programación, en especial el entendimiento de los distintos tipos de variables como lo que serían variables enteras, arreglos, cadenas, bits y caracteres. También se requiere de estructuras lógicas de control como lo son "if", "else" y "case".

Es importante también que el lector debe estar dispuesto a adquirir los dispositivos necesarios para la implementación de las prácticas de este manual con la finalidad de que el conocimiento se enriquezca y sea comprensible los conceptos que en algunas ocasiones pueden ser más complejos.

# QUIÉN LO VA A USAR

- Profesores que quieran incluir en sus actividades teórico-prácticas el estudio de los FPGA

- Alumnos de las carreras antes mencionadas que quieran especializarse en el área de la electrónica y la instrumentación

# **CONTENIDO**

| AGRADECIMIENTOSi                                                   | ii  |

|--------------------------------------------------------------------|-----|

| PREFACIO                                                           | V   |

| CONTENIDOi                                                         | ĺΧ  |

| RESUMEN                                                            | 1   |

| CAPÍTULO 1 DISPOSITIVOS LÓGICOS PROGRAMABLES                       | 3   |

| 1.1 DISPOSITIVO LÓGICO PROGRAMABLE                                 | .3  |

| <ul> <li>1.1.1 DISPOSITIVOS LÓGICOS PROGRAMABLES SIMPLES</li></ul> | . 4 |

| 1.2.1 CYCLONE II EP2C5T144                                         | . 8 |

| 2.1 VALORES NUMÉRICOS                                              | 0   |

| 2.2 | CA    | RACTERES Y CADENAS                                   | 12 |

|-----|-------|------------------------------------------------------|----|

| 2.3 | EST   | TRUCTURA DE CÓDIGO                                   | 13 |

|     | 2.3.1 | ARCHIVOS DE BIBLIOTECA                               | 13 |

|     | 2.3.2 | ESTRUCTURA ENTITY                                    | 14 |

|     | 2.3.3 | ESTRUCTURA ARCHITECTURE                              | 16 |

|     | 2.3.4 | UNIDADES SECUENCIALES                                | 17 |

| 2.4 | TIP   | OS DE DATOS                                          | 19 |

|     | 2.4.1 | STD_LOGIC                                            | 19 |

|     | 2.4.2 | STD_LOGIC_VECTOR                                     | 19 |

|     | 2.4.3 | SIGNED / UNSIGNED                                    | 20 |

|     | 2.4.4 | NATURAL                                              | 21 |

|     | 2.4.5 | INTEGER                                              | 21 |

|     | 2.4.6 | REAL                                                 | 21 |

|     | 2.4.7 | CHARACTER                                            | 22 |

|     | 2.4.8 | STRING                                               | 22 |

| 2.5 | TIP   | OS DE VARIABLES                                      | 23 |

|     | 2.5.1 | CONSTANT                                             | 23 |

|     | 2.5.2 | SIGNAL                                               | 23 |

|     | 2.5.3 | VARIABLE                                             | 23 |

|     | 2.5.4 | TYPE                                                 | 24 |

| 2.6 | OPI   | ERADORES                                             | 25 |

|     | 2.6.1 | OPERADORES ARITMÉTICOS CON NÚMEROS ENTEROS           | 25 |

|     | 2.6.2 | OPERADORES ARITMÉTICOS DE NÚMEROS CON PUNTO FLOTANTE | 26 |

|     | 2.6.3 | OPERADORES LÓGICOS                                   | 27 |

| 2.7 |       | TRUCTURAS LÓGICAS Y CICLOS                           |    |

| CAPÍTULO 3 PROGRAMA QUARTUS II 13.0                 | 31 |

|-----------------------------------------------------|----|

| 3.1 INSTALACIÓN                                     | 31 |

| 3.2 CREACIÓN DE PROYECTOS                           | 34 |

| 3.3 CREACIÓN DE ARCHIVOS VHDL                       | 38 |

| 3.4 DIAGRAMAS DE BLOQUES                            | 41 |

| 3.4.1 CREACIÓN DE PROYECTOS CON DIAGRAMA DE BLOQUES | 41 |

| 3.4.2 CREACIÓN DE BLOQUES USANDO CÓDIGO VHDL        | 43 |

| 3.4.3 CONSTRUCCIÓN DEL DIAGRAMA DE BLOQUES          | 49 |

| 3.5 COMPILACIÓN DE PROYECTOS                        | 52 |

| 3.6 CONFIGURACIÓN DE PINES DEL FPGA                 | 54 |

| 3.7 SIMULACIÓN                                      | 56 |

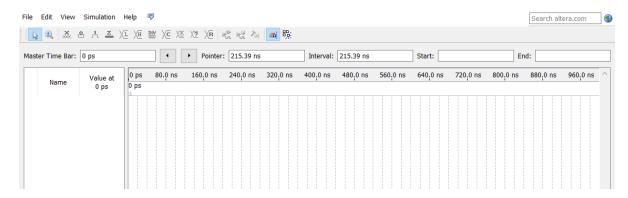

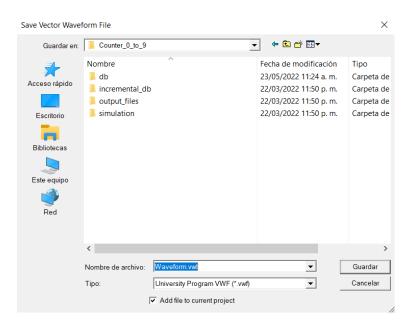

| 3.7.1 CREAR ARCHIVO WAVEFORM                        | 56 |

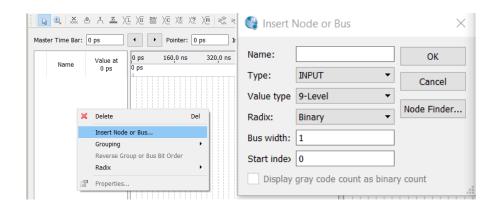

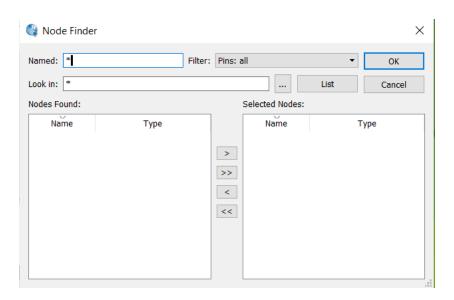

| 3.7.2 ENTRADAS Y SALIDAS                            | 58 |

| 3.7.3 CONDICIONES EN LAS ENTRADAS                   | 61 |

| 3.7.4 SIMULACIÓN                                    | 62 |

| 3.7.5 OBSERVACIONES DEL SIMULADOR                   | 65 |

| 3.8 PROGRAMACIÓN DEL FPGA CON USB BLASTER           | 65 |

| 3.8.1 INSTALACIÓN DEL CONTROLADOR                   | 66 |

| 3.8.2 MODO JTGA                                     | 70 |

| 3.8.3 MODO AS                                       | 72 |

| CAPÍTULO 4 CIRCUITOS BÁSICOS CON FPGA               | 75 |

| 4.1 ENCENDIDO DE UN LED MEDIANTE UN BOTÓN           | 75 |

| 4.2 PARPADEO DE UN LED                              | 79 |

| 4.3  | PROGRAMACIÓN DE UNA FUNCIÓN BOOLEANA                                                                                                                                                           | 84                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

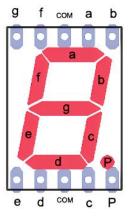

| 4.4  | DECODIFICADOR DE 4 BITS A 7 SEGMENTOS                                                                                                                                                          | 88                       |

| 4.5  | CONTADOR ASCENDENTE Y DESCENDENTE                                                                                                                                                              | 93                       |

| CAPÍ | TULO 5 HARDWARE CON FPGA                                                                                                                                                                       | 101                      |

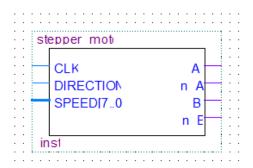

| 5.1  | CONTROLADOR DE UN MOTOR PASO A PASO                                                                                                                                                            | 101                      |

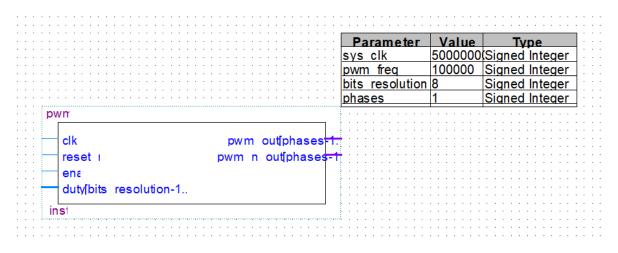

| 5.2  | GENERADOR DE UNA SEÑAL PWM                                                                                                                                                                     | 112                      |

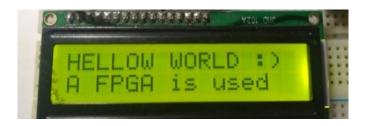

| 5.3  | EMPLEDO DE UNA PANTALLA LCD 16 X 2                                                                                                                                                             | 124                      |

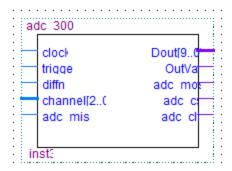

| 5.4  | CONVERTIDOR ANALÓGICO A DIGITAL                                                                                                                                                                | 133                      |

| 5.5  | MEDICIÓN DE VOLTAJE                                                                                                                                                                            | 142                      |

| 5.6  | CONTROL DE VELOCIDAD DE UN MOTOR DE CD                                                                                                                                                         | 147                      |

|      |                                                                                                                                                                                                |                          |

| APÉN | NDICE                                                                                                                                                                                          | 157                      |

|      | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO                                                                                                                                                    |                          |

| ΑE   |                                                                                                                                                                                                | 157                      |

| ΑE   | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO                                                                                                                                                    | 157                      |

| ΑE   | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO                                                                                                                                                    | 157                      |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144                                                                                                                          | 157<br>157<br>158        |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144                                                                                                                          | 157157158161             |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144  A.2 CYCLONE IV EP4CE6E22C8N  ÓDIGOS DE LAS PRÁCTICAS  B.1 ENCENDIDO DE UN LED MEDIANTE UN BOTÓN                         | 157157158161162          |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144  A.2 CYCLONE IV EP4CE6E22C8N  ÓDIGOS DE LAS PRÁCTICAS  B.1 ENCENDIDO DE UN LED MEDIANTE UN BOTÓN  B.2 PARPADEO DE UN LED | 157157158161161162       |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144                                                                                                                          | 157157158161162163       |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144                                                                                                                          | 157157158161162163163    |

| A E  | SPECIFICACIONES DE LAS PLACAS DE DESARROLLO  A.1 CYCLONE II EP2C5T144                                                                                                                          | 157157158161162163163164 |

| B.9 MEDICIÓN DE VOLTAJE                     | 173 |

|---------------------------------------------|-----|

| B.10 CONTROL DE VELOCIDAD DE UN MOTOR DE CD | 174 |

| C ARCHIVOS DE BILBIOTECA                    | 176 |

| C.1 CONTROLADOR PARA MOTOR PASO A PASO      | 176 |

| C.2 GENERADOR DE PWM                        | 180 |

| C.3 CONVERTIDOR ANALÓGICO A DIGITAL MCP3008 | 184 |

| C.4 CONTROLADOR DE UNA PANTALLA LCD 16 X 2  | 188 |

| C.5 ARCHIVO DE BIBLIOTECA "instrument.vhd"  | 195 |

| CARPETA VIRTUAL                             | 197 |

| REFERENCIAS                                 | 199 |

# **RESUMEN**

#### **Antecedentes**

Los dispositivos lógicos programables son una herramienta importante para el diseño de circuitos digitales debido a que rigen el funcionamiento de cualquier dispositivo inteligente que sea usado actualmente. Entre ellos sen encuentran los FPGA que, por sus siglas en inglés, se definen como matrices de compuertas lógicas programables las cuales son utilizadas para el procesamiento de datos y señales lógicas con propósitos específicos.

Los FPGA, como su nombre lo indica, contienen una matriz de miles de bloques, los cuales contienen un número definido de compuertas lógicas, donde se manipulan las interconexiones para dar forma al circuito lógico que se está diseñando. Por esta razón, la programación de estos dispositivos es descriptiva, es decir, el diseñador tiene que introducir en el código el comportamiento del circuito en respuesta a las señales de entrada. Los lenguajes de programación más usados para programar los FPGA son VHDL y Verilog.

#### **Objetivo**

Este manual permitirá a los docentes y estudiantes de carreras relacionadas con la electrónica digital implementar los FPGA para resolver problemas de ingeniería.

#### Metodología

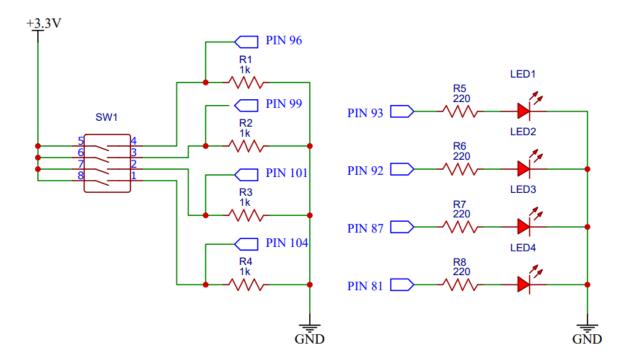

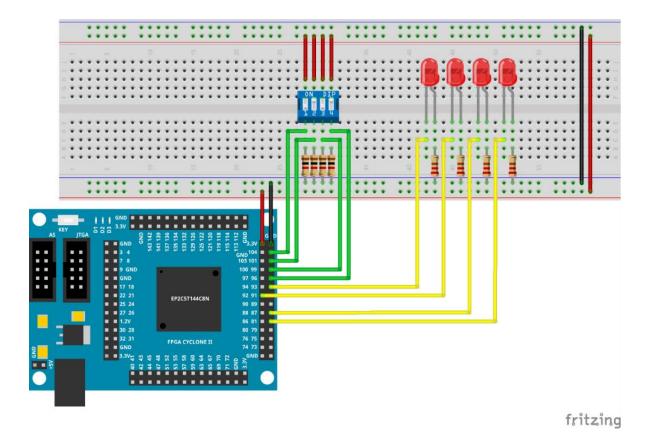

Se propusieron once prácticas divididas en dos secciones: la primera sección (de la práctica 1 a la 5) contempla la implementación de circuitos electrónicos digitales básicos para el entendimiento del lenguaje VHDL. La siguiente sección (de la práctica 6 a la 11) implementa dispositivos periféricos conectados al FPGA que permiten accionar motores, leer señales digitales y analógicas con el objeto de que el lector sea capaz de elaborar un circuito digital con FPGA.

#### Resultados

Cada una de las prácticas contiene una solución propuesta por el autor de este trabajo.

#### **Impacto**

Se pretende que los alumnos que estudien este manual sean capaces de un FPGA programable que será una alternativa al uso de los microcontroladores y de esta manera puedan aprovechar sus ventajas.

# CAPÍTULO 1 DISPOSITIVOS LÓGICOS PROGRAMABLES

### 1.1 DISPOSITIVO LÓGICO PROGRAMABLE

Un dispositivo electrónico programable (PLD, por sus siglas en inglés) es un dispositivo electrónico con el que se puede implementar el diseño lógico para crear un circuito digital y se pueden reconfigurar cuantas veces sea necesario. "El PLD proporciona a los programadores la flexibilidad para implementar diferentes diseños complejos para diversas aplicaciones de circuitos" (S. Parab, S. Gad, & Naik, 2018, pág. 2). Por lo tanto, se pueden implementar distintos tipos de circuitos desde memorias PROM, procesadores, incluso pueden emular el funcionamiento de un microcontrolador. Los PLD se dividen en dos grandes ramas: la **primera familia** consiste en dispositivos lógicos que cumplen una función específica y por lo tanto solo son programados una sola vez por el vendedor; la **segunda familia** abarca a los dispositivos que son programados por el usuario y pueden programarse las veces que sea necesario.

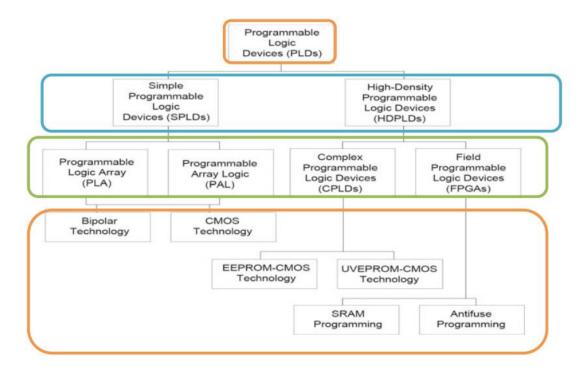

Los PLD, que pertenezcan a la segunda familia antes mencionada, son clasificados en dos grandes ramas, la primera de ellas consiste en los SPLD (dispositivos lógicos programables simples) y los HDPLD (dispositivos lógicos programables de alta densidad), en la Figura 1.1 se puede apreciar un diagrama esquemático de cada una de las familias.

.

Figura 1.1 Familia de los PLD (S. Parab, S. Gad, & Naik, 2018, pág. 5).

#### 1.1.1 DISPOSITIVOS LÓGICOS PROGRAMABLES SIMPLES

Los dispositivos lógicos programables simples (SPLD, por sus siglas en inglés) son dispositivos que poseen una matriz de compuertas lógicas, las cuales ascienden a un número de varios de cientos, y son capaces de guardar la configuración que les ha proporcionado el diseñador. Se caracterizan por su rápida respuesta debido al bajo número de conexiones que posee internamente y por lo tanto consumen poca energía. De esta rama del SPLD se derivan del PLA (arreglos lógicos programables) que utilizan tecnología bipolar mientras que los PAL (matriz lógica programable) utilizan tecnología CMOS (complementary metal-oxide-semiconductor).

#### 1.1.2 DISPOSITIVOS LÓGICOS PROGRAMABLES DE ALTA DENSIDAD

Como su nombre lo indica, los HDPLD son dispositivos que tienen una alta densidad de arreglos de compuertas lógicas las cuales son agrupadas en bloques permitiendo que exista mayor flexibilidad, comparado con los SPLD, y capacidad de realizar conexiones entre los

bloques lógicos los cuales contienen compuertas AND y OR. Esta variante permite al diseñador implementar diseños lógicos complejos debido a su flexibilidad.

Los **CPLD** (dispositivos lógicos programables complejos) tienen un funcionamiento similar a una memoria EPROM (Erasable Programmable Read-Only Memory) o EEPROM (Electric Erasable Programmable Read-Only Memory) debido a que no pierden su estructura lógica programada al interrumpirse la alimentación, por lo tanto, se considera que la lógica de estos dispositivos es no volátil. Se caracterizan también por ser pequeños y baratos debido a que el número de bloques lógicos que posee es considerablemente menor a un FPGA (Field Programable Gate Array, en inglés).

Los **FPGA**, que traducido al español significa matriz de compuestas lógicas programables, tienen un funcionamiento similar a las memorias que almacenan datos de manera temporal, tales como las RAM (Random Access Memory) y SRAM (Static Random Access Memory) lo que permite que puede programarse un sinnúmero de veces, aunque si es interrumpida la alimentación se pierde el circuito lógico programado. Al igual que los PLD, poseen un número elevado bloques lógicos lo que permite a los FPGA sintetizar circuitos más complejos, por lo tanto, su tamaño es mayor y su costo es considerablemente elevado.

#### 1.2 FPGA RECOMENDADO PARA ESTE MANUAL

Los FPGA, son dispositivos que no son fáciles de adquirir ya que su precio puede ser elevado, por lo que se recomienda adquirir las siguientes placas de desarrollo que son fáciles de encontrar y tienen un precio accesible. Este manual es compatible con los FPGA fabricados por ALTERA, por lo que se recomienda usar cualquiera de las siguientes tarjetas que se proponen.

#### **1.2.1 CYCLONE II EP2C5T144**

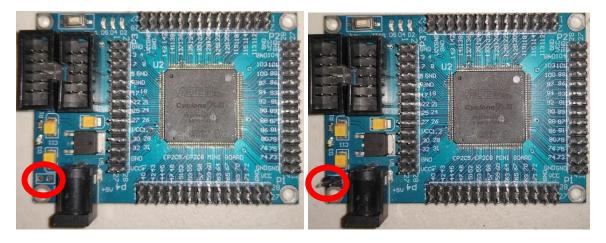

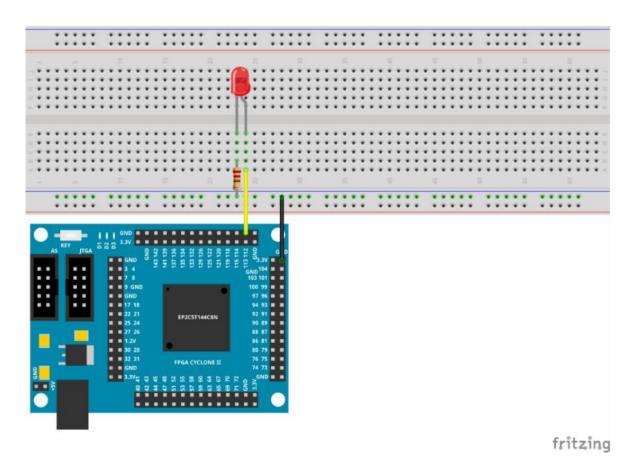

Figura 1.2 FPGA Cyclone II de ALTERA

En la Figura 1.2 se muestra una fotografía de la tarjeta de desarrollo que se puede adquirir en las tiendas de electrónica. Dicha tarjeta posee 89 pines que pueden ser utilizados como entradas y salidas, una RAM de varios bloques de 4 Kbits (total: 119.898 bits), una EEPROM EPCS4 de 4 Mbit (sólo programable a través del puerto AS).

Se sabe que los voltajes de alimentación normalizados más comunes son 3.3V y 5V, pero la mayoría de los dispositivos periféricos como convertidores analógicos a digital (ADC) y pantallas de cristal líquido (LCD) requieren por defecto una alimentación de 5V. Si se está trabajando las prácticas con la tarjeta de desarrollo Cyclone IV no se tendrá ningún problema ya que posee reguladores y pines para ambos voltajes.

En cambio, la tarjeta Cyclone II (en la cual están basados los diagramas y conexiones de este manual) no posee reguladores de 5 V y, por lo tanto, no contiene pines para dicho voltaje de alimentación por defecto. Este problema se puede resolver de la siguiente forma:

Figura 1.3 Ubicación de los pines de alimentación de 5 V en la Cyclone II

En la Figura 1.3 se aprecia que la placa de desarrollo tiene dos pequeños agujeros donde puede soldarse un par de terminales conocidos como headers (ya sean macho o hembra). Por lo que se debe soldar ese par de headers con la finalidad de que se requiera usar del voltaje suministrado al FPGA no se tenga que usar fuentes externas de voltaje.

El pin del lado izquierdo transmite la corriente eléctrica con un voltaje igual al de la alimentación, por lo tanto, se recomienda alimentar el FPGA con una fuente de 5 V para alimentar otros circuitos que requieran ese voltaje de alimentación. En cuanto a la corriente de la fuente usada debe ser capaz de suministrar más de 1 A ya que el modelo Cyclone II consume una corriente de alrededor de 600 mA, por lo tanto, es normal que presente un aumento de temperatura el dispositivo. Este detalle no se presenta en el modelo Cyclone IV ya que al ser un modelo más reciente consume menos energía lo que permite que sea alimentado con una PC mediante un puerto USB o cualquier eliminador de voltaje menor a 1 A.

#### 1.2.2 CYCLONE IV EP4CE6E22C8N

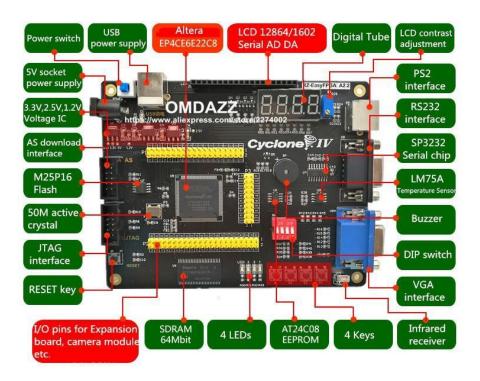

Figura 1.4 Tarjeta de desarrollo Cyclone IV de ALTERA.

La Figura 1.4 muestra una fotografía de una segunda tarjeta de desarrollo que puede usar para este manual. Es ligeramente más costosa que el modelo anterior, posee 88 pines que pueden ser configurados como entrada y salida por lo que la diferencia es notoria con respecto al modelo anterior, debido a que este FPGA tiene cuatro botones, un dip-switch de cuatro interruptores, cuatro despliegues de siete segmentos, cuatro leds y un puerto de 16 pines para colocar una pantalla de cristal líquido. Adicionalmente tiene soldada una memoria EEPROM tipo M25P16 de 16 Mb programable por el puerto AS, una memoria SDRAM de 64 Mb y una memoria EEPROM de comunicación por I2C modelo AT24C08.

En el apéndice A se pueden consultar los diagramas de conexiones de ambas tarjetas de desarrollo y, en el caso de la tarjeta con Cyclone IV, se tiene también la configuración se sus pines para cada uno de los módulos que tiene integrado.

# **CAPÍTULO 2**

# INTRODUCCIÓN A LENGUAJE VHDL

Los FPGA son capaces de emular circuitos lógicos complejo a través de sus matices de compuertas lógicas que se interconectan entre ellas, para ello utilizan el lenguaje de programación descriptivo que permita establecer el comportamiento del circuito lógico a implementar.

VHDL es uno de los tantos lenguajes de programación cuyo funcionamiento consiste en utilizar un lenguaje de descripción de hardware el cual describe el funcionamiento y la estructura de un circuito lógico que será posteriormente programado en el FPGA.

"VHDL permite la síntesis de circuitos, así como la simulación de circuitos. El primero es la traducción de un código fuente a una estructura de hardware que implementa la funcionalidad deseada, mientras que el segundo es un procedimiento de prueba para asegurar que tal de hecho, la funcionalidad se logra mediante el circuito sintetizado." (A. Pedroni, 2004, pág. 3)

Anteriormente se mencionó que el VHDL se utiliza para describir el funcionamiento de circuitos digitales por lo que inevitablemente se trabaja con señales digitales; las cuales solo pueden existir dos posibles valores: 1 (alto) y 0 (bajo).

VHDL permite también ejecutar operaciones aritméticas (ejem. sumar, restar, dividir y multiplicar), es capaz de sintetizar números enteros y con punto flotante usando los archivos de biblioteca adecuadas.

Debido a su naturaleza descriptiva, es capaz de ejecutar estructuras lógicas usadas en otros lenguajes de programación, tales como *if/else y case* así como estructuras cíclicas como *for* y *while*. También tiene la capacidad de declarar funciones y ser llamadas en cualquier parte del código.

## 2.1 VALORES NUMÉRICOS

#### Números binarios

Los números binarios son la base para el diseño digital y por lo tanto son la manera en que se pueden trabajar y sintetizar las señales digitales en VHDL. En este lenguaje de programación pueden existir números binarios de un solo bit y se representan de esta manera.

```

a \le '0'; -- a = 0

```

En el ejemplo anterior la variable "a" almacena el número 0 en un número de un solo bit. La asignación de valores en VHDL se realiza con el símbolo "<=" y, de manera similar al lenguaje C, cada línea de código se debe finalizar con ";". Por otro lado, para realizar comentarios en VHDL se usa doble guion "--" y seguido del comentario, estos se usarán para escribir el valor de las variables en esta sección.

En la línea mostrada anteriormente, se usaron dos apóstrofos para escribir un número de un solo bit el cual solo puede tener dos posibles valores (0 y 1), aunque se puede usar la siguiente notación:

```

a <= b"1" -- a = 1;

```

Para representar números binarios de dos o más bits, la variable que contenga el valor debe declararse con anterioridad como un **vector de bits**. Puede usarse la notación anterior y solamente se agregan más elementos dentro de dos comillas dobles.

```

b <= b"1001"; -- b = 9

c <= b"11110001"; -- c = 241

```

La variable "b" está declarada como un número binario de 4 bits cuyo valor corresponde a 9, mientras que "c" es un número de 8 bits y representa al número 241, por lo tanto, sus valores máximos son 15 y 255 respectivamente.

La notación usada anteriormente incluye una b antes de escribir el número binario dentro de las comillas dobles, pero se pueden suprimir y el código funciona de igual forma.

```

b <= "1001";

c <= "11110001";

```

#### Números hexadecimales

La letra "b" en la notación anterior indica que se trata de un número binario y de esa manera VHDL identifica que se está usando números de base 2. Si "b" es reemplazada por la letra "x", representaría a los números base 16 o mejor conocidos como números hexadecimales. En el siguiente ejemplo se asigna a la variable "d" el valor de 205 representado en número hexadecimal.

```

d <= x"CD";</pre>

```

#### Números octales

Los números base 8 o también conocidos como octales se representan reemplazando la letra "h" por la letra "o" antes de escribir las comillas dobles. En el siguiente ejemplo, la variable e se asigna el valor 205 usando un número octal.

```

e <= o"315";

```

Las variables d y e han implícitamente son números de 8 bits por lo que su rango de valores es entre 0 y 255 sin importar que se usen binarios, octales o hexadecimales. La declaración de vectores de bit se explicará a detalle en la sección 2.4.

#### Números decimales

Los números base 10, mejor conocidos como decimales, son sintetizables en VHDL. En las siguientes líneas de código del siguiente ejemplo se muestra la asignación un número natural a la variable "f", para la variable "g" se asigna un entero negativo y por último a "h" se asigna un número real con punto flotante.

```

f <= 143;

g <= -17;

h <= -3.14159;

```

#### 2.2 CARACTERES Y CADENAS

Los caracteres pueden usarse también en VHDL, pero como en cualquier lenguaje, las variables deben declararse para albergar caracteres o cadenas. En el siguiente ejemplo "i" se ha declarado para almacenar caracteres y se le asigna el carácter "+". Para cualquier carácter, se debe incluir ente dos apóstrofos:

```

i <= '+';

```

En el siguiente ejemplo, para la misma variable "i", se hace uso de una función donde el argumento es el número que corresponde al carácter "+" en el código ASCII.

```

i <= character'val(24);</pre>

```

De una manera similar, las cadenas se escriben entre dos comillas dobles. En los siguientes ejemplos, la variable "j" se ha declarado una cadena de 6 caracteres, por lo tanto, la cadena asignada debe tener la misma extensión. De igual manera la variable "k" se ha declarada una cadena de 2 caracteres. La declaración de cadenas se explicará a detalle en la sección 2.4.8.

```

j <= "Hellow";

k <= ":)";</pre>

```

Dos o más cadenas pueden concatenarse para crear una sola cadena, para ello se usa "&" entre cada cadena. En el siguiente ejemplo "l" se ha declarado una cadena de 13 caracteres y en la asignación del su valor, se concatenan tres cadenas y un carácter.

```

1 <= "Hello" & " " & "world" & ":)";</pre>

```

En la concatenación de cadenas, se puede usar otras variables que almacenen tanto cadenas como caracteres. En el siguiente ejemplo, la asignación de la cadena a la variable "l" se realiza con las variables "j" y "k" de los ejemplos anteriores y el resultado es exactamente el mismo.

```

1 <= j & " " & "world" & k;</pre>

```

## 2.3 ESTRUCTURA DE CÓDIGO

#### 2.3.1 ARCHIVOS DE BIBLIOTECA

Esta sección del código, como en otros lenguajes de programación, consiste en la declaración de los archivos de bibliotecas que habilitan el uso de tipos de datos, operadores y funciones. En VHDL se usa por defecto el archivo de biblioteca **ieee** el cual contiene paquetes de código que se declaran de manera individual para usar su contenido en el código principal. Existen diversos paquetes para diferentes propósitos por lo que se considera para este manual usar tres paquetes que cubren lo necesario para el funcionamiento de las actividades propuestas en las secciones subsecuentes.

#### Paquete std\_logic\_1164

Contiene el tipo de variable *STD\_LOGIC* el cual permite declarar números de un solo bit. También incluye la variante *STD\_LOGIC\_VECTOR* que son arreglos o vectores de bits que permiten representar números de dos o más bits. El paquete define los valores que representan los posibles estados lógicos: "1" (alto) y "0" (bajo). El paquete permite sintetizar otros estados lógicos, que no se usarán en este manual, como "u" (no asignado), "z" (alta impedancia) y "-" (no importa el valor).

#### Paquete numeric\_std

El paquete permite manipular números con signo (UNSIGNED), que se representan como arreglos de bits similar a los STD\_LOGIC\_VECTOR, y con signo (SIGNED) que, con base en el método de complemento a 2, agrega el bit significativo al arreglo para definir si el número es positivo o negativo. Además, permite manipular números naturales y números enteros (con y sin signo). Este paquete también contiene a los operadores aritméticos (suma, resta, multiplicación y división) para realizar operaciones con números enteros, además se pueden escribir en notación científica y ejecutar funciones que puedan realizar la conversión los *STD\_LOGIG\_VECTOR* a números enteros y viceversa.

#### Paquete math\_real

Este paquete trabaja de manera similar a **numeric\_std** con la diferencia que permite manipular números con punto flotante, incluye constantes matemáticas tales como el número Pi y la constante de Euler. El paquete contiene las operaciones matemáticas básicas (suma, resta multiplicación y división) para operar con números flotantes y añadiendo operaciones matemáticas avanzadas como potencias, raíces y funciones trigonométricas.

#### Declaración de los archivos de bibliotecas y los paquetes

Para declarar un archivo de biblioteca primero debe escribirse en las primeras líneas de código siguiendo la siguiente sintaxis:

```

library [library name]

```

Mientras que para declarar los paquetes de los archivos de biblioteca se usa la siguiente estructura:

```

use [library name].[package name].all;

```

En el siguiente ejemplo se muestra la declaración del archivo de biblioteca **ieee** y los paquetes mencionados anteriormente los cuales se usarán en cada una de las prácticas que se propongan en las secciones subsecuentes:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.math real.all;

```

#### 2.3.2 ESTRUCTURA ENTITY

Esta sección del código define la estructura externa del circuito digital la cual es representada en el código. En ella se establece un nombre, así como el número de señales externas que interactúan en el circuito. En esta sección se utiliza una función llamada *port*() en la cual se listan todas las señales de entrada y salida del circuito.

```

entity entity_name is

port (

port_1_name: port_mode signal_type;

port_2_name: port_mode signal_type;

port_3_name: port_mode signal_type;

port_n_name: port_mode signal_type

);

end entity;

```

"port\_mode" puede ser reemplazado por la palabra in que define que se trata de una entrada o también se puede emplear out que especifica que es una salida. Por otro lado, en lugar de "signal type" pueden usarse las variables STD\_LOGIC para señales de un solo bit o también STD\_LOGIC\_VECTOR para señales de dos o más bits. En el siguiente ejemplo se ilustra la declaración de una entidad.

```

entity example is

port (

port_A: in std_logic;

port_B: in std_logic_vector (3 downto 0);

port_C: out std_logic_vector (6 downto 0);

port_D: out std_logic

);

end entity;

```

Adicionalmente, existe la función **generic**() que puede ser usada de manera opcional la cual declara valores paramétricos que pueden ser usados en cualquier parte del código. Para usar la función se escribe:

```

generic (

constant_1_name: constant_1_type := constant_1_value;

constant_2_name: constant_2_type := constant_2_value;

constant_3_name: constant_3_type := constant_3_value;

constant_n_name: constant_n_type := constant_n_value

);

```

Esta función se escribe antes de declarar la función **port**(). Usando el ejemplo anterior, se declara la función **generic**() para agregar parámetros:

```

entity example is

generic (

integer_constant: integer := 10;

simple_bit: std_logic :='0';

binary_number: std_logic_vector(2 downto 0) := "101"

);

port (

port_A: in std_logic;

port_B: in std_logic_vector (3 downto 0);

port_C: out std_logic_vector (6 downto 0);

port_D: out std_logic

);

end entity;

```

#### 2.3.3 ESTRUCTURA ARCHITECTURE

ARCHITECTURE es la sección del código que describe el funcionamiento del circuito lógico. Su estructura es la siguiente:

```

architecture architecture_name of entity_name is

--architecture_declarative_part

begin

--architecture_statements_part

end architecture;

```

La sección declarativa (situada entre **architecture** y **begin**) se puede escribir de manera opcional, en ella se declaran constantes, señales, variables internas y funciones que son utilizadas en el cuerpo de la arquitectura ("architecture\_declarative"). Este describe el funcionamiento y la estructura del circuito lógico. En el siguiente ejemplo se ilustra la escritura de una arquitectura para una compuerta XOR:

```

architecture main of example is

begin

c <= a xor b;

end architecture;</pre>

```

A continuación, se ilustra otro ejemplo que contiene declaraciones de constantes y señales internas que son usadas en la estructura de la arquitectura:

```

architecture behavioral of BLINKING is

```

```

constant count limit : integer := 12499999;

signal count : integer range 0 to 50e6 := 0;

signal led state : std logic;

begin

blink: process (CLK)

begin

if rising edge (CLK) then

if (count = count limit) then

led state <= not led state;</pre>

led <= led state;</pre>

count <= 0;

else

count<= count+1;</pre>

end if;

end if;

end process;

end architecture;

```

#### 2.3.4 UNIDADES SECUENCIALES

La estructura de ARCHITECTURE se caracteriza por contener a las unidades secuenciales, o conocidos también como PROCESS, que son la estructura principal para el funcionamiento del código en VHDL, ya que en ellos se escribe una sección, o completamente, el código que describe al circuito digital. Cada proceso representa una unidad secuencial que está sujeto al cambio de una o varias señales lógicas y cuando sucede el cambio por lo menos en una señal, se ejecuta el código contenido. Su estructura es la siguiente:

```

PROCESS_1_NAME: process (sensivity_1) is

begin

-- process statments

end process;

PROCESS_2_NAME: process (sensivity_2) is

begin

-- process statments

end process;

```

Dentro de las unidades secuenciales se ejecutan las estructuras lógicas tales como ciclos (for y while), if/else, case/when, que serán presentadas en la sección 2.7, y funciones elaboradas por el programador. Además, se pueden tener tantos procesos como sean necesarios y la gran ventaja es que cada proceso dentro del FPGA se ejecutará de manera paralela lo que permite obtener mejor velocidad y rendimiento. En el siguiente código se ejemplifica dos unidades secuenciales que se ejecutan cada vez que existe un cambio en las señales CLK y RESET.

```

PROCESS 1 : process (CLK) is

begin

if(CLK = '1') then

a <= '1';

b <= '0';

else

a <= '0';

b <= '1';

end if;

end process;

PROCESS 2 : process (CLK, RESET) is

begin

if(CLK = '0'and RESET = '1') then

c <= '0';

d <= '0';

else

c <= '1';

d <= '1';

end if;

end process;

```

#### 2.4 TIPOS DE DATOS

Existen diversos tipos de datos en VHDL donde cada uno cumple una función específica que permiten al diseñador crear el circuito lógico de la manera más eficiente. Para usarlos basta con declarar los archivos de bibliotecas y los paquetes que permitan usarlos, y después declararlos dentro de ARCHITECTURE usando la siguiente estructura:

```

[variable type] [data name] : [data type] := [data value];

```

Si no se requiere definir un valor al momento de declarar el dato, simplemente se omite la sección que asigna el valor y se cierra la línea de código después de asignar el tipo de dato:

```

[variable type] [data name] : [data type];

```

#### 2.4.1 STD\_LOGIC

Este tipo de dato permite usar un número binario de un solo bit el cual puede adquirir el valor 1 y 0. Para declararlo, se usa la sintaxis:

```

[variable_type] [name] : std_logic := '[bit_value]';

Ejemplo:

signal my_bit : std_logic := '0';

```

#### 2.4.2 STD\_LOGIC\_VECTOR

Este trabaja de manera similar al anterior, con la diferencia que alberga un vector de bits y es similar a los arreglos en otros lenguajes de programación. Puede representar buses de datos de más de dos bits, así como números binarios. La sintaxis para declararlos es la siguiente:

```

[variable_type] [name] : std_logic_vector([size - 1] downto 0):=

"[binary value]";

```

En el ejemplo, la variable "my\_bus" contiene un valor STD\_LOGIC\_VECTOR de que representa un bus de 8 bits:

```

signal my_bus : std_logic_vector (7 downto 0) := "10101111";

```

A continuación, se muestra cómo acceder a un bit en específico de la variable "my\_bus" usada anteriormente y se asigna a "my\_bit" declarada como *STD\_LOGIC*. Se quiere acceder al bit situado en la posición 3 (contando de derecha a izquierda contando desde 0) y el valor obtenido es 1.

$$my bit <= my bus(3);$$

En ocasiones se requiere obtener un conjunto de bits de un *STD\_LOGIC\_VECTOR*. En el siguiente ejemplo "my\_bus\_2" se ha declarado como un *STD\_LOGIC\_VECTOR* de 4 bits y el valor asignado corresponde a los bits de las posiciones 7, 6, 5 y 4 de la variable "my bus" y el resultado es el número binario "1010".

#### 2.4.3 SIGNED / UNSIGNED

Los tipos de dato con UNSIGNED trabajan de manera similar a los STD\_LOGIC\_VECTOR debido a que representan números binarios con más de dos bits mientras que los tipos SIGNED representan números binarios con signo donde, de acuerdo con el método de complemento a 2, el bit más representativo indica el signo del número. En la Tabla 2.1 se muestra la diferencia entra ambos tipos de dato:

Tabla 2.1 Diferencia entre SIGNED y UNSIGNED.

| Número<br>binario | SIGNED | USIGNED |

|-------------------|--------|---------|

| 000               | 0      | 0       |

| 001               | 1      | 1       |

| 010               | 2      | 2       |

| 011               | 3      | 3       |

| 100               | -4     | 4       |

| 101               | -3     | 5       |

| 110               | -2     | 6       |

| 111               | -1     | 7       |

La declaración de este tipo de datos usa la sintaxis:

```

[variable_type] [name] : signed([size-1] downto 0) :=

"[binary_number]";

[variable_type] [name] : unsigned([size-1] downto 0) :=

"[binary_number]";

```

La declaración de estos tipos de datos es semejante a los *STD\_LOGIC\_VECTOR* debido a que también almacenan vectores de bits. En el siguiente ejemploen las variables "num\_signed" y "num\_unsigned" se declaran números con y sin signo de 4 bits respectivamente:

```

signal num_signed : signed(3 downto 0) := "1011" ;

signal num unsigned : unsigned(3 downto 0) := "1011";

```

La variable "num\_signed" almacena el número binario de 1011 que, de acuerdo con el método de complemento a 2, equivale al valor numérico -5 mientras que para la variable "num unsigned" representa el número 11.

#### 2.4.4 NATURAL

Este tipo de dato almacena y permite operar los números naturales. En este tipo de dato existe un rango de operación el cual se encuentra desde 1 hasta  $2^{31} - 1$ .

```

[variable_type] [name] : natural := [value];

Por ejemplo:

signal natural name : natural := 32;

```

#### **2.4.5 INTEGER**

Este tipo de dato permite trabajar con el conjunto de los números enteros.

```

[variable_type] [name] : integer := [value];

Ejemplo:

signal int_num : integer := -150;

```

#### 2.4.6 **REAL**

Al usar este tipo de dato es posible manipular el conjunto de los números reales. VHDL utiliza 15 dígitos decimales de precisión.

```

[variable_type] [name] : real := [integer part . float part];

Ejemplo:

signal real num : real := -100.0;

```

#### 2.4.7 CHARACTER

Permite usar los valores alfanuméricos de la tabla del código ASCII.

```

[variable_type] [name] : character := '[character]';

Ejemplo:

signal real num : character := '$';

```

#### **2.4.8 STRING**

Son tipos de datos que almacenan arreglos de caracteres. En VHDL, las cadenas se declaran con un número finito de caracteres y cuando se realiza la asignación de un valor, debe coincidir con el tamaño de la cadena asignado.

```

[variable_type] [name]: string(1 to [string_lenght]):= "[string]";

```

La asignación de la longitud de la cadena se declara de manera similar a los STD\_LOGIC\_VECTOR, aunque éste ultimo los bits se cuentan de derecha a izquierda iniciando desde 0, mientras que las cadenas los caracteres se cuentan de derecha a izquierda iniciando desde 1:

```

signal my string: string(1 to 11):= "Hello world";

```

En este otro ejemplo se muestra cómo acceder a un carácter o una sección de la cadena.

```

my_char <= my_string(2);

string_2 <= my_string(4 to 8);</pre>

```

Donde el valor de "my\_char" es el carácter "e", siguiendo el conteo mencionado anteriormente. Mientras que para "string\_2" el valor es una sección de la cadena "my\_string" cuyo contenido es la cadena "lo w".

#### 2.5 TIPOS DE VARIABLES

#### 2.5.1 CONSTANT

Un tipo de variable CONSTANT almacena un valor de cualquier tipo de dato, no se permite el cambio del valor de la variable por lo que siempre será el mismo en cualquier parte del código. Es indispensable que exista un valor por defecto asignado.

```

constant my_constant_1 : std_logic := '1';

constant my_constant_2 : std_logic_vector(3 downto 0):= "1101";

constant my_constant_3 : integer := 100;

```

#### **2.5.2 SIGNAL**

Este tipo de dato tiene el propósito de representar las señales físicas internas del circuito que se está programando en el FPGA. Representan las conexiones internas entre las señales de entrada y salida de un circuito digital, aunque también pueden realizar conexiones entre otras señales internas. En las siguientes líneas se muestran algunos tipos de datos declarados como señales internas:

```

signal my_signal_1 : std_logic := '0';

signal my_signal_2 : std_logic_vector(3 downto 0);

signal my_signal_3 : integer;

```

#### 2.5.3 VARIABLE

Son similares a los SIGNAL debido a que se declaran de la misma forma:

```

variable my_variable_1 : std_logic := '0';

variable my_variable_2 : std_logic_vector(3 downto 0);

variable my_variable_3 : integer;

```

Su funcionamiento es casi idéntico con la gran diferencia de que SIGNAL se declara al inicio de la ARCHITECTURE lo que da el rol de una variable global, mientras que VARIABLE se declara dentro de la unidad secuencial en la cual se requiere su uso por lo tanto se considera una variable local. En el siguiente código se muestra un ejemplo de la utilización de ambos tipos de datos.

```

1 architecture main of example is

2 signal sig int : integer;

3 begin

4 SEQUENTIAL: process (clock) is

variable var int : integer;

6 begin

7

sig int <= 0;

var int := 0;

9

if(rising edge(clock)) then

10

sig int <= sig int + 1;

11

var int := var int + 1;

if(sig int = 10) then ...

12

13

elsif (var int = 10) then ...

14

end if;

end if;

15

16 end process;

17 end architecture;

```

#### 2.5.4 TYPE

Los tipos de variable TYPE definen a un conjunto específico de valores y variables que son establecidos por el diseñador. Dichos valores son semejantes a una cadena, debido a que cada uno representa una etiqueta que puede dar nombre a un estado del circuito secuencial y por esa razón son usados para crear máquinas de estado.

En el siguiente código se ejemplifica la declaración de un TYPE que define a un tipo de dato nombrado arbitrariamente como *states* y el cual define un conjunto de diez posibles valores. El siguiente ejemplo se muestra la declaración del conjunto:

```

type states is

(num 0,num 1,num 2,num 3,num 4,num 5,num 6,num 7,num 8,num 9);

```

En el siguiente código, las variables  $Q\_bus$  y  $D\_bus$  son señales definidas dentro del conjunto *states* donde la primera se inicializa en  $num\_0$  mientras que la segunda no se define en algún valor:

```

signal Q_bus : states := num_0;

signal D bus : states;

```

En las variables Q\_bus y D\_bus no se pueden guardar valores numéricos, *STD\_LOGIC*, o cadenas, solamente los valores los valores que se declararon en el conjunto: num\_0, num\_1, num\_2, num\_3, num\_4, num\_5, num\_6, num\_7, num\_8, y num\_9.

## 2.6 OPERADORES

En VHDL se pueden encontrar diversos operadores que realizan operaciones con los tipos de datos mencionados en la sección anterior.

## 2.6.1 OPERADORES ARITMÉTICOS CON NÚMEROS ENTEROS.

Estos operadores permiten realizar operaciones matemáticas con los números enteros cuyo resultado son números enteros. Para hacer uso de ellos, se tiene que haber declarado antes el paquete *numeric\_std*. En los siguientes ejemplos se muestra la forma en cómo se escriben los operadores matemáticos en VHDL y su resultado mostrado en el comentario.

#### Suma

Para este caso, la división solo puede regresar números enteros, por lo que, si matemáticamente el resultado es un número con punto flotante, el operador truncará el resultado.

#### Módulo

## 2.6.2 OPERADORES ARITMÉTICOS DE NÚMEROS CON PUNTO FLOTANTE

Funcionan de igual forma que los mencionados en el apartado anterior, con la diferencia que el resultado de estos operadores también es un número con punto flotante y pueden operar operaciones matemáticas complejas como las funciones trigonométricas, exponentes y logaritmos. Es importante mencionar que, si el número es entero, pero se quiere operar con números con punto flotante, se debe agregar el punto seguido de un cero (ej. Si es el numero entero 2, en números con punto flotante se escribe 2.0).

#### Suma

$$a \le 4.5 + 10.0; -- a = 14.5$$

#### Resta

#### Multiplicación

#### División

#### Exponente

#### Raíz cuadrada

$$f \le sqrt(0.56); -- f = 0.74833$$

#### Raíz cúbica

$$g \le cbrt(27.0); -- g = 3.0$$

#### Notación científica

#### Exponencial base e

$$i \le \exp(3.25); -- i = 25.79034$$

#### Logaritmo natural

$$j \le log(12.69) -- j = 2.5408$$

#### Logaritmo base 10

$$k \le log10 (156.4) -- k = 2.194237$$

#### Seno

$$1 \le \sin(2.36) - 1 = 0.041178$$

#### Coseno

$$m \le \cos(-2.36) - m = 0.9991518$$

#### **Tangente**

$$n \le \tan(0.423) -- n = 0.007383$$

#### Truncar

$$o \le trunc(15.7953) -- o = 15.0$$

#### Aproximar

$$p \le round(1.4896) -- p = 1.0$$

$q \le round(-3.713) -- q = 4.0$

## 2.6.3 OPERADORES LÓGICOS

## **Comparativos**

Realizan las comparaciones matemáticas conocidas, pueden tener argumentos tanto números enteros como números flotantes y el resultado es un booleano que puede ser true (verdadero) o false (falso). En la Tabla 2.2 se muestra el símbolo asignado a cada operador de comparación.

| A = B  | A igual a B         |

|--------|---------------------|

| A /= B | A diferente de B    |

| A < B  | A menor que B       |

| A > B  | A mayor que B       |

| A <= B | A menor o igual a B |

| A >= B | A mayor o igual a B |

Tabla 2.2 Operadores comparativos.

En el siguiente ejemplo se ilustra que la variable "condition" ha sido declarado variable booleana que solo guarda los valores ture o false.

condition

$$\leq$$

12  $<$  -4; -- false condition  $\leq$  0.1561  $>$ = 0 --true

En la primera línea se obtiene que la condición es falsa ya que 12 no es mayor a -4, mientras que en la segunda línea la condición es verdadera porque 0.1561 es mayor a cero.

## Lógicos

Los operadores lógicos son muy similares a los operadores comparativos del apartado anterior. Existe una diferencia entre ambos, los operadores comparativos trabajan con valores numéricos y devuelven un dato de tipo booleano, mientras que los operadores lógicos trabajan con el tipo de dato *STD\_LOGIC*. Por este motivo, los operadores lógicos se consideran equivalentes a las compuertas lógicas usadas en los circuitos digitales.

| not A    | Compuerta NOT  |

|----------|----------------|

| A and B  | Compuerta AND  |

| A or B   | Compuerta OR   |

| A xor B  | Compuerta XOR  |

| A nand B | Compuerta NAND |

| A nor B  | Compuerta NOR  |

| A xnor B | Compuerta XNOR |

Tabla 2.3 Compuertas lógicas en VHDL.

En la Tabla 2.3 se muestra a cada operador lógico en VHDL y su compuerta lógica equivalente. En el siguiente ejemplo la variable "C" se define como el resultado de una función booleana representada por compuertas lógicas.

```

C <= not ((A and B) xor (A or B)); Si\ A=1\ y\ B=0, \ se\ obtione\ que\ C=1.

```

# 2.7 ESTRUCTURAS LÓGICAS Y CICLOS

Las estructuras lógicas y los siclos que se presentan en esta sección funcionan de la misma manera que en otros lenguajes de programación. Permiten ejecutar bloques de código los cuales están sometidos a condiciones. En la Tabla 2.4 se muestran las estructuras lógicas y cíclicas sintetizables en VHDL.

Tabla 2.4 Estructuras lógicas y ciclos representados en VHDL.

| If / else                                                       | For                                                                           |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|

| <pre>if ([condition]) then   [code] else   [code] end if;</pre> | <pre>For [counter] in [min] to [max] loop   [Code for cycle]; end loop;</pre> |

```

If / elsif / else

While

if ([condition_1]) then

while ([condition]) loop

[Code for cycle];

[code];

elsif ([condition 2]) then

end loop;

[code];

elsif ([condition N]) then

[code];

else

[code];

end if;

Case

case ([variable/signal]) is

when ([case 1]) =>

[code for case 1];

when ([case 2]) =>

[code for case 1];

when ([case N]) =>

[code for case N];

when others =>

[code for a case that is not

in the previous cases];

end case;

```

Cada una de las estructuras lógicas presentadas en la Tabla 2.4 solamente funcionan si están contenidas dentro de una unidad secuencial *process* presentada en la sección 2.3.3. VHDL no puede sintetizarlas si no cumplen con este requerimiento y si se encuentran fuera de la unidad secuencial, habrá errores de compilación.

# CAPÍTULO 3 PROGRAMA QUARTUS II 13.0

Este capítulo es una breve introducción a Altera Quartus II el cual es un programa de diseño lógico. El software es capaz de trabajar con lenguajes de programación como VHDL y Verilog los cuales son usados para describir el funcionamiento de un circuito secuencial que será implementado en un FPGA o CPLD. En las siguientes secciones se explicará el proceso de instalación de la versión gratuita y la creación de proyectos.

# 3.1 INSTALACIÓN

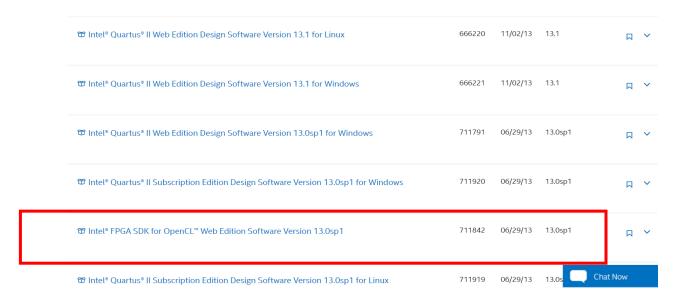

Para instalar este software se accede a la página de <u>FPGA Software Download Center (intel.com)</u> y en la lista que se muestra se busca "Intel Quartus II web edition Design Software Version 13.0sp1". La Figura 3.1 muestra una sección de la lista que la página de descargas, y entre todas las versiones se debe asegurar de descargar la versión web porque no requiere comprar licencia.

Figura 3.1 Centro de descargas de FPGA de Intel.

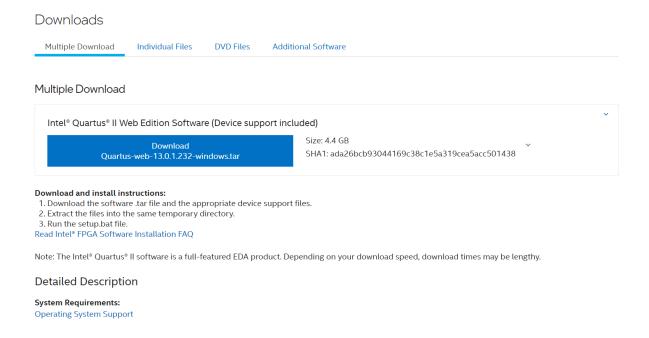

Al hacer clic en la opción mencionada en la lista, se dirigirá a una segunda página, donde existen cuatro opciones para descargar el software. Se selecciona la opción "Multiple Download" la cual contiene el software con lo requerido para este manual.

Figura 3.2 Enlace de descarga de Quartus II 13.0sp1

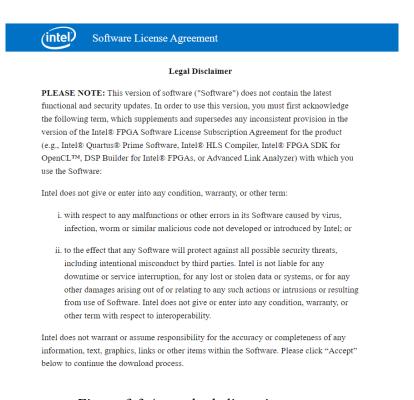

Por último, después de hacer clic en el botón de descarga, la página de Intel abrirá a una tercera página donde se debe aceptar un acuerdo de licencia, mostrado en la Figura 3.3, pero al ser una versión web no requiere de un registro. Al hacer clic en aceptar, la descarga comenzará y puede tardar unos cuantos minutos debido a su peso de 4.4 GB.

Figura 3.3 Acuerdo de licencia.

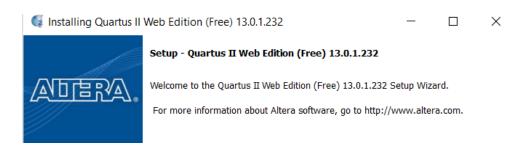

Una vez terminada la descarga, se debe descomprimir el archivo .*rar* y posteriormente ejecutar el instalador "QuartusSetupWeb-13.0.1.232.exe". La Figura 3.4 muestra la interfaz del instalador. Habrá que seguir los pasos para concluir la instalación del software

Figura 3.4 Sección de la ventana del instalador de Quartus II 13.0sp1.

# 3.2 CREACIÓN DE PROYECTOS

Cuando se haya terminado la instalación, el siguiente paso será ejecutar el programa haciendo clic en el acceso directo que se coloque en el escritorio con el logo de Quartus II.

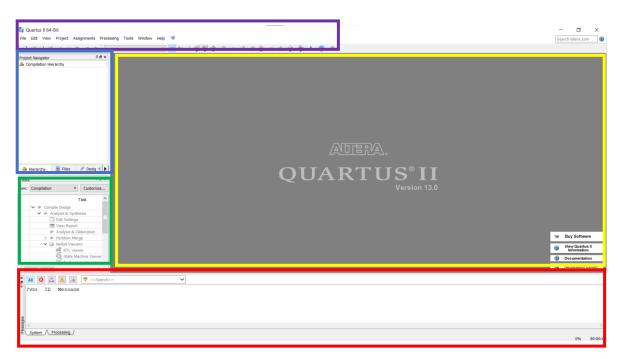

Figura 3.5 Página principal de Quartus II.

En la Figura 3.5 se aprecia la vista de la página principal del software sonde encontramos 5 secciones. En la barra de herramientas (morado) se encuentran las opciones de crear, guardar y abrir archivos. Navegador del proyecto (azul) se puede visualizar los archivos que conforman el proyecto y sus jerarquías. En el espacio de trabajo (amarillo) se situarán las pestañas que permiten escribir y editar los archivos del código fuente. En la lista de procesos (verde) se puede visualizar el estado en que se encuentra el proyecto referido a la compilación, en esta sección de la ventana es donde se muestra si el proyecto requiere ser compilado o si el proceso ya ha finalizado. Finalmente, la barra de mensajes (rojo) permite visualizar advertencias y errores que surjan durante la compilación del proyecto.

Las diferentes partes de la ventana del software resaltadas en la Figura 3.5 permitirán crear proyectos y, por lo tanto, generar código para programar un FPGA. Se recomienda seguir los siguientes pasos:

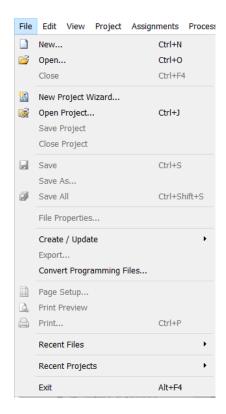

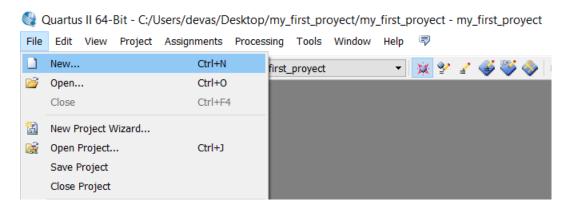

El primer paso será buscar la pestaña "File" en la barra de herramientas, que además se muestra en la Figura 3.6, después seleccionar busque la opción "New Proyect Wizard" y se abrirá una nueva ventana.

Figura 3.6 Barra de herramientas

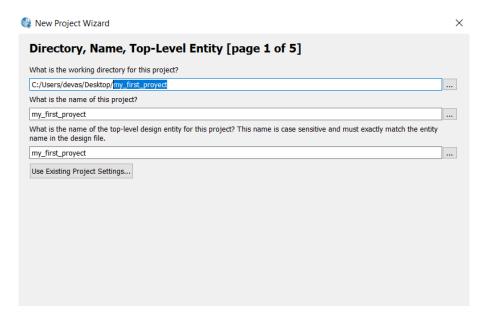

El segundo paso será crear una carpeta, ya sea en el escritorio o en cualquier parte de la computadora. Después se debe seleccionar dicha carpeta y posteriormente asignar un nombre al proyecto. Este proceso se hará en la ventana que muestra la Figura 3.7. Una buena práctica es que el proyecto y la carpeta tengan el mimo nombre.

Figura 3.7 Ventana de creación del proyecto.

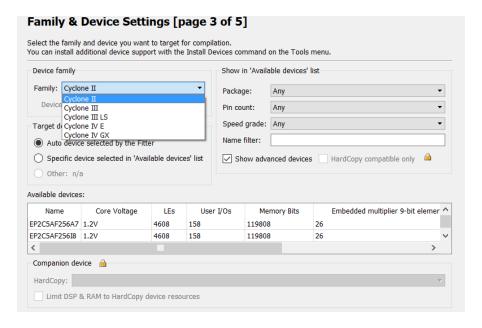

El tercer paso será seleccionar el FPGA para programar, la Figura 3.8 muestra la ventana con la lista de los FPGA Cyclone, este manual contempla solo la familia Cyclone II y Cyclone IV. En el apartado "Family" se puede seleccionar cualquiera de las dos familias antes mencionadas.

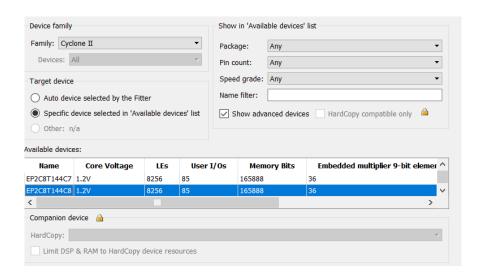

Figura 3.8 Selección de la familia del FPGA

En la lista inferior de la Figura 3.9, se muestran los modelos de cada familia de FPGA. En la lista inferior se selecciona el modelo del FPGA. Para este manual solo puede seleccionar la **EP2C5T144** (Cyclone II) o la **EP4CE6E22C8N** (Cyclone IV).

Figura 3.9 Selección del modelo de FPGA.

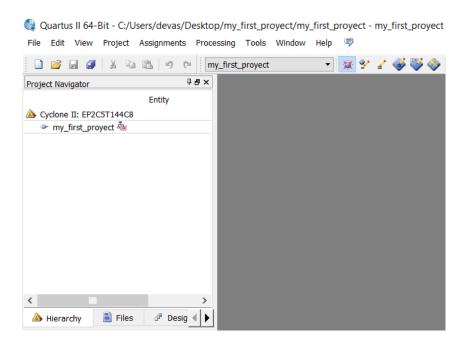

Se debe hacer clic en el botón "Next" hasta cerrar la ventana y finalmente pueda visualizar el botón "Finish" y por último hacer clic en él. Cuando termine el proceso se mostrará la ventana de la Figura 3.10.

| Summary [page 5 of 5]                                |                               |

|------------------------------------------------------|-------------------------------|

| When you click Finish, the project will be created v | vith the following settings:  |

| Project directory:                                   | C:/Users/devas/Desktop        |

| Project name:                                        | my_first_proyect              |

| Top-level design entity:                             | my_first_proyect              |

| Number of files added:                               | 0                             |

| Number of user libraries added:                      | 0                             |

| Device assignments:                                  |                               |

| Family name:                                         | Cyclone II                    |

| Device:                                              | EP2C8T144C8                   |

| EDA tools:                                           |                               |

| Design entry/synthesis:                              | <none> (<none>)</none></none> |

| Simulation:                                          | <none> (<none>)</none></none> |

| Timing analysis:                                     | 0                             |

| Operating conditions:                                |                               |

| Core voltage:                                        | 1.2V                          |

| Junction temperature range:                          | 0-85 °C                       |

|                                                      |                               |

Figura 3.10 Paso final de la creación del proyecto

Finalmente, se observará en el árbol de operaciones que el proyecto se ha creado, aunque en primera instancia se encontrará vacío, como se observa en la Figura 3.11. En la sección siguiente se mostrará el proceso de creación de los archivos que contienen el código para programar el FPGA.

Figura 3.11 Proyecto vacío.

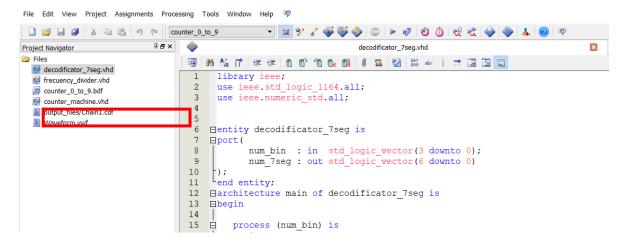

# 3.3 CREACIÓN DE ARCHIVOS VHDL

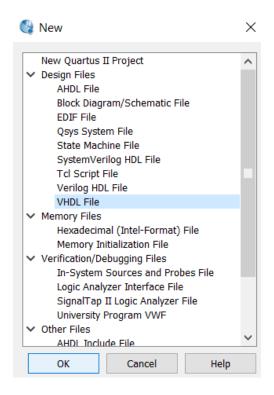

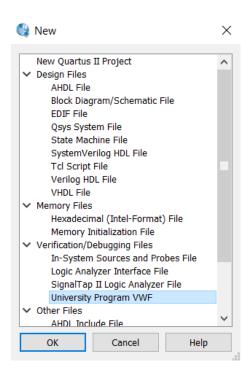

Ahora que el proyecto está creado, se procede a generar el archivo .vhd el cual permitirá escribir el código fuente en lenguaje VHDL. Este archivo debe tener el mismo nombre que el proyecto debido a que Quartus II rige a los archivos por jerarquías y requiere de un archivo principal que haga funcionar el proyecto, aunque puede crear tantos archivos .vhd como sean necesarios para simplificar el código que representen el circuito digital. Para generar el archivo, se debe buscar y seleccionar la opción "new" en la pestaña "File" como lo muestra la Figura 3.12.

Figura 3.12 Creación de un nuevo archivo en el proyecto.

Al hacer clic en la opción indicada se mostrará la ventana ilustrada en la Figura 3.13, se trata de una ventana emergente la cual contiene una lista de los tipos de archivos que puede crear en Quartus II, la opción que se requiere es "VHDL File".

Figura 3.13 Creación de archivos .vhd para programar en VHDL.

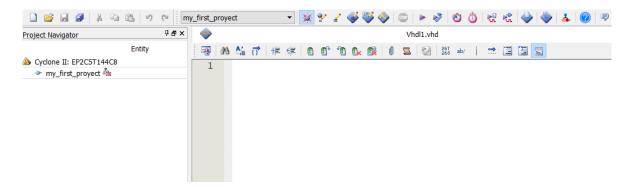

Una vez creado el archivo .*vhd*, la pantalla principal permitirá visualizar el contenido del archivo que obviamente se encuentra vacío tal como lo muestra la Figura 3.14.

Figura 3.14 Archivo .vhd vacío.

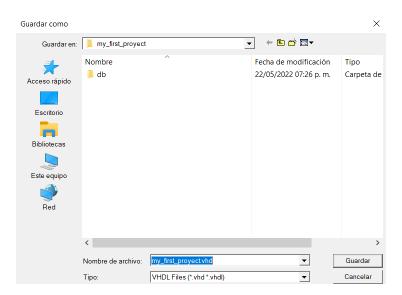

Después, se hace clic en la opción "guardar como", situada dentro de la pestaña "Files", y para guardar se tendrá que asignar él mismo nombre del proyecto al archivo. Por último, ee abrirá una ventana emergente, como lo muestra la Figura 3.15, donde se indica la dirección de la carpeta creada en la sección anterior. Finalmente se hace clic en la opción guardar.

Figura 3.15 Guardado del archivo.

## 3.4 DIAGRAMAS DE BLOQUES

El software de Quartus II tiene la opción de programar los FPGA mediante el uso de diagramas de bloques, donde cada bloque trae consigo una parte del código en VHDL del proyecto. Esta herramienta permite programar de una manera más sencilla, ya que el usuario puede tener un mejor control de la estructura del proyecto para programar el FPGA y las líneas de código utilizadas se reducen de manera significativa. Esta técnica es recomendable cuando se requiere utilizar más de un archivo .vhd

# 3.4.1 CREACIÓN DE PROYECTOS CON DIAGRAMA DE BLOQUES

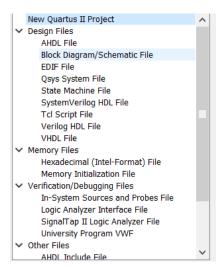

El primer paso para crear un proyecto usando los diagramas de bloques es crear el espacio de trabajo donde estarán alojados todos los bloques, conexiones, entradas y salidas. Para ello, se crea el proyecto siguiendo los pasos de la sección 3.2 y, una vez terminado, en la sección "Files" se busca la opción "New" y al abrirse la nueva ventana se selecciona Block Diagram / Schematic File como lo muestra la Figura 3.16.

Figura 3.16 Opción para crear un diagrama de bloques.

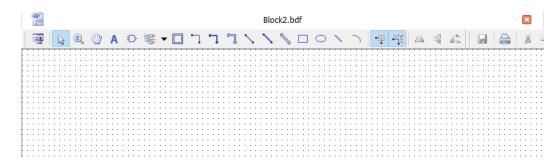

Se creará un archivo con terminación .*bsd* que el cual contiene el diagrama de bloques del proyecto, inicialmente no tendrá un nombre asignado por lo que aparecerá por defecto

como "block1.bdf". Regresando a la ventana principal, el archivo se visualizar como lo muestra la Figura 3.17 donde evidentemente estará vacío.

Figura 3.17 Archivo ".bdf" vacío.

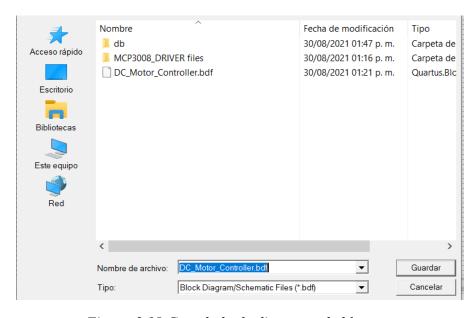

El segundo paso será asignar un nombre al archivo. De la misma manera que los archivos .vhd, en el software de Quartus II un archivo .bdf puede convertirse en la entidad principal del proyecto y en él se pueden añadir un sin número de bloques y código VHDL. Para ello, en la pestaña "File" se selecciona la opción "Save as" y por defecto se añadirá el nombre que fue asignado al proyecto. Automáticamente el archivo .bdf se guarda en la carpeta donde se aloja el proyecto como lo muestra la Figura 3.18 y finalmente se hace clic en el botón guardar.

Figura 3.18 Guardado de diagrama de bloques.

Una vez terminado este proceso, el espacio de trabajo estará listo para crear el diagrama de bloques que representará el funcionamiento del FPGA.

# 3.4.2 CREACIÓN DE BLOQUES USANDO CÓDIGO VHDL

En la sección anterior se creó un espacio de trabajo dentro de un archivo .bdf que contiene el diagrama de bloques que se usarán para programar el FPGA. Pero para armar dicho diagrama se debe crear cada uno de los bloques que lo compone. En Quartus II los archivos .bsf almacenan de manera gráfica los bloques que se usan para elaborar el diagrama y siempre están acompañados de un archivo .vhd que contiene el código que describe el funcionamiento del bloque así como sus entradas y salidas. Para crear un bloque basado en su código en VHDL se usa la siguiente serie de pasos:

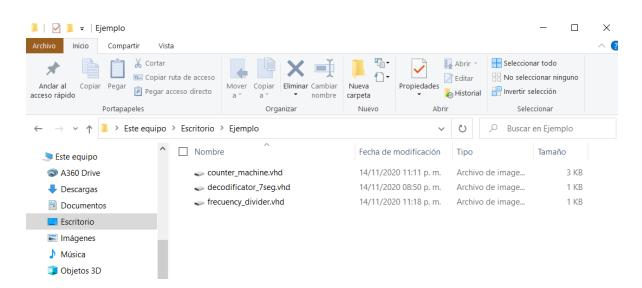

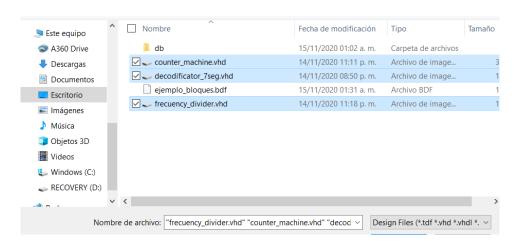

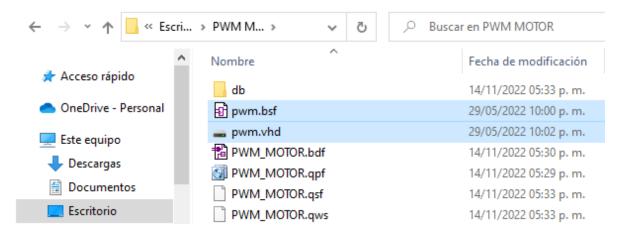

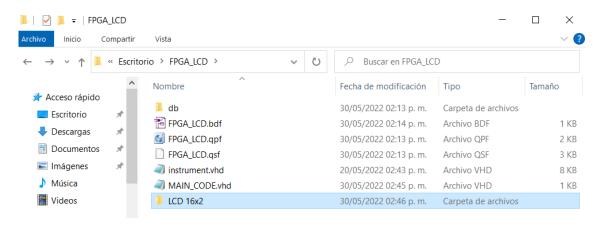

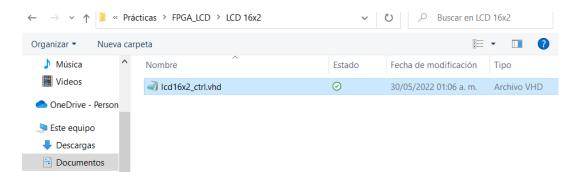

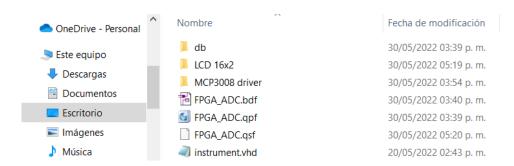

Ubicando la carpeta donde se alojar el proyecto, el primer paso será guardar los archivos .vhd que describen el funcionamiento de los diagramas de bloques. La Figura 3.19 muestra una carpeta llamada "Ejemplo" que contiene tres archivos VHDL donde cada uno generará un bloque distinto.

Figura 3.19 Archivos VHDL que serán convertidos a bloques.

El segundo paso es crear un proyecto configurado para diagrama de bloques como se explicó en la sección anterior.

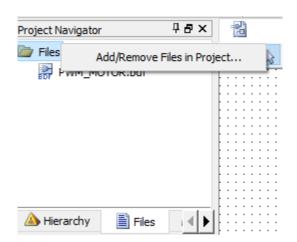

El tercer paso es incluir el archivo (o los archivos) .vhd que se encuentran dentro de la carpeta creada en paso anterior. Para incluirlos en el proyecto se debe hacer clic en la pestaña "Files" situada debajo del árbol de operaciones, y después en la parte superior del cuadro se hace clic derecho sobre "Files" y se selecciona la opción "Add/Remove files in proyect ..." tal como lo muestra la Figura 3.20.

Figura 3.20 Navegador del proyecto vacío.

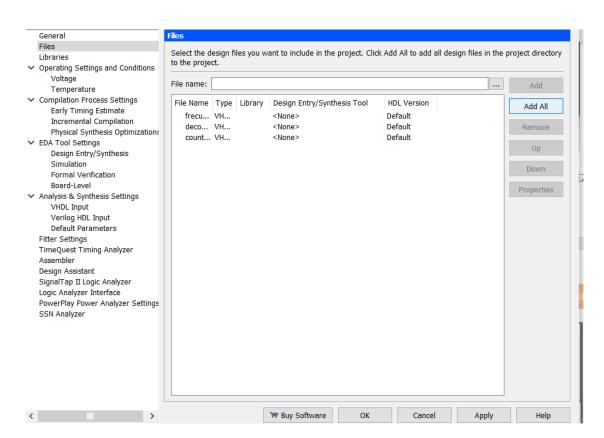

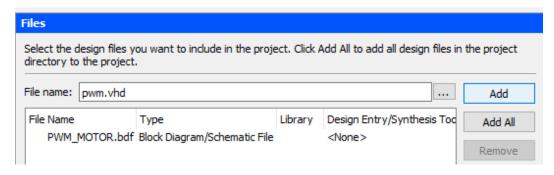

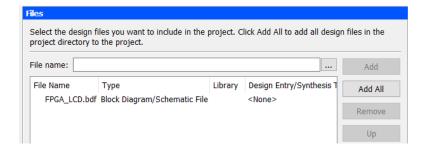

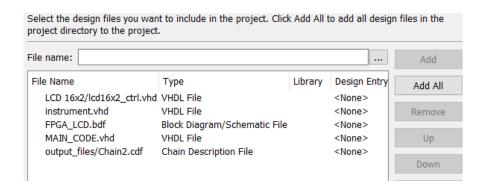

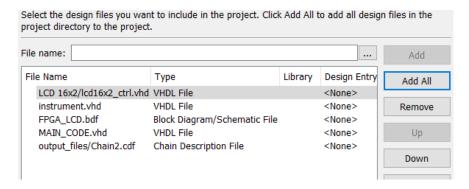

Después se desplegará una nueva ventana como lo ilustra la Figura 3.22 cuyo contenido principal es una lista que contiene los archivos incluidos en el proyecto. Al inicio la lista estará vacía ya que no existe ningún archivo que esté asociado al proyecto. Para que los archivos VHDL estén dentro del proyecto, se tendrá que hacer clic en el botón "..." ubicado arriba de la lista y se desplegará una ventana emergente como lo muestra la Figura 3.21 que muestra la carpeta donde se encuentra el proyecto y los archivos que se incluyeron al inicio de este proceso. Se selecciona todos los archivos .vhd y luego se hace clic en abrir.

Por último, cuando se haya cerrado la ventana de la Figura 3.21, en la lista de la Figura 3.22 se incluirán a los archivos en el proyecto. Finalmente, se debe hacer clic en "Add all", luego en "Apply" y por último en "Ok".

Figura 3.21 Selección de los archivos VHDL.

Figura 3.22 Selección de los archivos VHD

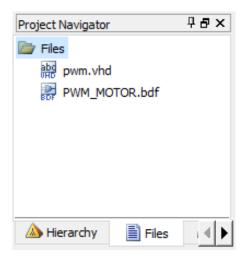

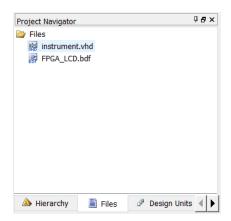

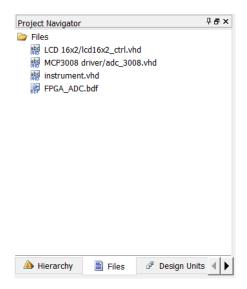

Ahora se podrá apreciar una lista donde se observa los archivos que conforman el proyecto, como se muestra en la Figura 3.23 que corresponde al navegador de archivos de Quartus II.

Figura 3.23 Navegador del proyecto con los archivos VHDL incluidos en el proyecto.

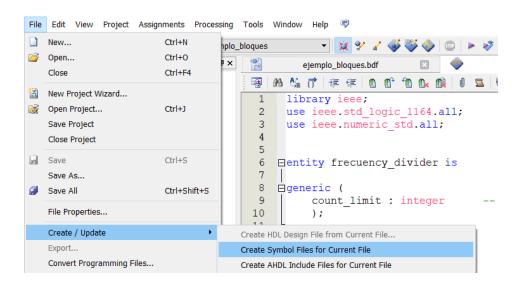

El cuarto paso será abrir uno de los archivos dentro del software y después seleccionar la pestaña "Files", después se hace clic en la sección "Create" y se selecciona la opción "Create Symbol Files for Current Files". Repetir el proceso para cada uno de los archivos.

Figura 3.24 Selección de la opción para crear archivos de bloques .bsf.

Cuando se hace clic en "Create Symbol Files for Current Files" se desplegará una ventana que informa cuando el archivo se ha creado exitosamente y la barra de mensajes del compilador mostrará mensajes de éxito, tal como se observa en la Figura 3.25. Si existe un error en los códigos de cada uno de los archivos se indicará con mensajes y se deberá corregir para que el archivo del diagrama de bloques pueda crearse. Se repite este paso para cada uno de los archivos .vhd.

```

| All | All

```

Figura 3.25 Barra de mensajes con compilación exitosa.

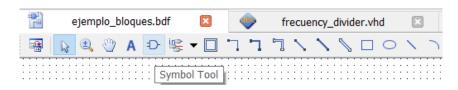

Para el quinto paso, una vez creado el diagrama de bloques para cada archivo y ubicando la barra de herramientas de la Figura 3.26, se selecciona la opción "Symbol Tool" situado en la barra superior de la ventana.

Figura 3.26 Selección de "Symbol Tool" para agregar bloques al proyecto.

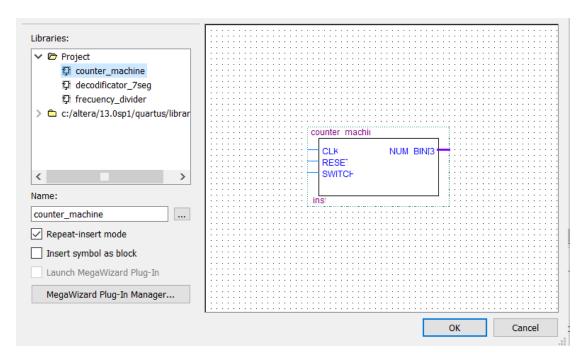

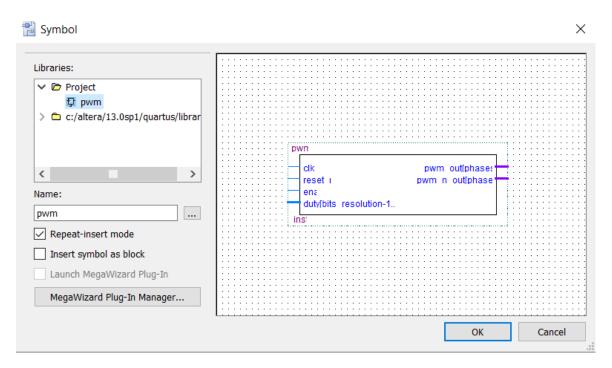

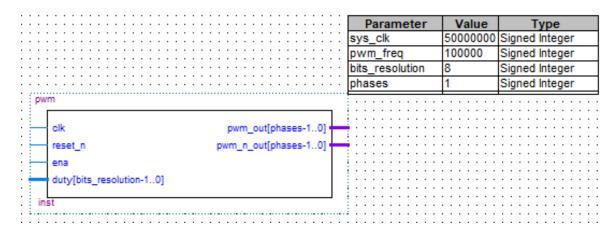

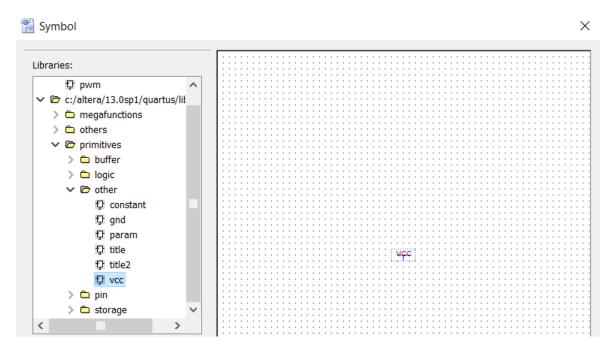

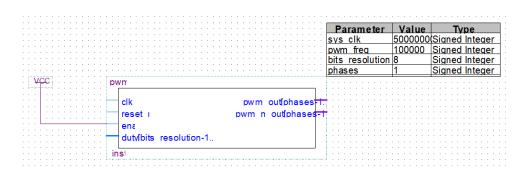

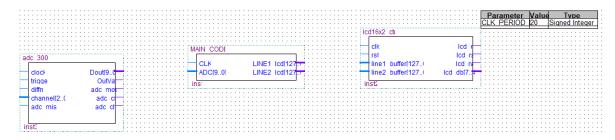

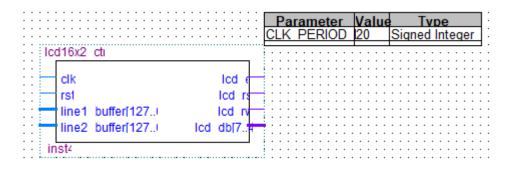

Se desplegará una ventana correspondiente a la carpeta "Proyect" mostrada en la Figura 3.27 y allí se sitúan enlistados cada uno de los diagramas de bloques que corresponden a los códigos de los archivos .*vhd* creados en los pasos anteriores. Se muestran también las entradas y las salidas de cada bloque que corresponden a las entradas y salidas del código escrito en ese archivo.

Figura 3.27 Vista previa de los bloques creados a partír de código VHDL.

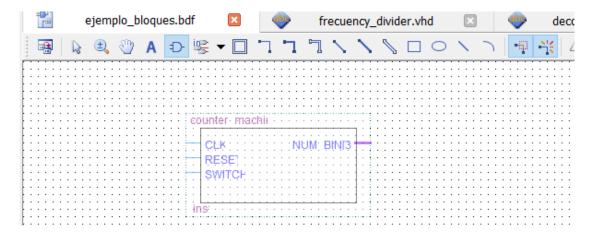

Al hacer clic en "Ok" el cursor aparecerá el bloque seleccionado y se podrá situar en cualquier parte de la ventana del diagrama de bloques. La Figura 3.28 muestra el bloque con una transparencia debido a que el cursor indica que ese bloque esta seleccionado, cuando se haga clic en cualquier parte del diagrama, el bloque pasará a tener un color sólido y significa que el bloque ya formará parte del diagrama.

Figura 3.28 Bloque creado a partír de código VHDL.

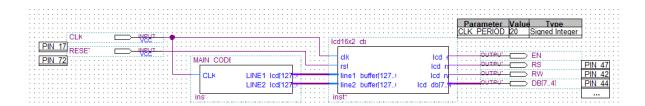

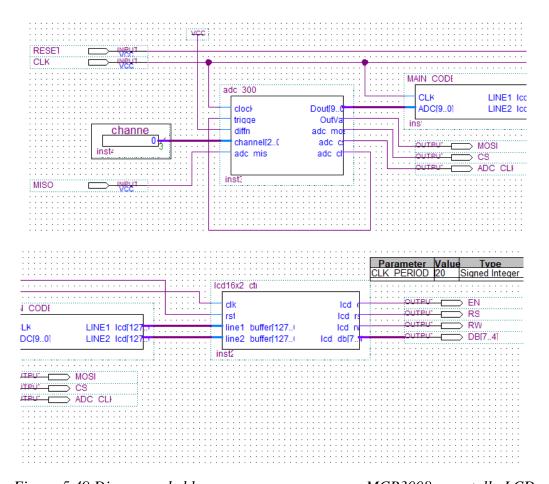

## 3.4.3 CONSTRUCCIÓN DEL DIAGRAMA DE BLOQUES

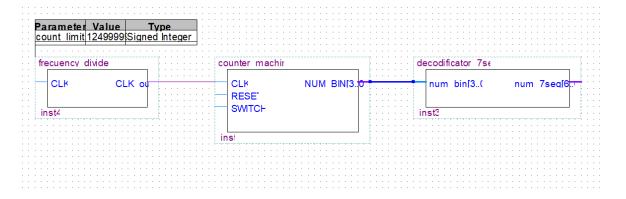

Existen dos tipos de uniones entre bloques los cuales corresponden con: la unión por señal digital simple representada por a un  $std\_logic$  en código VHDL; la unión por vector de bits, que es un conjunto de señales lógicas (ya sea de entrada o salida) del tipo de dato  $std\_logic\_vector$ . Ambos se distinguen principalmente porque la línea de la señal digital simple es más delgada y la unión del vector de bits tiene una línea más gruesa. En la Figura 3.29 se marcan resaltan las herramientas para unir los buses de datos entre los bloques del diagrama.

Figura 3.29 Opciones para unir los bloques. Para señales de solo bit (rojo) y vectores de bits (morado).

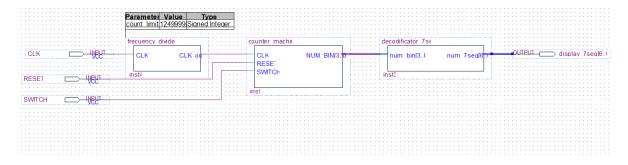

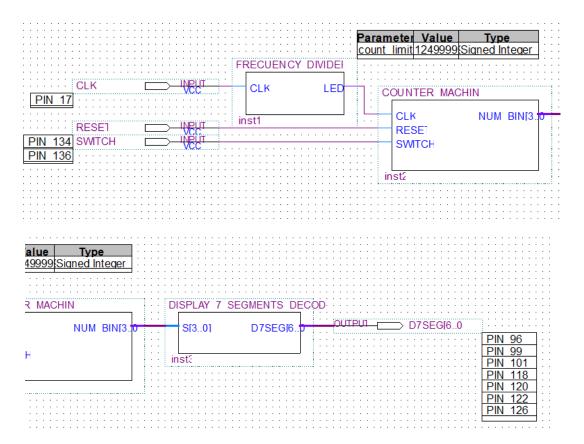

Con esta información, los bloques pueden interconectarse del proyecto, respetando que las señales simples se unen con otras señales simples y, de la misma manera, con los vectores de bits. En la Figura 3.30 ejemplifica la unión por un bit simple entre "frecuency\_divider" y "counter\_machine", mientras que la unión de éste último con "decodificator\_7seg" es un vector de 4 bits.

Figura 3.30 Unión de los buses de datos entra cada bloque.

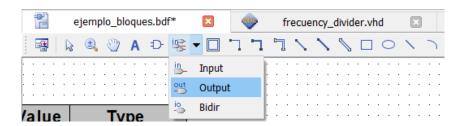

Al igual que en código VHDL, se deben asignar las entradas y las salidas que corresponden al proyecto en general.

Figura 3.31 Opción para añadir entradas y salidas al proyecto.

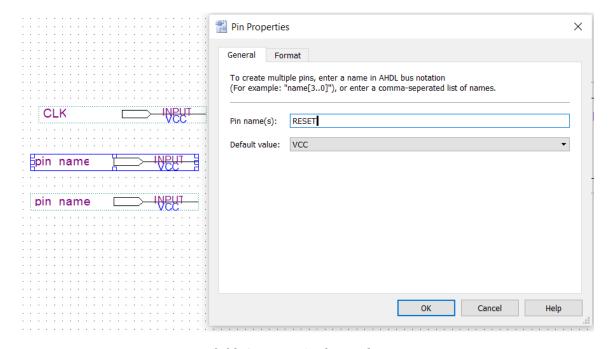

La opción "Pin Tool", mostrada en la Figura 3.31, permite al proyecto tener los pines de entrada y salidas necesarios y posteriormente asigne un nombre a cada uno de ellos. Para ello, se hace doble clic sobre el pin de entrada (o de salida) y se desplegará una ventana donde el siguiente paso será asignar un nombre a la entrada o salida tal como lo muestra la Figura 3.32.

Figura 3.32 Asignación de nombre a un pin.

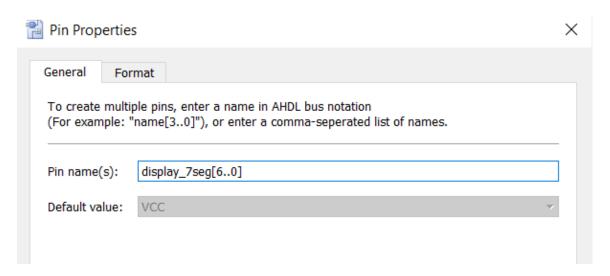

En el caso de que los pines correspondan a un arreglo de bits como se ha mencionado anteriormente se requerirá contemplar el número de elementos que contiene y escribir su nombre de la siguiente forma:

Siguiendo la estructura presentada anteriormente, en la ventana de la Figura 3.33 se escribe la estructura presentada para una salida de 7 bits.

Figura 3.33 Asignación de un nombre a una señal de 7 bits.

Posteriormente se unen los pines de entrada y salida con el resto de los bloques.

Figura 3.34 Creación y unión de los pines de entrada y salida al diagrama de bloque

De esta forma queda conformado el diagrama de bloques de todo el proyecto el cual puede compilarse sin ningún problema, y también asignar los pines físicos del FPGA a los pines de entrada y salida del diagrama.

Como se mencionó al inicio de esta sección, el objetivo de organizar el código con bloques e implementar un diagrama, es tener una mejor organización del proyecto y tener la menor cantidad de líneas de código en cada uno de los archivos .*vhd* que conforman el proyecto.

# 3.5 COMPILACIÓN DE PROYECTOS

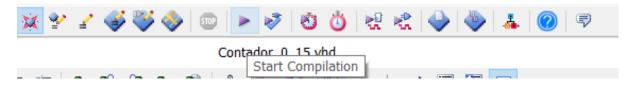

Sin importar que se trate de código VHDL o diagramas de bloques explicados en las secciones pasadas, el proceso para compilar el proyecto es el mimo. La compilación genera los archivos de programación de los FPGA y se revisan los errores en código o el proyecto. Para ejecutar esta función se ubica el botón "Start Compilation" en la barra de herramientas como lo muestra la Figura 3.35.

Figura 3.35 Selección de opción para compilar el proyecto.

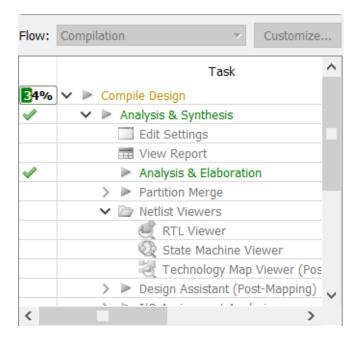

Cuando se inicie la compilación del proyecto se podrá observar el porcentaje de avance en la lista de procesos representada en la Figura 3.36.

Figura 3.36 Barra de procesos indicando el porcentaje de avance de la compilación.

Una vez que se haya completado, el software indicará si la compilación fue exitosa. De lo contrario, si existen errores en el código, se pueden ubicar los mensajes de error en la barra de mensajes. En los mensajes de error se indica el posible error ya sea de sintaxis, incompatibilidad de variables, señales usadas, pero no declaradas, etc. Además del posible error, también indica la línea de código donde está ubicado. En la Figura 3.37 se ejemplifica un programa que tiene errores de sintaxis en el código donde en las líneas 16, 22 y 31 hace falta escribir el ";" al final de la línea de código.

Figura 3.37 Barra de mensajes indicando errores en la compilación del proyecto.

# 3.6 CONFIGURACIÓN DE PINES DEL FPGA

La configuración de pines es un paso esencial para la programación de los FPGA debido a que se asocia un pin físico de este dispositivo a una variable de salida o entrada del código principal VHDL o del diagrama de bloques.

Para llevar a cabo la configuración de los pines, se selecciona la opción "Pin Planner" ubicado en la barra superior como lo muestra la Figura 3.38.

Figura 3.38 Selección de la opción "Pin planner" para configurar pines del FPGA.

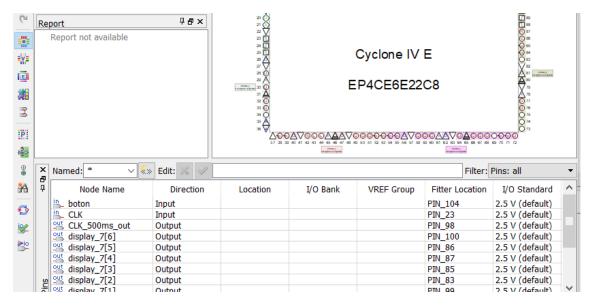

Se desplegará la siguiente ventana en la cual puede observar la configuración de pines del FPGA. En el anexo A adjunta la documentación con la distribución de los pines disponibles de ambas tarjetas de desarrollo.

Figura 3.39 Vista previa de la configuración de pines de la Cyclone IV (arriba) y lista de las entradas y salidas del proyecto (abajo).

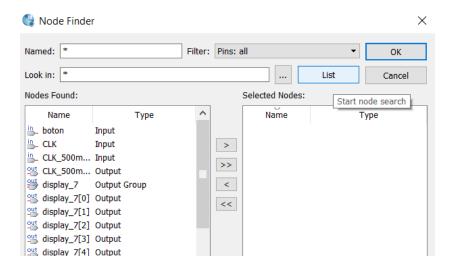

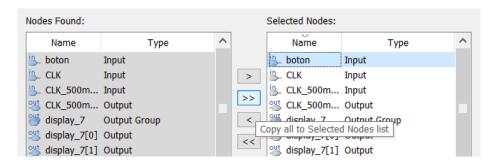

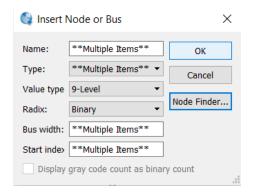

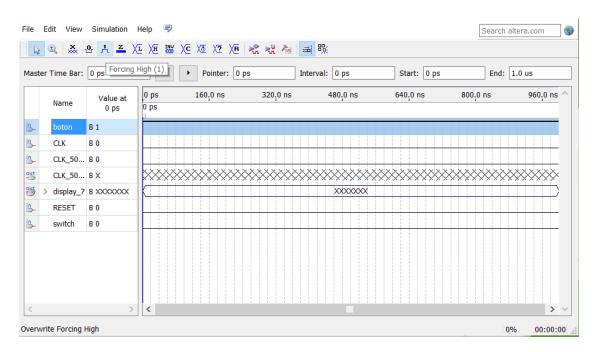

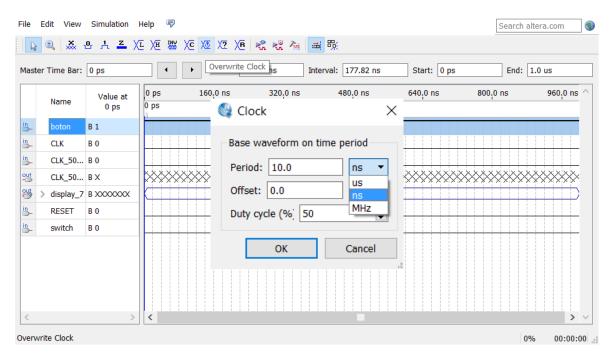

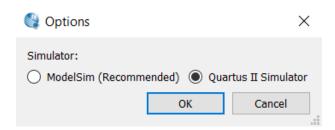

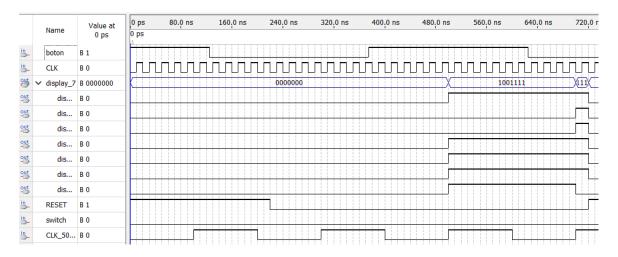

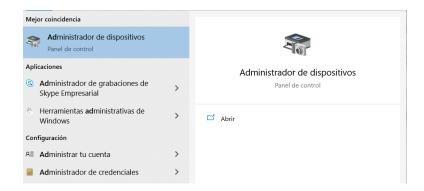

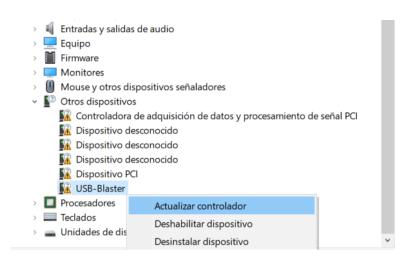

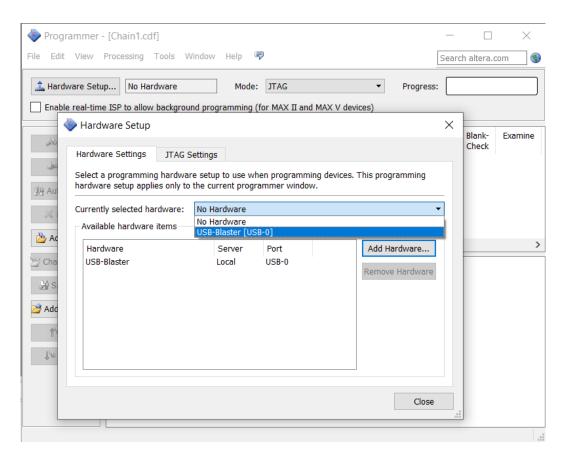

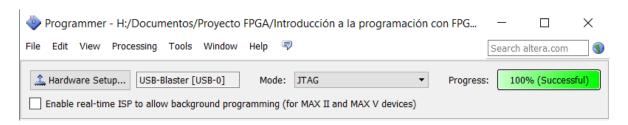

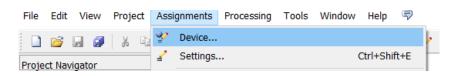

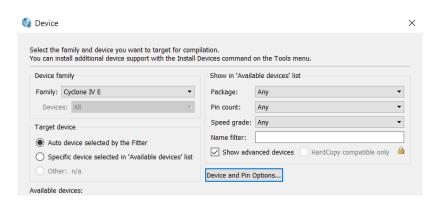

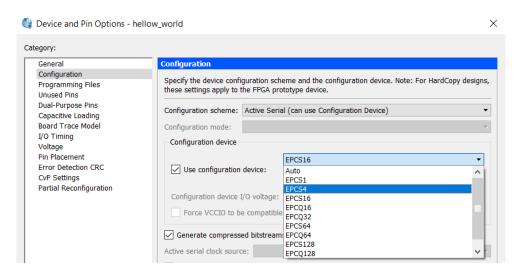

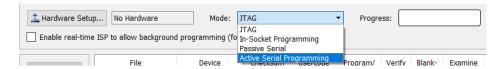

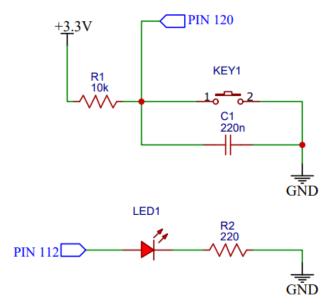

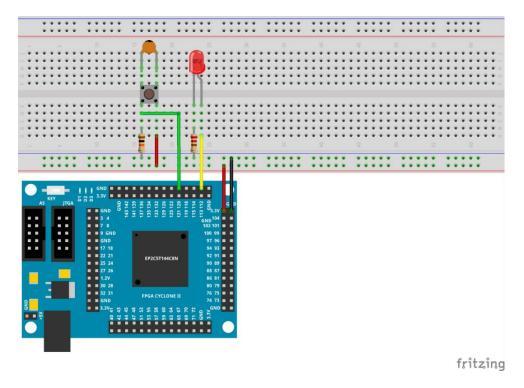

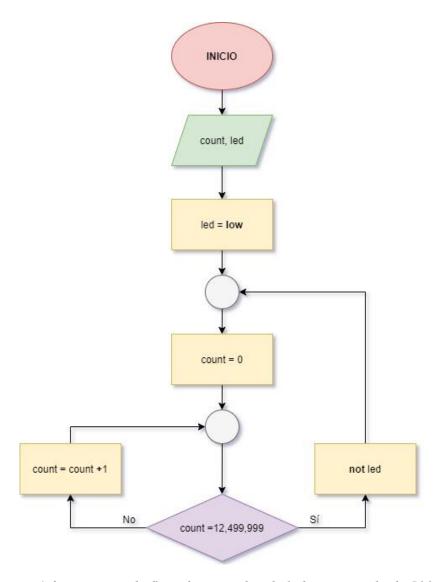

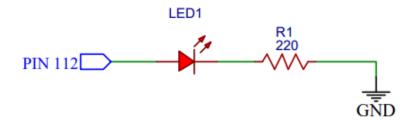

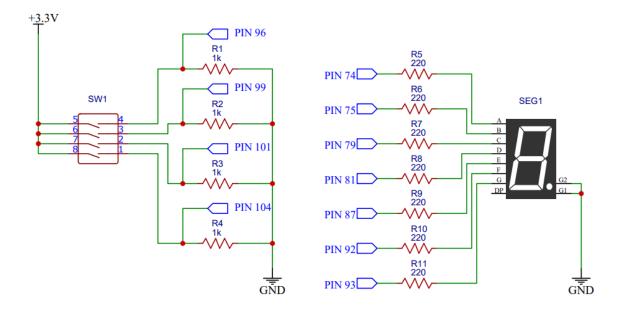

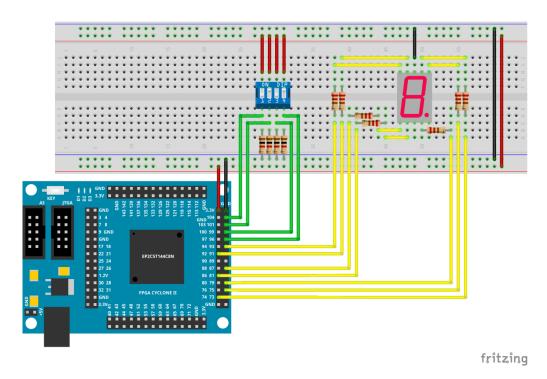

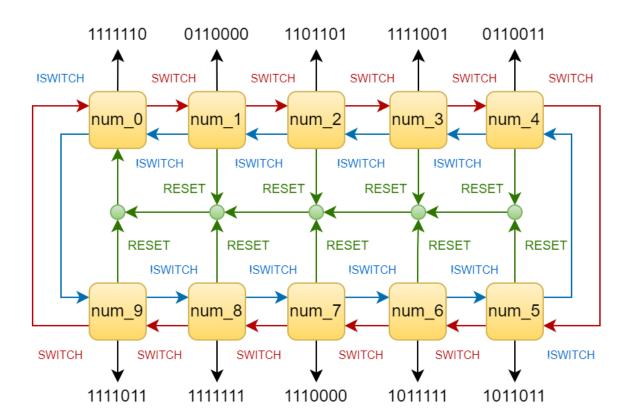

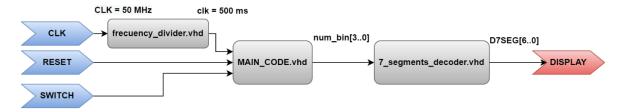

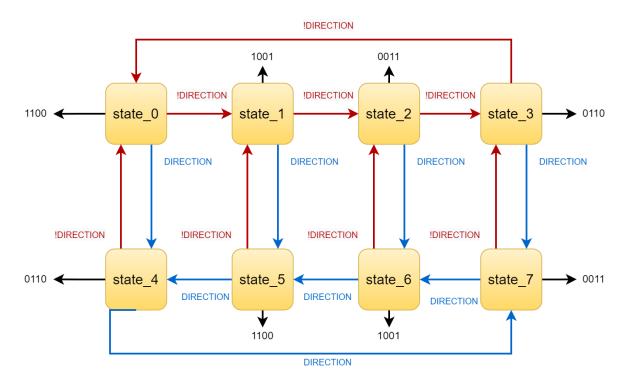

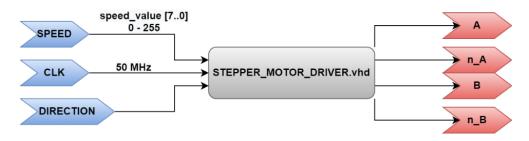

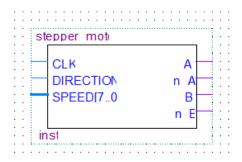

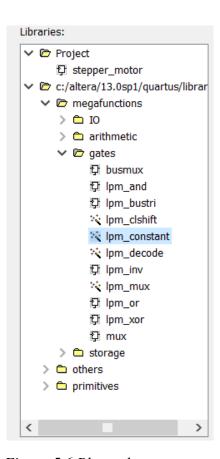

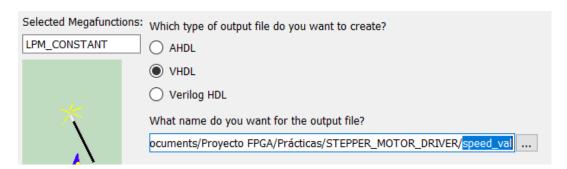

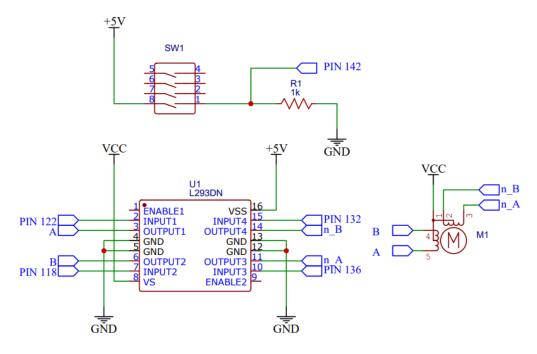

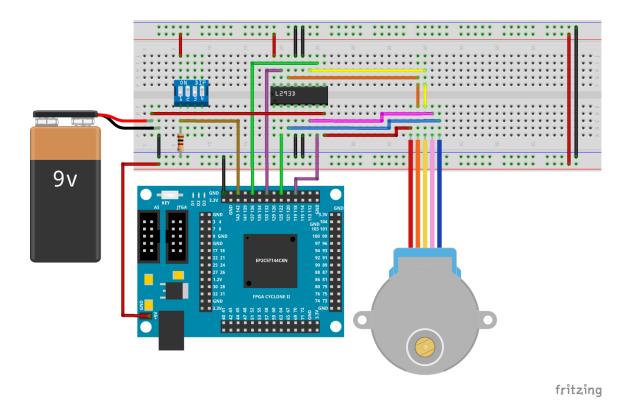

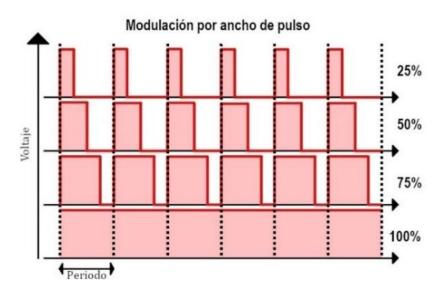

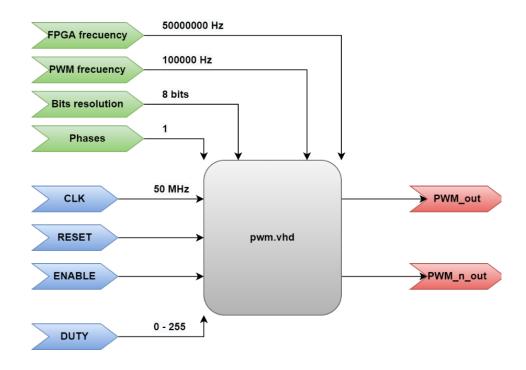

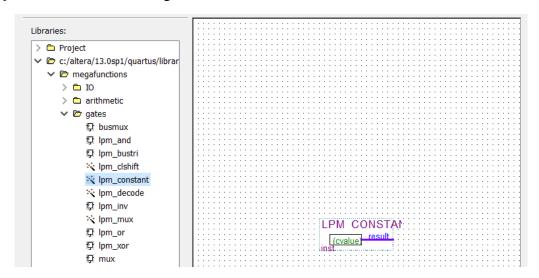

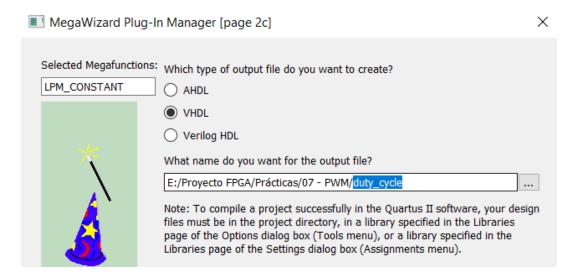

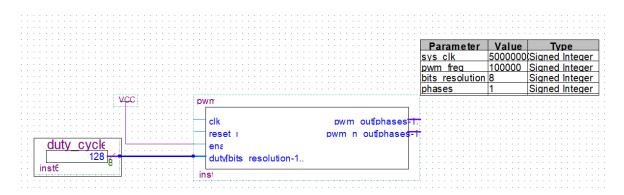

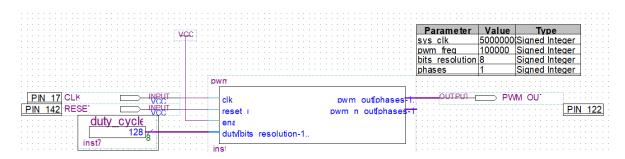

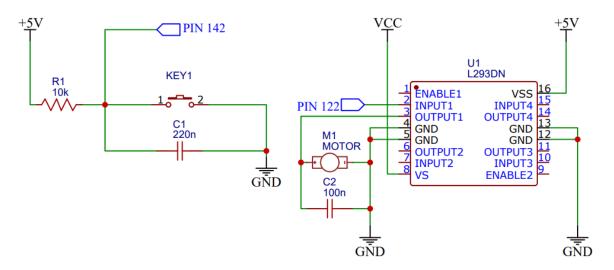

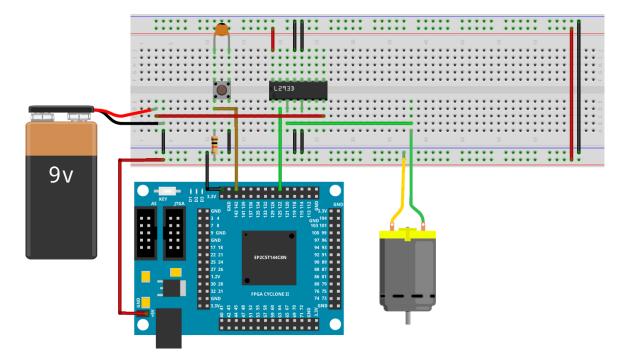

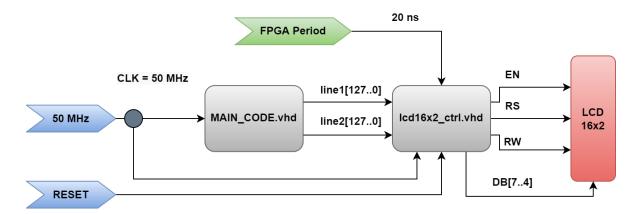

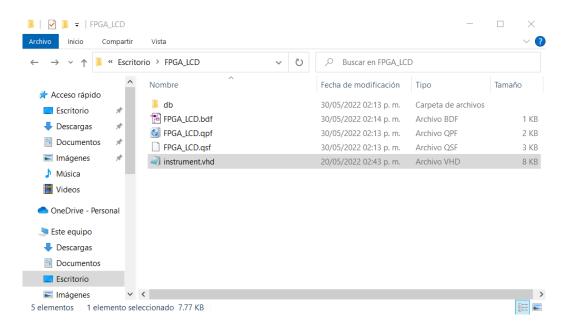

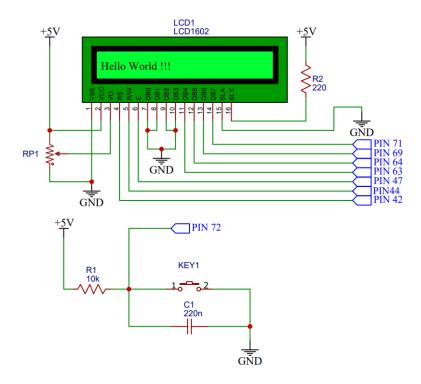

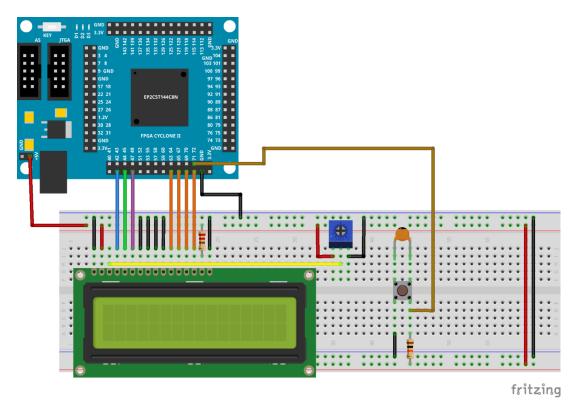

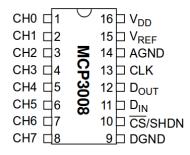

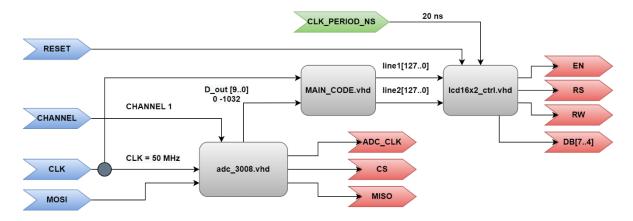

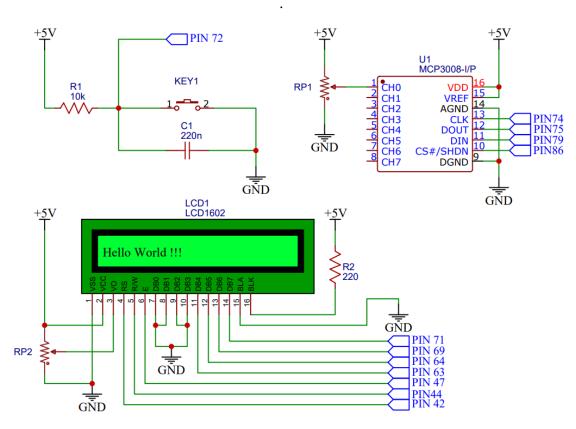

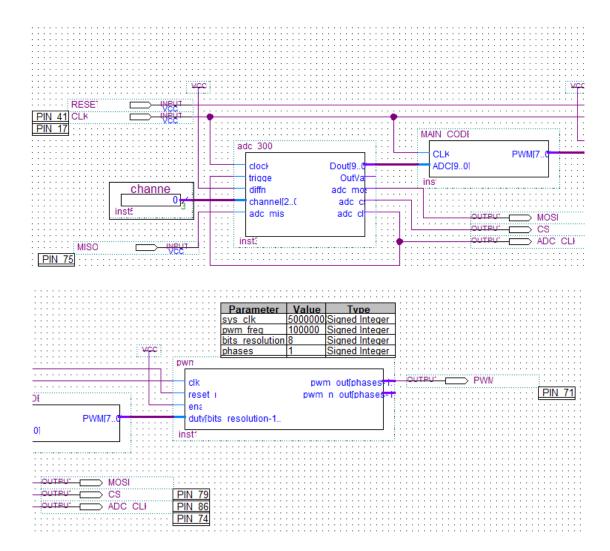

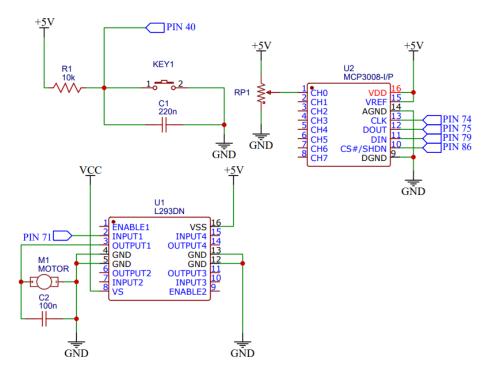

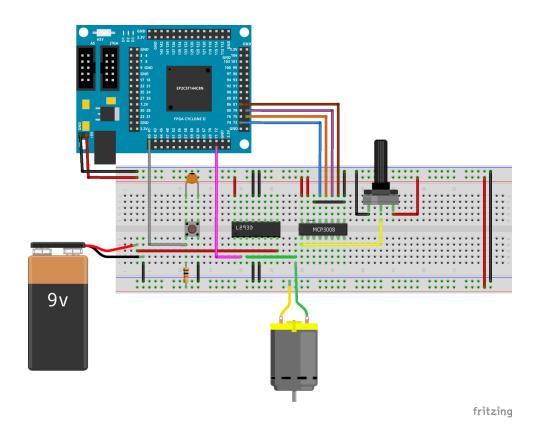

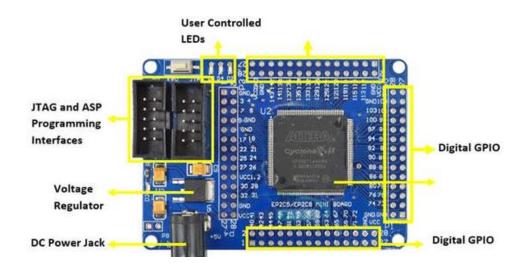

En Figura 3.39 muestra la organización de los pines físicos del FPGA Cyclone IV en la parte central de la imagen. Por otro lado, en la parte inferior de la ventana se encuentra una tabla que contiene cada una de las señales de entrada y salida son utilizadas en el código VHDL, o en el diagrama de bloques. Para asignar un pin a cada una de estas señales se debe dirigir el cursor en la columna "Location", como lo ejemplifica la Figura 3.40, y se escribe en cada una de las celdas el número de pin que va a corresponder a la señal de la fila de la tabla. El pin se escribe de la forma: **PIN\_(número del pin)** y se presiona la tecla *ENTER*.