#### "MICROPROCESADORES EN DISEÑO DIGITAL"

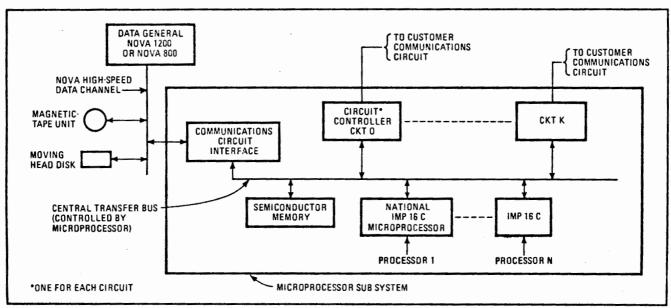

DR. PAUL M. RUSSO RCA Research Center Princeton, N.J.

#### Curso Corto; Sección de Ingenieria Electronica DESFI, UNAM

- · INTRODUCTION

- · BASIC PROCESSOR OPERATIONS

- I · DETAILED DESCRIPTION OF "COSMAC"

- III · COMPARISON WITH OTHER MEP'S

- I I/O STRUCTURES

- V · APPLICATIONS

- · HOME/ SCHOOL

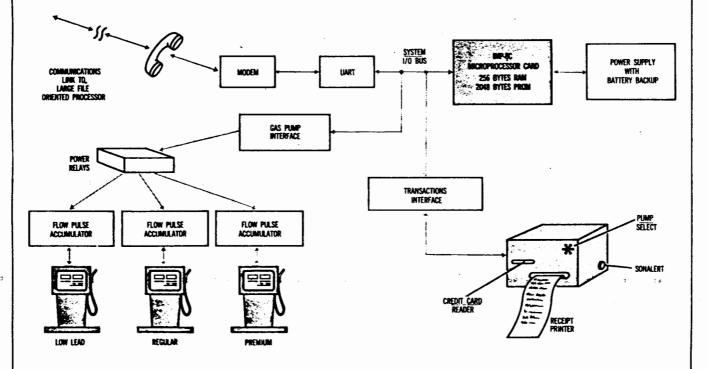

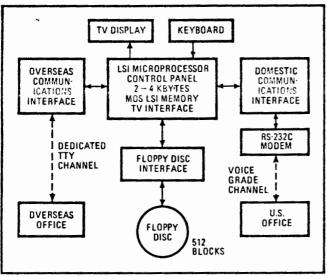

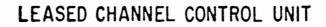

- · DATA COMMUNICATIONS

- · PROCESS CONTROL/ANTO MATION

VT

I

6(2)-

217

÷.

2173

· MULTI-MICROPROCESSORS

# INTRODUCTION É BASIC PROCESSOR

#### OPERATIONS

- · WHAT IS A RP

- · RP APPLICATIONS

- · HOW TO DESIGN WITH NOP

- . STATKS

I/O DEVICES

- TTY'S- cRT'S

- PRINTERS

- DISPLAYS

- DIS.CS

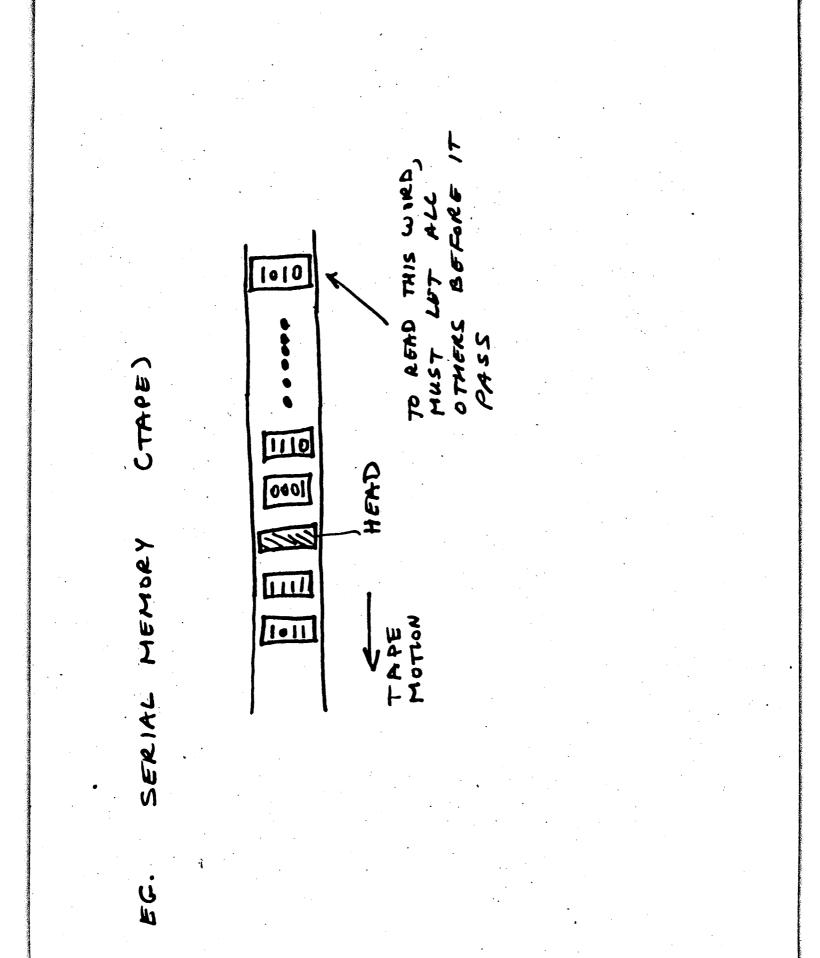

- MAGNETIC TTOPE

- SENSORS

- RELAYS

- ANALOG DEVICES

- A/D • D/A

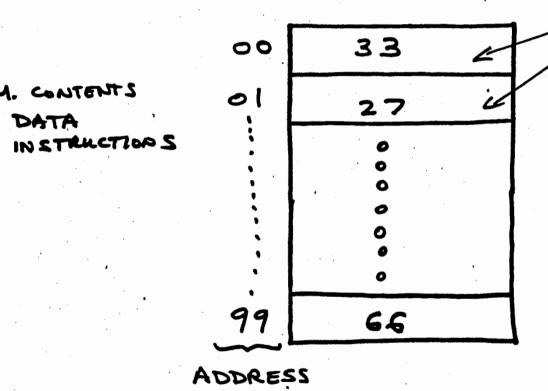

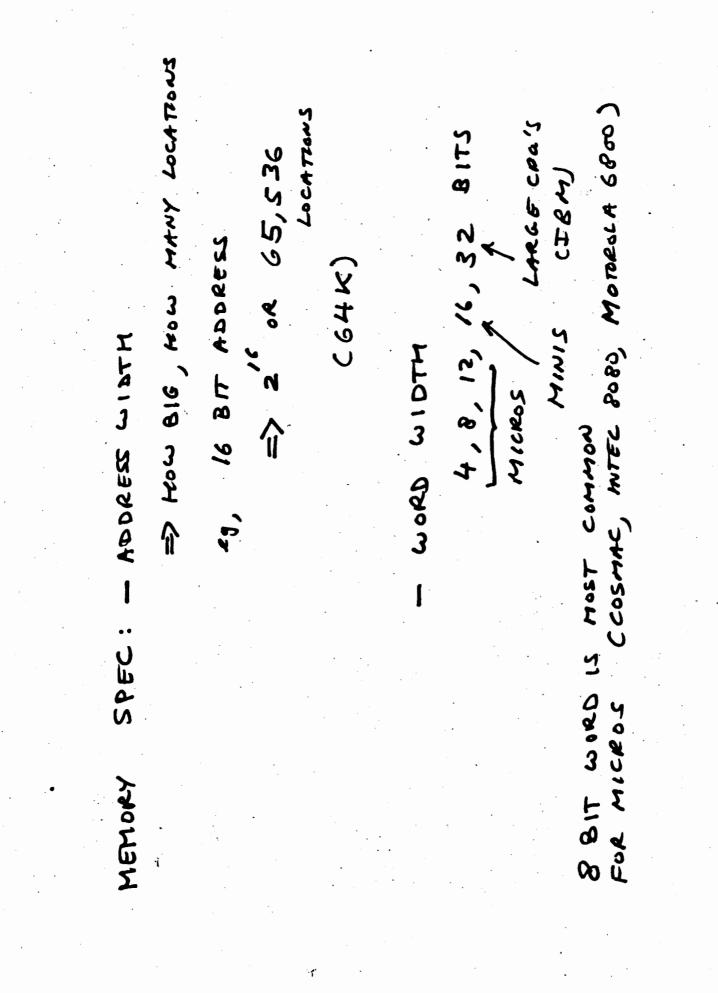

#### MEMORY : NEEDED BY ANY COMPUTER

· ADD RESS

MEM. CONTENTS

DATA

· INFORMATION AT ADDRESS

. THINK OF POST OFFICE

CONTENTS

CAN PUT NEW DATA IN OR TAKE OLD DATA OUT.

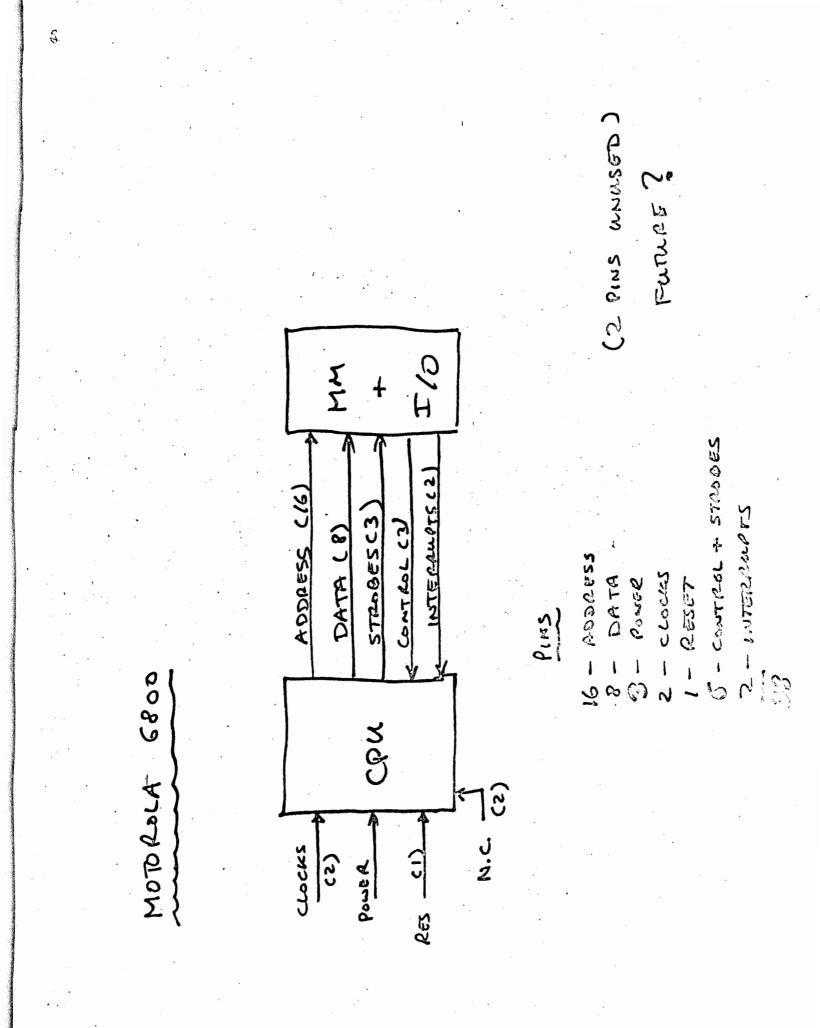

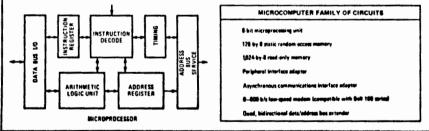

### MICROPROCESSOR: CPU ON 1 CHIP

TECHNOLOGY LIMITS: CHIP AREA -> LIMITS FUNCTIONS

> PACKAGE -> LIMITS # PINS

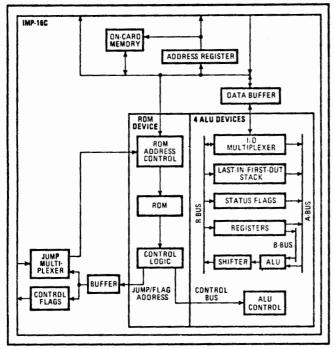

MULTI CHIA SETS (EG, BIPOLAR SLICES OR LSI-11 TYPE SETS)

ARE NOT TRUE MICROPROCESSORS. THEY ARE MINICOMPUTER BUILDING BLOCKS.

EVERY COMPUTER : - FETCH INST. FROM MM EXECUTE INST. MACHINES -FETCH NEXT INST. FROM MM EXECUTE IT COSMAC: 2 MACHINE CYCLES PER INST. A "PROGRAM" DETERMINES SEQUENCE OF INSTRUCTION TO BE EXECUTED.

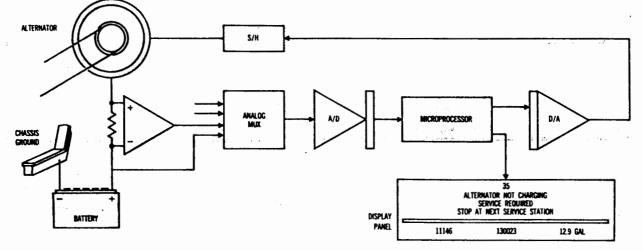

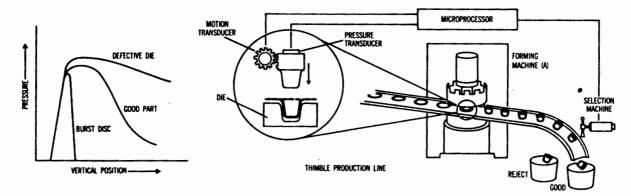

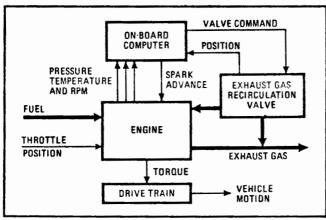

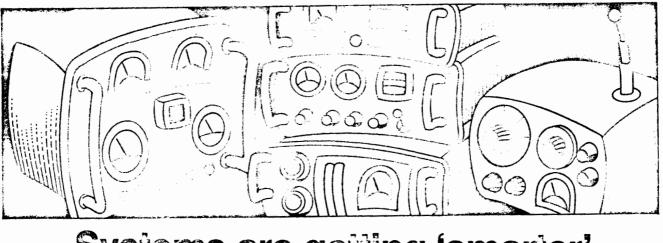

EXAMPLE OF MICROCOMPUTER : DISPLAYS, ACTUATORS CAR SYSTEM : FUEL FLOW **F10** CPU ROM DISTRIBUTOR OPTIMAL FUEL MIXTURE GET : - MPG (Km ken Litre) STATUS - Speed - ALARMS ETC

- REPLACE MINIS (50,000/YEAR)

- REPLACE MARD WIRED LOGIC TERMINALS

CCONTROLLERS) INSTRUMENTS

AROCESS CONTROL

- NEW PRODUCTS CARS - HOME

- SCHOOL - ETC.

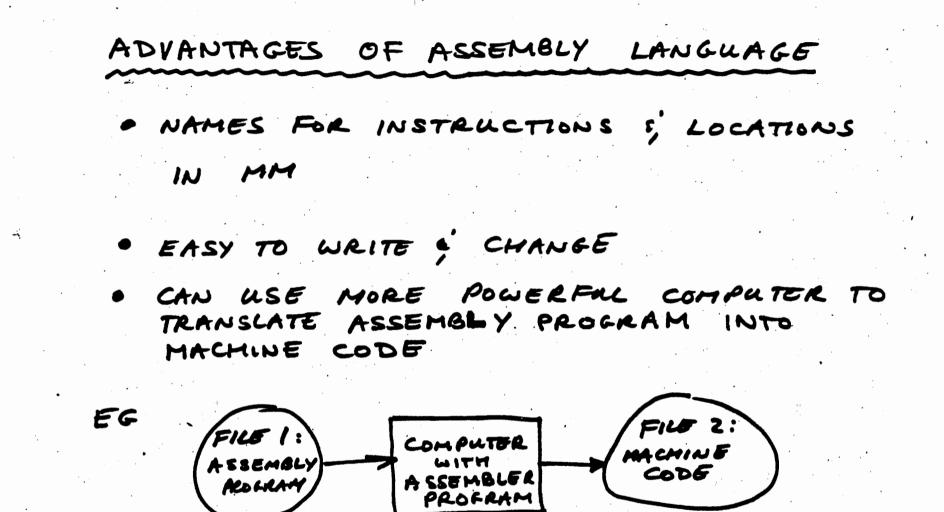

## ADVANTAGES OF USING MP

· COST

• FLEXIBILITY - CUSTOMIZE IN SOFTWARE - NEW FUNCTIONS

· MAINTENANCE

· RELIABILITY

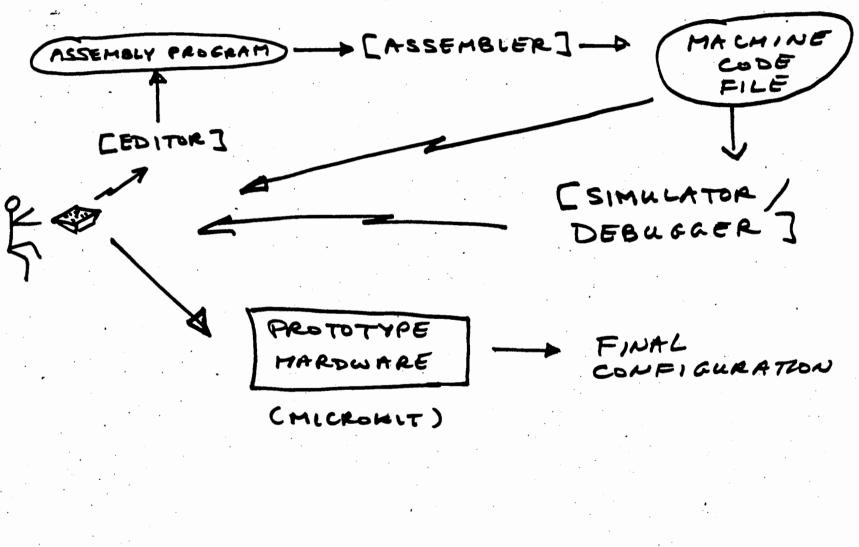

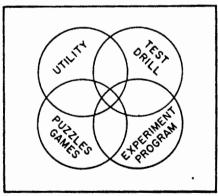

# AIDS TO PP SYSTEM DESIGN

- · LEARNING AIDS \_ MICROTUTOR

- DEVELOPMENT AIDS MICROKIT

INTELLEC

(work with terminal)

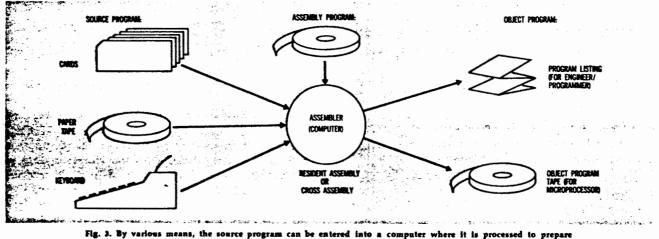

- · CROSS-ASSEMBLERS

- · SIMULATORS

- DEBUGGERS

AID PROGRAM DEVELOPMENT

## TOTAL SYSTEM DESIGN

0, 1, 4 23 BINARY 2' 2°,  $0 | | 0 = (22)_{10}$ EG. 16×1+8×0+4×1+2×1+1×0 BASE = 2  $= (22)_{10}$ 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, HEXADECIMAL D, E, FA = 10D = 13BASE = 16E=14 B = 11F=15 C = 12

172 27188 þ 00 || 00 V || 00 V || 00 11 BYTE BYTE = (243) l 1/ 4 (E3), 15×16+3× DIGITS HEX SI 5 N ŕ

T D-NM+NON00CAUAWL

DECIMAI

0-NW+NOL0000-4W+N

BINARY

NOTATION IS HUMAN CONVENCE IN TERNALLY COMPUTERS USE BINARY HEX

|  | RAM RANDOM ACCESS MEMORY | · USUALLY MEANS READ/WRITE MEMORY | ROM READ ONLY MEMORY | ALSO RANDOM ACCESS | · CANNOT WRITE TO IT |  | WHAT DOES RANDOM ACCESS MEAN? | · CAN ACCESS ANY WORD WITH | SAME SPEED |  |  |

|--|--------------------------|-----------------------------------|----------------------|--------------------|----------------------|--|-------------------------------|----------------------------|------------|--|--|

|--|--------------------------|-----------------------------------|----------------------|--------------------|----------------------|--|-------------------------------|----------------------------|------------|--|--|

OI => DATAS PATA VI PATA V ADDRESS IN PARALLEL 100 DATA 4 DATA J DATA S DATA 6 DATA 3 DATA 2 0 DATA DATA :0: ADDRESS 42 61 6 .... \$ 0 \$ ; 0; : . ò 2 ;0; \* `\* , o FOR RAM DECODE 0 3 BIT ADDRESS

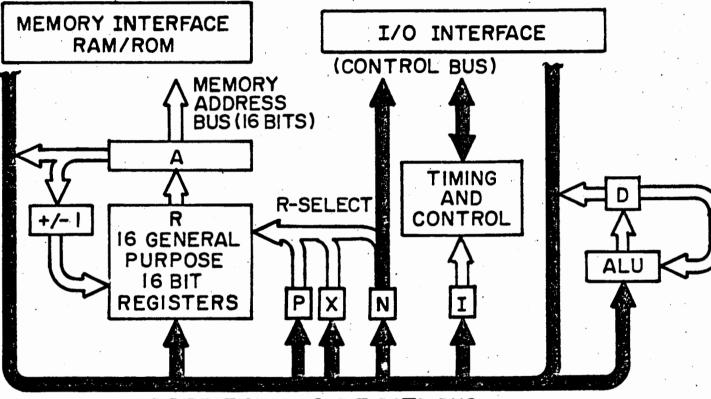

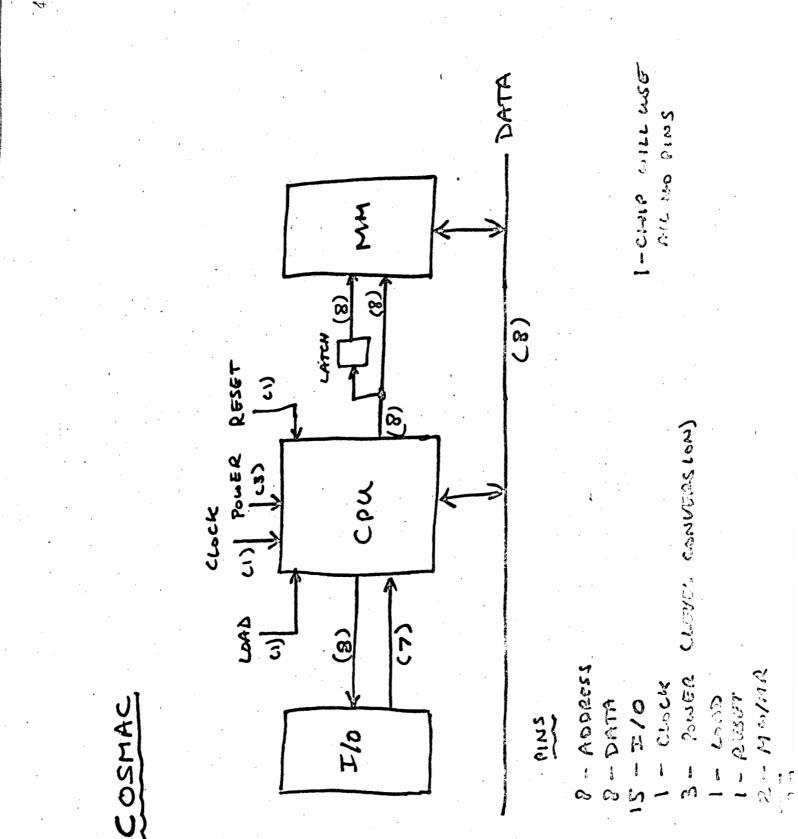

COSMAC

4205 8 BIT "WORD SIZE" BYTE ( 2 t t ) INSTRUCTION IS ADDRESS ING DATA BUS EVERY 16 BIT 8 8 7

していい 150 and Execute NEEDS IN STRUCTON FETCH CYCLES 日午の日

CCOMPACT CODE)

JIID ONE BE Bat wir CHIPS Sool ป

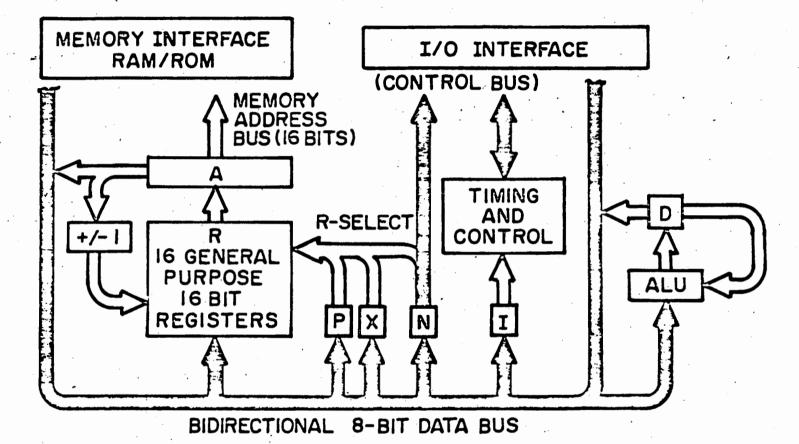

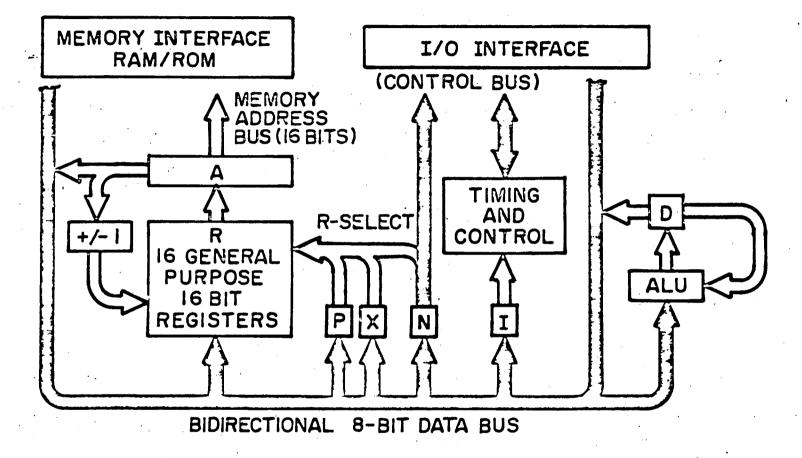

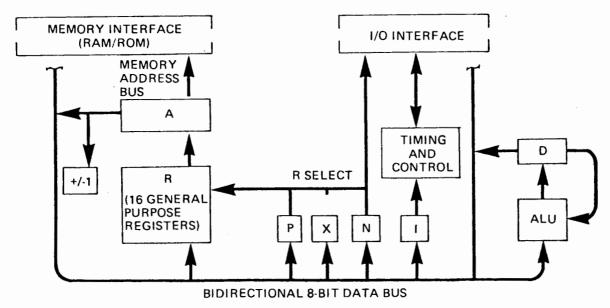

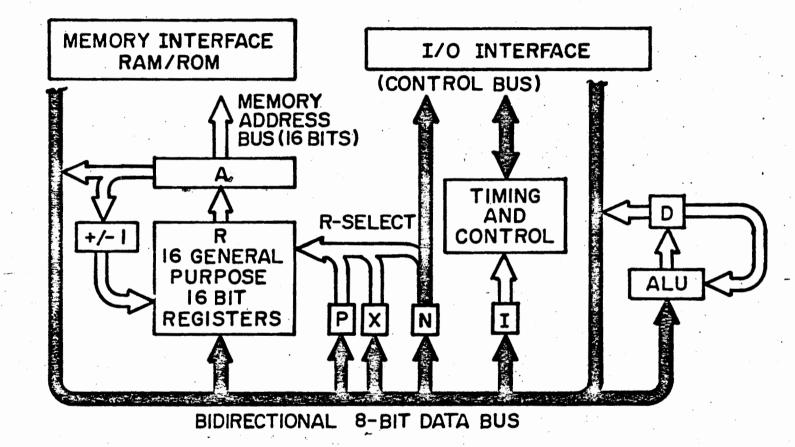

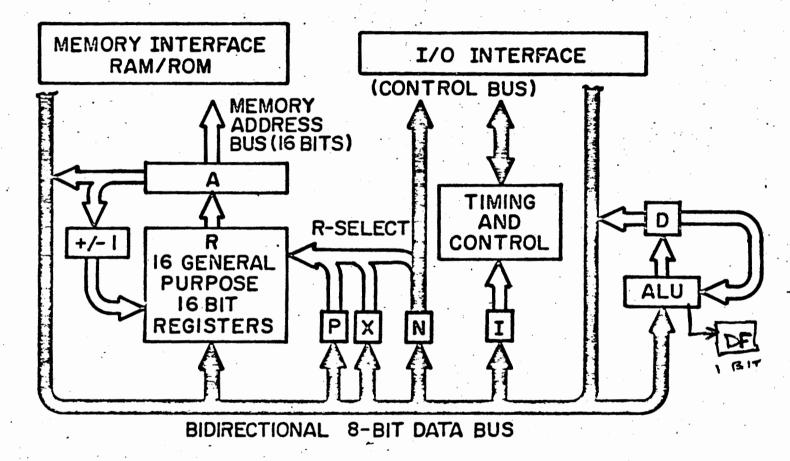

BIDIRECTIONAL 8-BIT DATA BUS

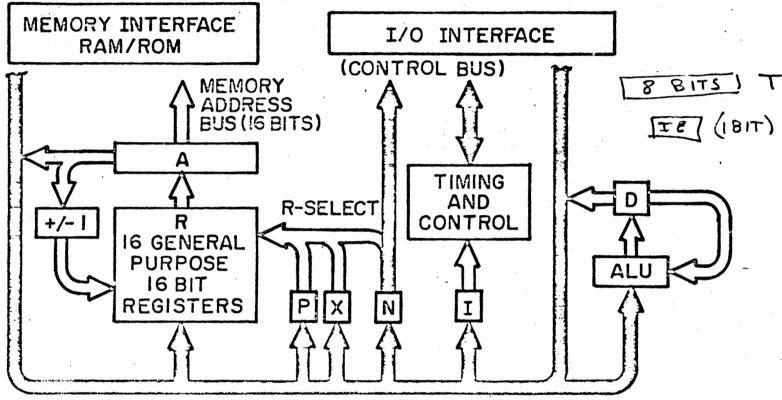

COSMAC MICROPROCESSOR ARCHITECTURE

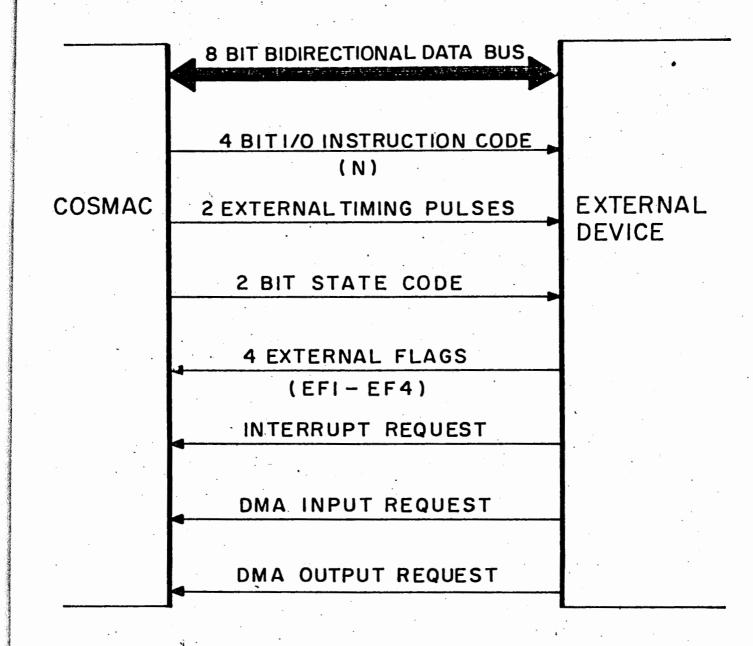

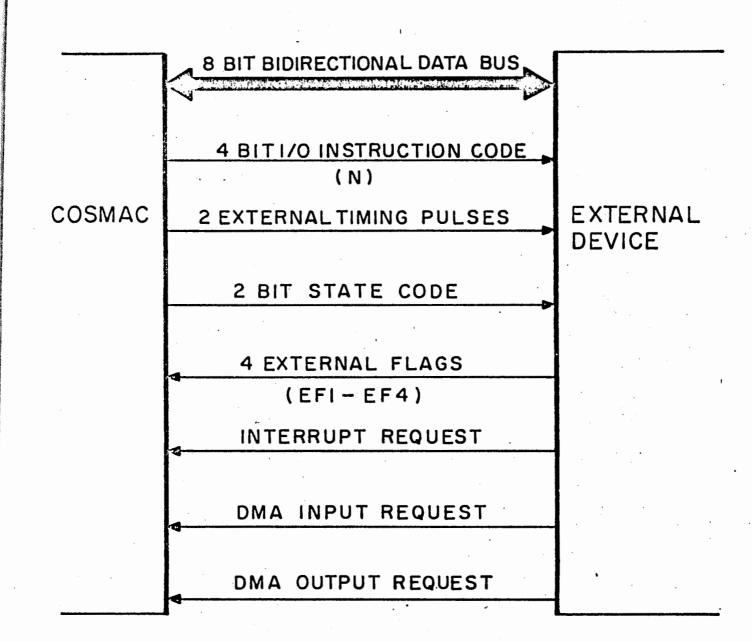

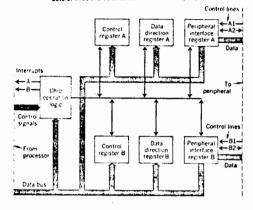

#### COSMAC 1/O INTERFACE

#### COSMAC ARCHITECTURAL ADVANTAGES

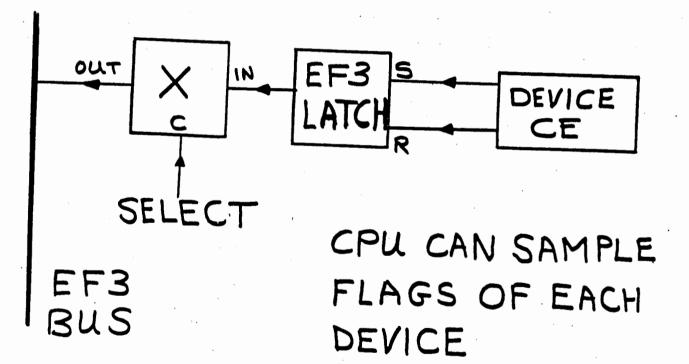

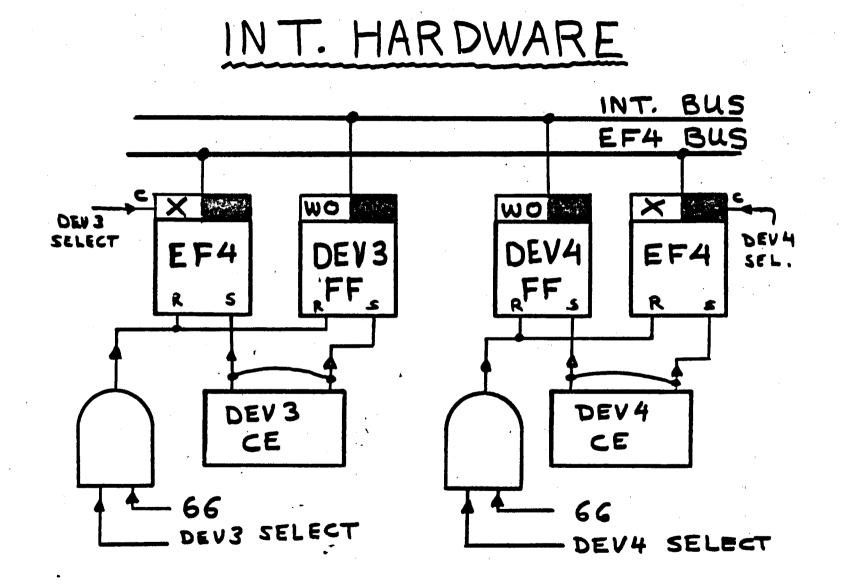

★ EXTERNAL CPU TESTABLE FLAGS

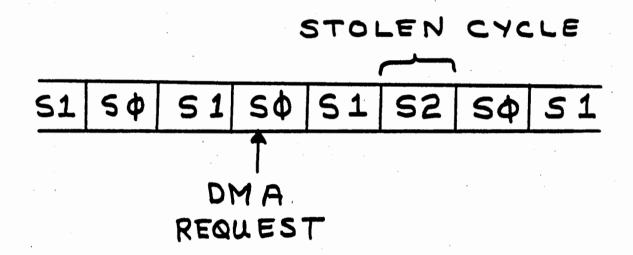

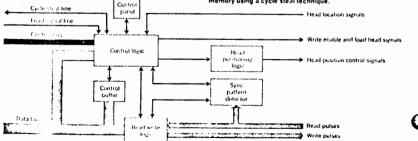

★ BUILT-IN DMA CHANNEL

★ SINGLE-PHASE CLOCK

★ CMOS TECHNOLOGY

÷

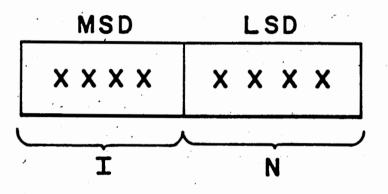

#### ONE BYTE INSTRUCTION FORMAT

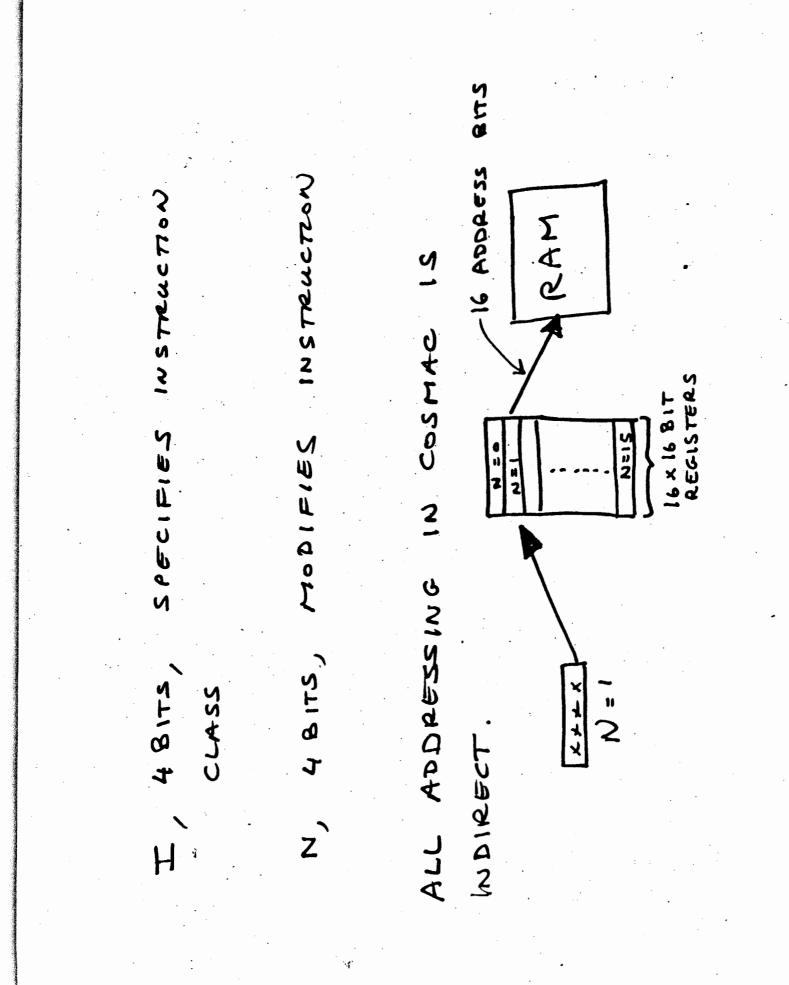

COSMAC MICROPROCESSOR ARCHITECTURE

# P, 4 BITS, SELECTS PROGRAM COUNTER (PC)

X, 4 BITS, SELECTS DATA POINTER

-**X**

PC ALWAYS POINTS AT NEXT INSTRUCTION TO BE FETCHED FROM MEMORY ANY OF 16 R'S CAN BE PC, DATA POINTER, ETC.

#### COSMAC MICROPROCESSOR ARCHITECTURE

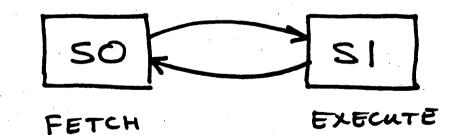

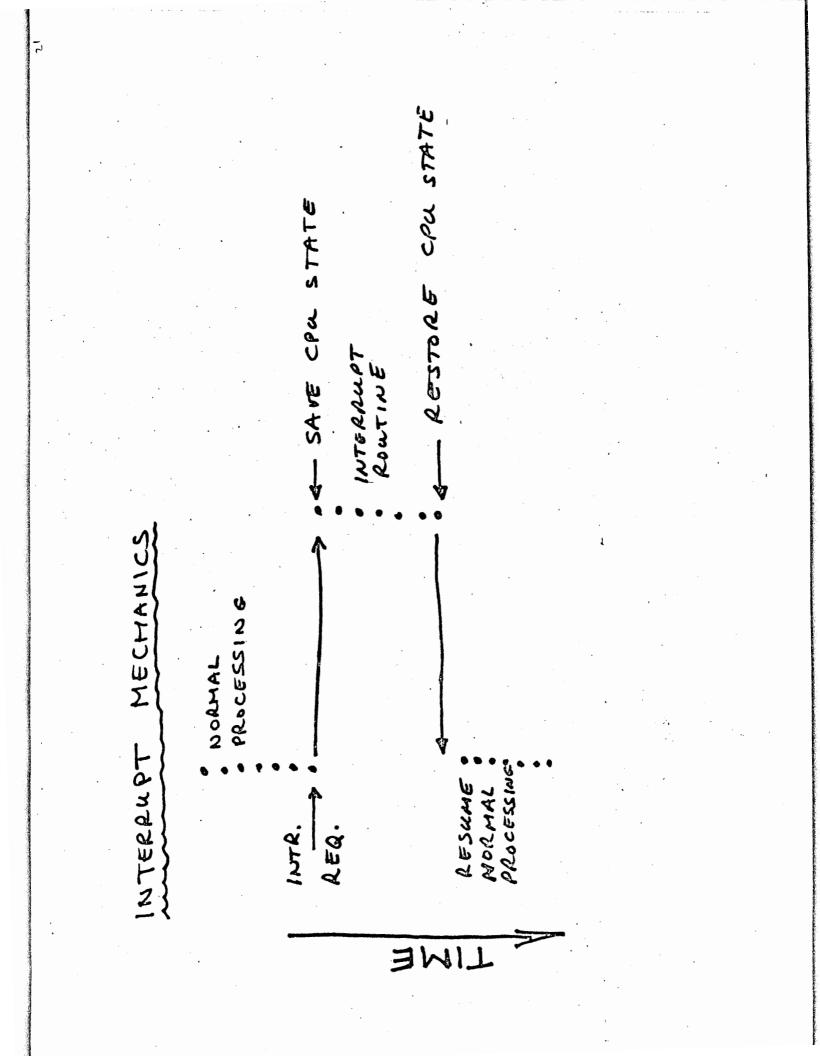

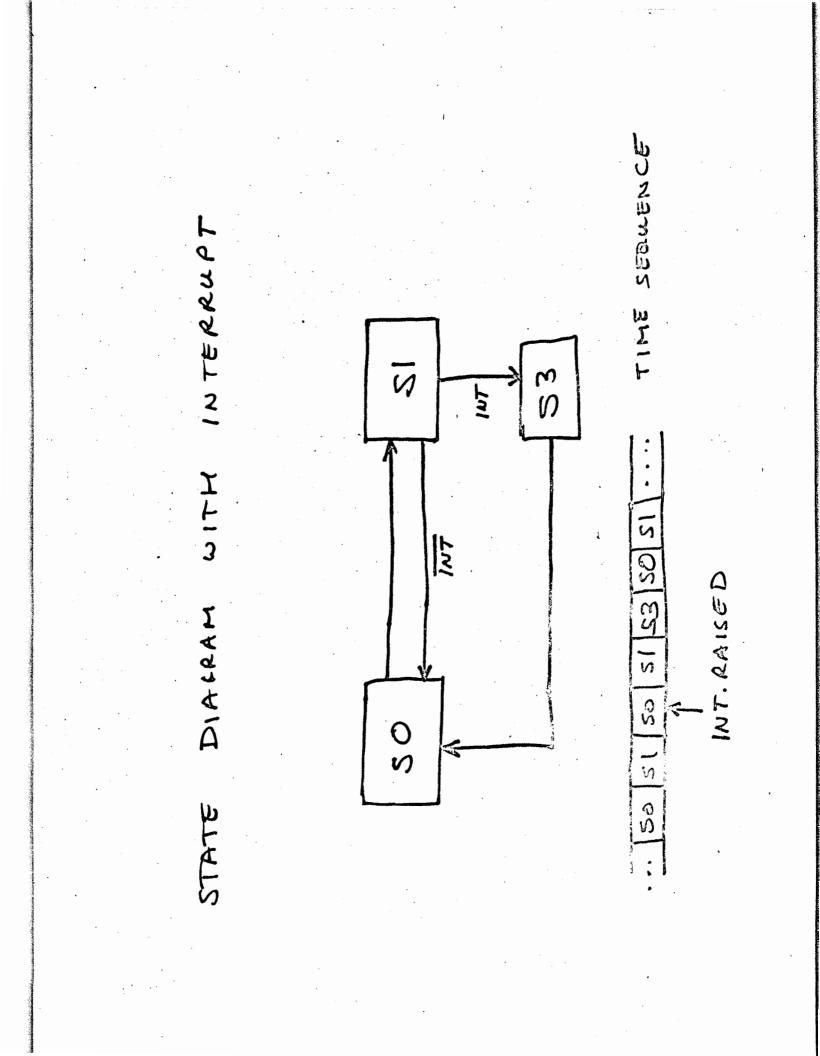

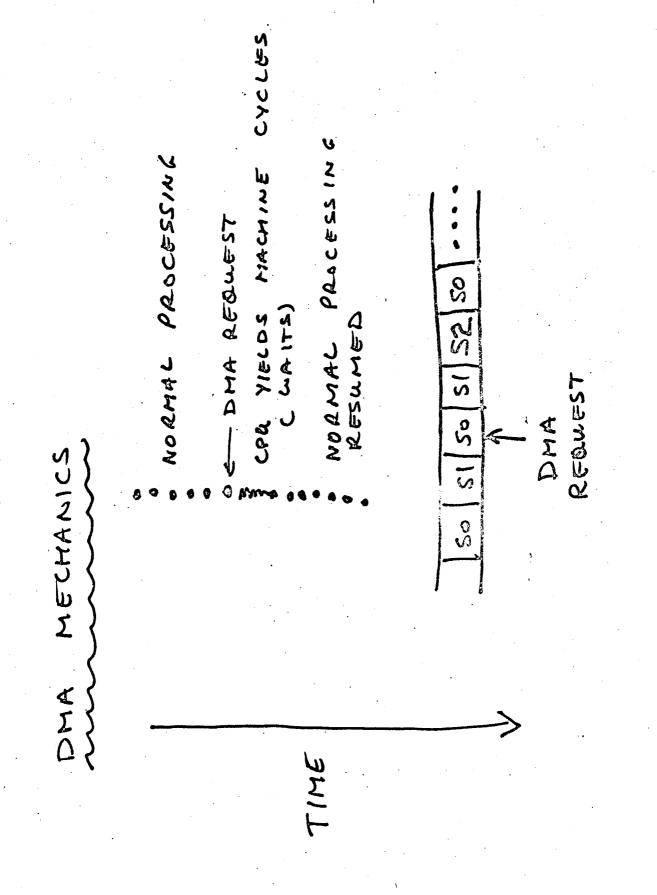

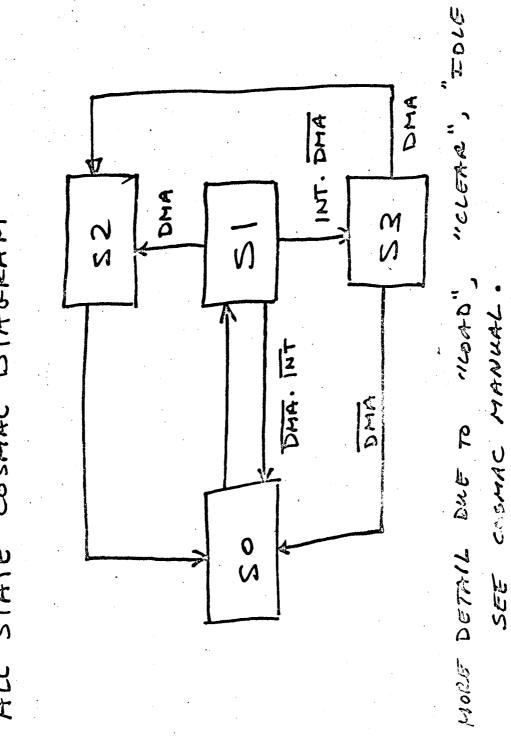

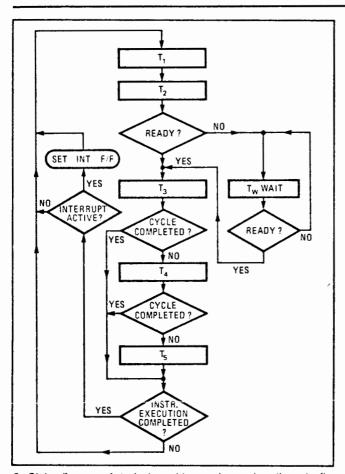

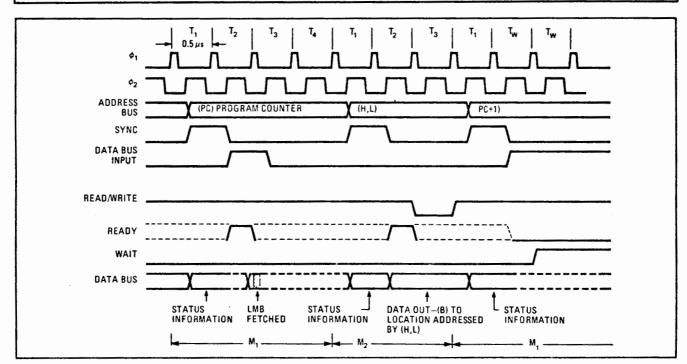

## 4 BASIC MACHINE STATES

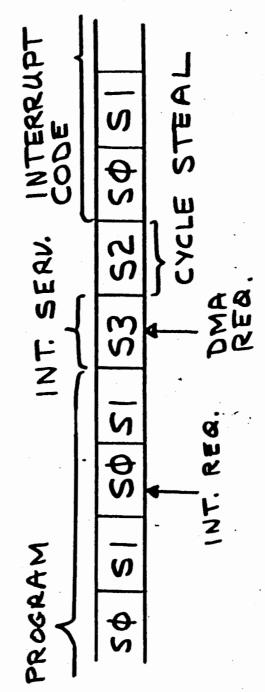

- SO FETCH Z NORMAL SI EXECUTE J PROCESSING SZ DMA

- S3 INTERRUPT

NORMAL PROCESSING STATE DIAGRAM

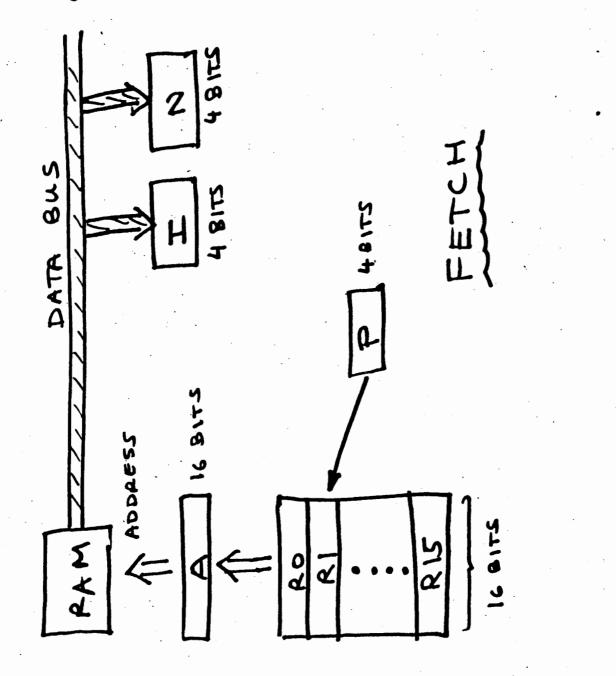

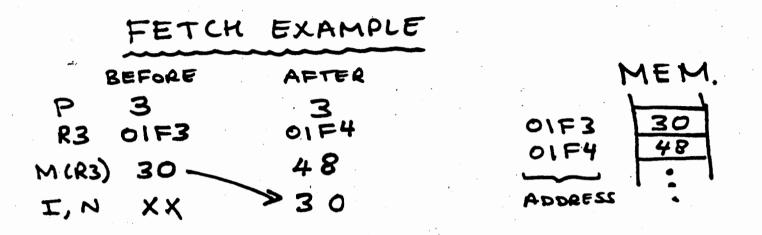

CADDRESS REFISTER 32 CPROGRAM COUNTER CONTENTS -> A DATA BUS E RCP) INCREMENTED FETCH CYCLE Z H RCP) A- SNO - HTYO p selects NTERNAL RCP)

8 8 175

ì

1

h

NOTE: COSMAC CHIP ADDRESS BUS IS 8 BITS. 16 BITS SENT OUT SEQUENTIALLY.

MICROTUTOR ONLY MAS 256 BYTES OF MEM. - SO IGNORE UPPER 8 BITS. EXECUTE CYCLE - SI

PXECUTION PERFORM IN STRUCTON DECODED TO DESIGED 2

WHAT IS A PROGRAM

EXECUTION

SEQUEN CE

- N M - 7

36

| •   | CLEAR BUTTON C SET RO = 0000 P=0 )<br>(I=0, N=0)                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------|

| ≥•` | IN BUTTON (MEM. LOAD OR PROGRAM RUN I/O                                                                         |

|     | START BUTTON ( START EXEC. OR STEP<br>THROUGH MEM. )                                                            |

|     | START BUTTON (START EXEC. OR STEP<br>THROUGH MEM.)<br># FOR COSMAC<br>ALWAYS START<br>EXECUTION AT ADDRESS 0001 |

|     |                                                                                                                 |

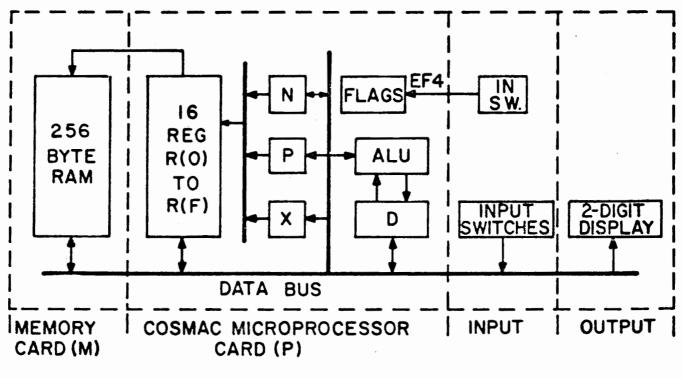

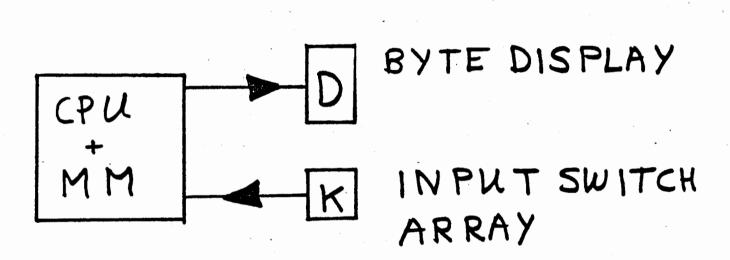

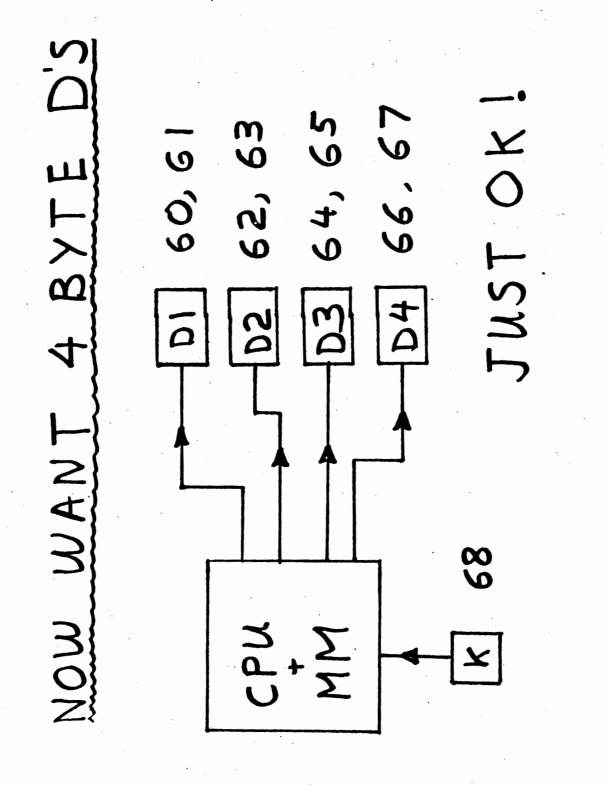

> 256 BYTES RAM (IGNORE UPPER 8 BITS OF ADR) > 2 HEX DIGITS DISPLAY (OUTPUT)

8 SWITCHES (IBYTE) (INPUT)

LOAD SWITCH (RUN/LOAD)

MICROTUTOR

Tator To A PROCRAM COUNTER

256 BYTES OF MM RECALL :

L 0 LPPER 8 BITS Lanore 介

MEMORY ADDRESS.

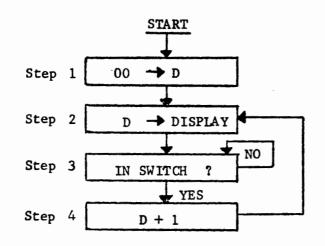

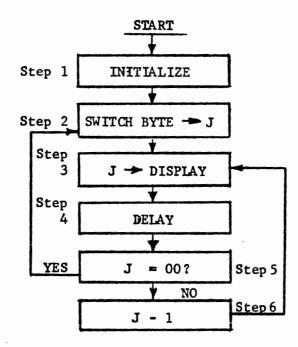

DISPLAY COUNT, STARTING WITH OO TO COUNT WHENEVER "IN" PRESSED ADA ~ ト 2 4 3

S

eg (

BRANCH WIEN - ALU FUNCTION してし Dutput FLOU DIAGRAM test ANY LUS 1 TO COUNT WALT FOR "IN" . UNCONDITIONAL BRANCH DISPLAY COUNT INITIALIZE STEPS A00 PROCAAN

30

(YANSPLAY) INST. TEST FOR "IN" 1521 output NEED

ADD INST.

BRANCH INST.

# LOOK AT THESE IN DETAIL

P7

Bus > MCRCX) M (R (K)) -> 8 45 RCX)+1 + RCX) H /0 00 C005 INSTR. OUTPUT H30 21 H 10 S1 N GENERAL 70 L Š V ] | 20 9 Z 10 0 0

217

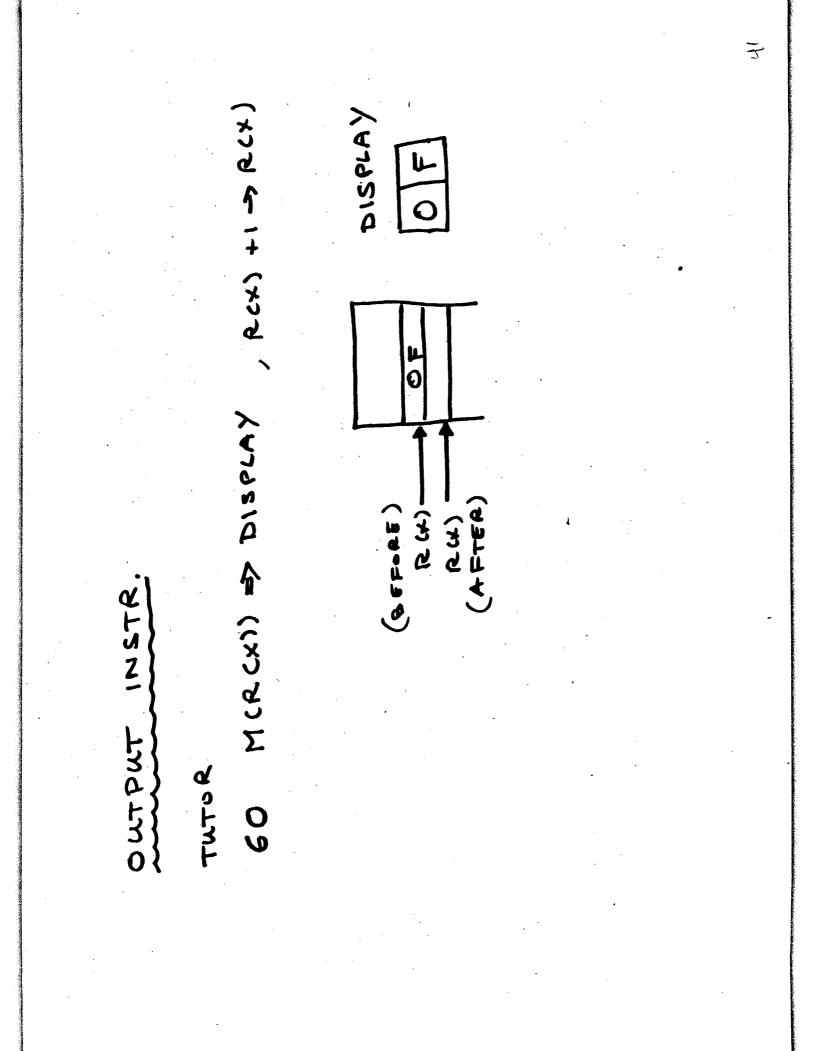

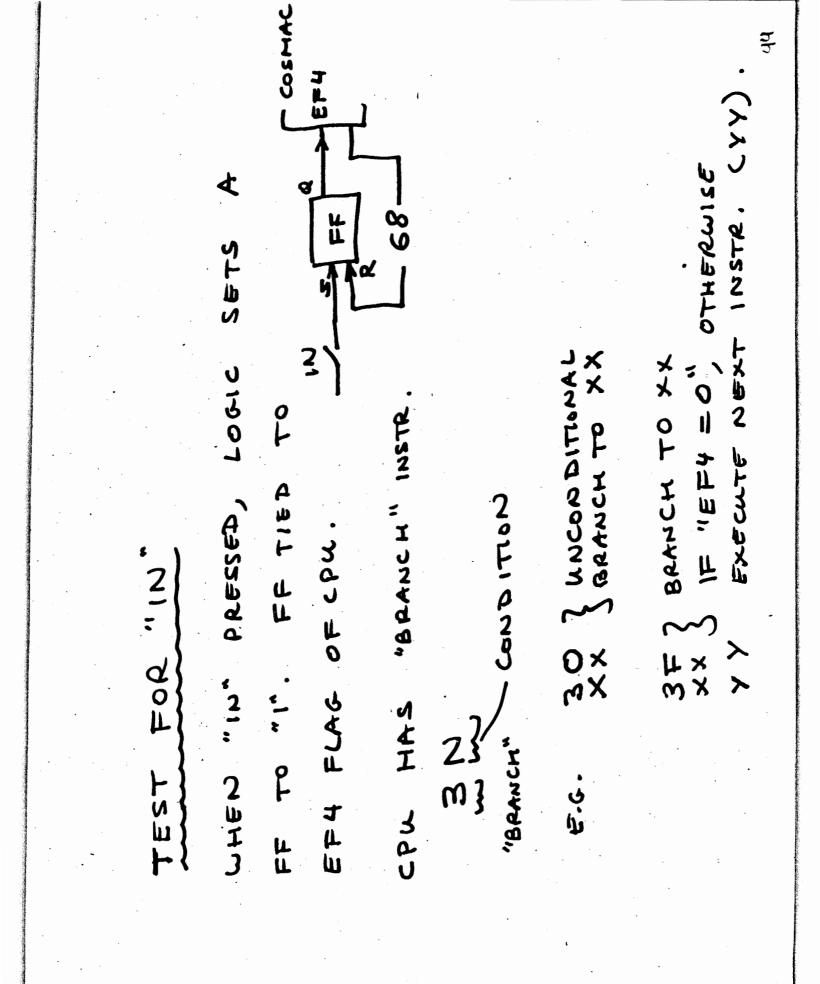

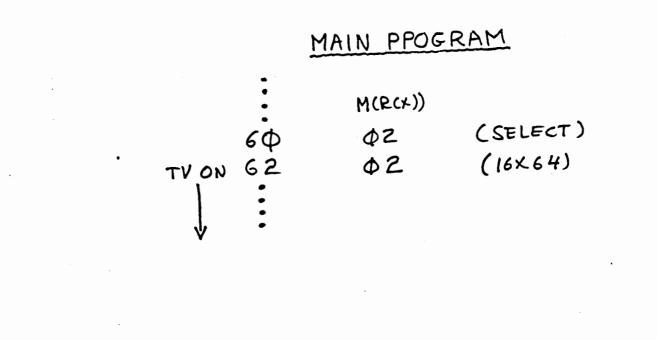

| SEX INSTR. (SET X REG.)<br>E.G. E3 MAKES R3 RECOME X REG.<br>IF X = P, THEN HAVE "IN LINE" DATA.<br>F.C. EO' SET PEX<br>E.C. EO' SET PEX<br>TUTOR ; 60 MCRCX) > DISPLAY, R(X)+1-720)<br>P=0 XX<br>P=0 XX<br>XX | FETCH 60 ING RO<br>EXEC 60 INC RO (P=X), SO SKIP "F7" |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

57 RESALT DATA PLAC SET "DF Ľ REGISTER L 0 Ω AND STORE LS, OR, AND, XOR, × X IF CARRY, A 2 ADA Ā Δ NEED ADD INSTR × × Ш M. op. D IÌ .00. MSTR マーベ

16 MCRW) -> D, RCN)+1 ->PCN) R(P)+1 - R(P) RETRIEVE FROM M(RCP) -> D. MM ADDRESS SPECIFIES MM ADDRESS STR DJMCRCN) LOAD IMMEDIATE SPECIFIES LOA LOH LOAD D 00 LL C40J STORE

<u>२</u> ४ L O STI 5 8 R(N)·O D D 1) R(N) 0 LOUER CGET LOW DENTIFIES (mon Two) LEGUTIFIES REGISTER REGISTER PLO 510 ₹} 90] CODE Co C

5

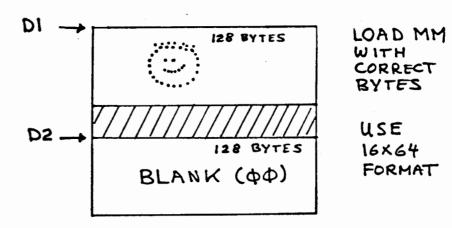

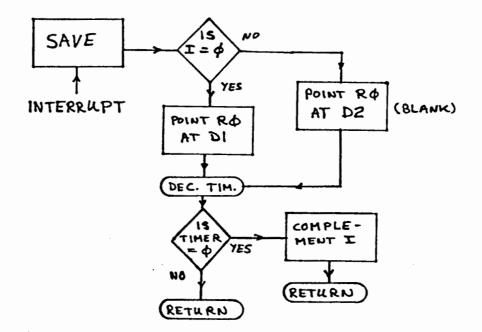

MM CODE 00 STORAGE BYTE FOR OUTPUT 00 F803 01 PUT OO IN D REGISTER 02 03 D-> R(3).0 (PUT 00 IN R(3).0)  $D \rightarrow M(R(3))$ R3 POINTS 06000 X REG. 15 R(2) 103F8 AT OO M(R(X)) -> DISPLAY, INC. R(3) DEC. R(2) (POINTS AT OO AGAIN) BRANCH TO 08 IF FF4 EO 09 CWAIT FOR "IN") OA FC ADD "OI" TO D, STORE RESULT OB 0 IN D 00 30 BRANCH TO 04 OD 04

> RECALL, R(0) = 0000 P = R(0) WHEN EXECUTIONBEGINS

### I. GENERAL

### A. Turning it ON

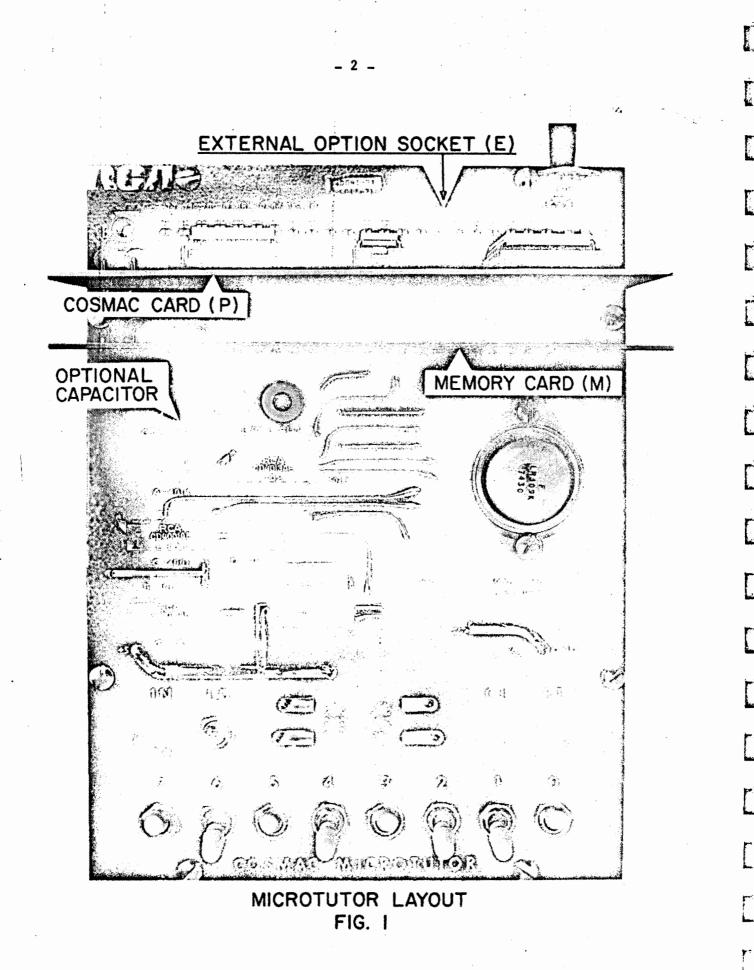

Figure 1 shows what MICROTUTOR looks like in case you don't have one. If you do have one, plug the memory card into the first socket (M). Plug the COSMAC microprocessor into the middle socket (P). The component (bumpy) side of these cards should face the rear. Don't apply power until the M and P cards are in unless you enjoy replacing integrated circuits.

Plug the power pack cord into the back of MICROTUTOR to turn it on. Pull the cord plug out to turn it off. If the red display lights don't come on when you plug in the power you are the proud owner of what is technically known as a lemon.

### B. Bits, Bytes, and Hex Digits

Before a stored program computer can run, it must have a program stored in its memory. Before storing a program in the MICROTUTOR memory, some basic definitions should be stored in your memory. Familiarity with binary notation (bits) is assumed. If this is a rash assumption, please correct the obvious gap in your otherwise outstanding educational background before proceeding.

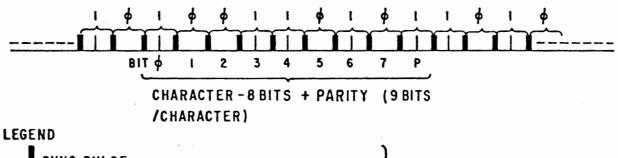

A byte is a group of 8 bits. The COSMAC microprocessor (along with many others) uses 8-bit bytes (or words). These 8 bits are labeled 0-7 corresponding to the eight MICROTUTOR byte input switches as shown below:

| SWITCH  | X | X | X | X | X | X | X | X |

|---------|---|---|---|---|---|---|---|---|

| BIT NO. | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

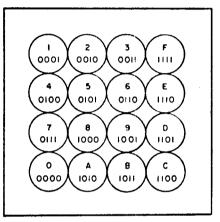

A byte can be divided into two 4-bit digits (D1 and D0). The high order digit (D1) comprises bits 7-6-5-4, while D0 comprises bits 3-2-1-0. Each 4-bit digit can be represented by a single HEX symbol as follows:

| BINARY | HE X | DECIMAL EQUIVALENT |

|--------|------|--------------------|

| 0000   | 0    | 0                  |

| 0001   | 1    | 1                  |

| 0010   | 2    | 2                  |

| 0011   | 3    | 3                  |

| 0100   | 4    | 4                  |

| 0101   | 5    | 5                  |

| 0110   | 6    | 6 <sup>.</sup>     |

| 0111   | 7    | 7                  |

| 1000   | 8    | 8                  |

| 1001   | 9    | 9                  |

| 1010   | A    | 10                 |

| 1011   | B    | 11                 |

| 1100   | C    | 12                 |

| 1101   | D    | 13                 |

| 1110   | E    | 14                 |

| 1111   | F    | 15                 |

The byte "01011011" can now be described as "5B" in HEX notation. Press the MICROTUTOR CL (Clear) switch and flip the LD (Load) switch up. Set "01011011" into the input switches (setting input switches up for "1" and down for "0"). Press IN and the byte will be displayed in hex form as "5B". Change the input switches and press IN (with LD up) to convert other binary numbers to HEX.

HEX is a base 16 numbering system which was developed by an obscure group of bald headed, 16 toed programmers. It is only through the development of notational jargon such as bit, byte, and HEX that we can maintain our superiority over the average citizen. HEX notation will be used throughout this manual unless noted otherwise.

### C. Down Memory Lane

Whoever said that memory is fundamental to a stored program computer has been long forgotten. Just in case he (or she) was right, MICROTUTOR is provided with a memory. The MICROTUTOR memory can store up to 256 bytes in locations numbered consecutively from 00 to FF. The number of a stored byte location is called its memory address. The notation M(4A) is used to specify the <u>memory byte</u> located at <u>address 4A</u>. For example, four bytes might be stored in the first four memory locations as follows:

| ADDRESS (M) | BYTE |

|-------------|------|

| 00          | E2   |

| 01          | 27   |

| 02          | 51   |

| 03          | F6   |

M(02) would then represent the memory byte, addressed by 02, which is 51. The ability not to confuse memory addresses with the bytes stored at those addresses separates programmers from normal people.

When a byte is stored in memory at a specified location or address it <u>replaces</u> the byte previously stored at that location. When a byte is fetched or read from memory, a copy of it remains stored. (This is analogous to recording or playing back magnetic tape.)

D. Getting It In (Program Loading)

Computer <u>instructions</u> are individual binary <u>codes</u> or <u>bytes</u> stored in memory. Each byte specifies an individual computer <u>operation</u> such as store an input byte, add two bytes, display an output byte, etc. A sequence of such instructions is called a program. The computer obtains each instruction, as required, from memory and performs the specified operation.

The following is a short COSMAC MICROTUTOR program code that can be stored in memory:

| ADDRESS (M) | INSTRUCTION BYTE (CODE) |

|-------------|-------------------------|

| 00          | 00                      |

| 01          | F8                      |

| 02          | 00                      |

| 03          | A3                      |

| 04          | 53                      |

| 05          | E3                      |

| 06          | 60                      |

| 07          | 23                      |

| 08          | 3F                      |

| 09          | 08                      |

| 0A          | FC                      |

| OB          | 01                      |

| 0C          | 30                      |

| OD          | 04                      |

Flip LD (Load) up. This tells MICROTUTOR that you want to load a program. Push CL (Clear) and loading of the following sequence will start at memory address 00. You are now ready to load your first program. Do not become nervous or excited as this will lead to mistaekes. Set the input switches to 00 (Binary 0000000) and push IN. 00 is displayed and stored at address 00. MICROTUTOR also advances its load memory pointer to 01 so that your next input byte will be stored at memory address 01. This ability to anticipate your next move led to the early belief that computers were giant brains. (This belief was later shattered by the discovery of the first program bug.)

Proceeding, set the input switches to the next instruction byte, F8 (Binary 11111000), and push IN to store it at memory address 01. Continue loading the rest of the program bytes into memory until the last instruction (04) has been stored.

### E. So You Made A Mistake

You can check memory with LD up. Push CL to return to memory address 00. Now push ST and the byte stored at address 00 will be displayed. Push ST again and the next byte (F8) will be shown. Continue pushing ST to check that all bytes in the program are properly stored.

Checking the program in memory is generally skipped by those of us who don't make errors. Some programmers actually prefer the challenge and added fun of trying to run an improperly loaded program. If you are only interested in getting a program to run, include the checking step.

If one of your memory bytes is wrong you can loudly blame it on the computer or quietly change it to the right value. To change a byte, leave LD up and push CL. Repeatedly push ST until the byte just before the one you want to change is displayed. Set the input switches to the byte code you want to substitute for the wrong one and push IN. The new byte will replace the wrong one in memory and be displayed. Pressing ST will resume memory stepping for correction of a subsequent error in the byte sequence.

### F. Pushing the Start Button

With the above program properly stored in memory you are ready to run. LD should be down. Always push CL to start the program at the beginning. (Starting programs at the end only works for backward programmers.) After pushing CL push ST (Start). The program is now running.

Unfortunately nothing spectacular happens when this program is running so you'll just have to take our word for it. If you are a doubting Thomas type, you can verify that the program is running by pushing IN. Each time you press IN the program adds 1 to the display. This hex counter program only required 14 bytes. You really couldn't expect anything too exciting, could you?

To stop the program, press CL. Now nothing happens when you press IN, does it? To restart the program, press ST. This program remains stored in memory until you disconnect power or load a new program. Want to become a NIM game hustler? Find a friend to play with. (If you don't have a friend, you are well on your way toward becoming a professional programmer.) Start the computer (00 displayed). You and the other player take turns. On each turn add 1, 2, or 3 to the displayed hex number (press IN 1, 2, or 3 times). The first player to reach 10 (decimal 16) wins. If you graciously let the other player have the first turn you can always win (unless he cheats). We'll leave the how as an exercise for the reader.

Later on a program which plays this game <u>against you</u> (and always wins) will be described. In the meantime, this program can be used to illustrate a major advantage of computers. This advantage lies in the ease with which operation can be changed. For example, changing the 01 byte at M(OB) to 02 will increment the display by 02 each time IN is pushed. Substituting an FF instruction for the FC at M(OA) will decrement the display each time IN is pushed.

The next section provides some more programs to load and play with before getting down to the nitty-gritty details of hardware and programming.

## **SPECIAL FEATURE:**

# A Simplified Microcomputer Architecture

Joe Weisbecker RCA Laboratories

Copyright 1974 by The Institute of Electrical and Electronics Engineers, Inc. Reprinted, with permission, from COMPUTER, March 1974.

### Introduction

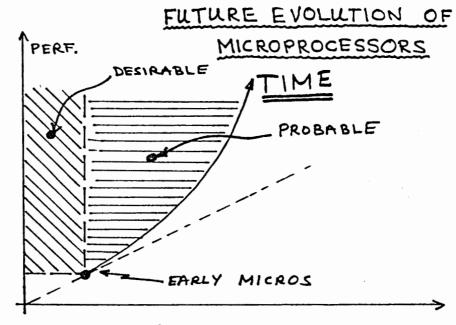

The motivation behind this work has been the view that for 20 years computer hardware has become increasingly complex, languages more devious, and operating systems less efficient. Now, microcomputers afford some of us the opportunity to return to simpler systems. Inexpensive, LSI microcomputers could open up vast new markets. Unfortunately, development of these markets may be delayed by undue emphasis on performance levels which prohibit minimum cost. We are already promised more complex next-generation microcomputers before the initial ones have been widely applied. This paper discusses these points and describes a simplified microcomputer architecture that offers maximum flexibility at minimum cost. Design philosophy, programming considerations, and typical systems are also discussed. Experience with breadboard versions of this architecture has verified its usefulness over a surprisingly wide range of potential applications.

### Overview

Large scale integration of semiconductor devices has finally become a practical reality. The long-awaited revolution in electronic products appears to be at hand. The basis of this revolution is the ability to provide complex electronics at greatly reduced prices. Major cost reduction opens up entirely new markets and is as significant a development as the invention of the vacuum tube or transistor.

The four-function electronic calculator represents the first wave of the revolution. Further new markets will emerge with the ability to provide complete stored-program computers at a fraction of current minicomputer costs. A number of microcomputer chip sets have already been announced.<sup>1,2</sup> We can expect a proliferation of micro-computer types and products based on them over the next several years. Unfortunately, old habits are hard to break, and we can also expect to see increased emphasis on performance instead of cost.<sup>3</sup> This could easily obscure the fact that many major new markets will depend primarily on absolute cost.<sup>7,8</sup>

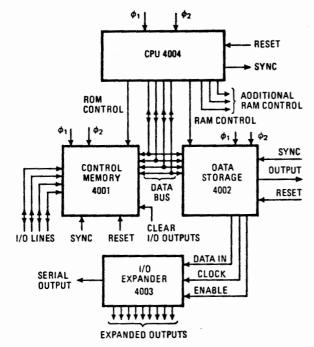

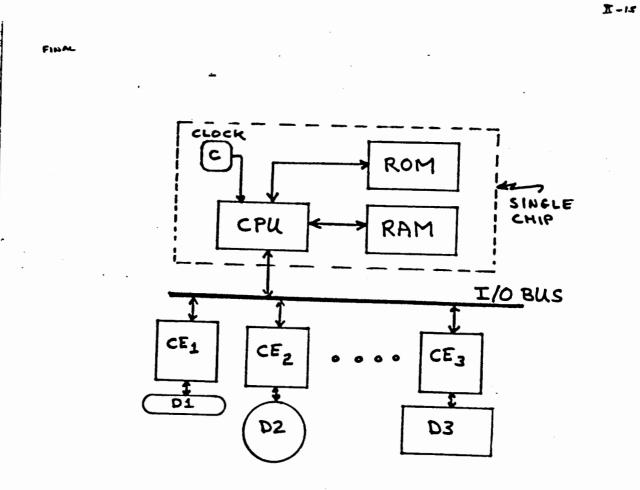

Consumer, educational, small business, and communications markets are prime targets for truly low-cost microcomputer-based products. The architecture described here was developed to satisfy the requirements of these potential new markets. Practical, stand-alone systems (including input/output device control and memory) requiring as few as 6 LSI chips are feasible with this architecture. Discrete TTL and COS/MOS breadboards of such potential systems have been breadboarded and programmed. Based on this experience, the microcomputer described appears to satisfy the requirements of a much wider range of applications than originally intended. It also appears to be simpler than most existing microcomputers. It is estimated that this new architecture compares favorably with the complexity of current four-function calculator chips. This simplicity is expected to provide significant production advantages. Improved yields and decreased testing costs are anticipated.

Since LSI improvements are permitting ever larger numbers of devices per chip, there are definite long term advantages in minimizing microcomputer complexity. If the microcomputer is prevented from growing in complexity as the device per chip ratio improves, more of the system can be pulled back into a single chip. For example, small systems in which both memory and microcomputer are provided on a single chip become feasible, resulting in added, long term, cost reduction potential. This approach is ruled out, however, when increased device per chip ratios are used to provide more complex microprocessors.

### **Design Philosophy**

Minimum system cost is the primary goal. To achieve this goal an architecture is required that is both simple and flexible. Simplified computer architecture has received relatively little attention in the literature. Prior approaches toward simplified computers appear to be incompatible with microcomputer application goals.<sup>4,5,9</sup>

The architecture that was finally developed evolved from examining proposed applications. Another approach would have started with a more or less conventional minicomputer architecture and instruction set. This latter approach was discarded because of fundamental differences in minicomputer and microcomputer applications. The most obvious mini-micro difference is cost. Because of their higher cost, minicomputers must generally be structured to compete on a free standing cost/performance basis with a high degree of upward expansion capability and the need to support relatively efficient operating systems, etc. Simple, inexpensive microcomputers will generally be imbedded in special-purpose products. They do not require the same degree of upward expansion or an excessive preoccupation with cost/performance ratios. (Who cares if a \$20 microcomputer chip is efficiently utilized?) Used to replace custom logic, the microcomputer can be designed to put more burden on the programmer. Software (in many cases) will be developed on larger computers. Because of such differences it was felt that a minicomputer starting point would not yield the simplest architecture.

Since a single-chip microcomputer promises minimum cost, the architecture was constrained to a 40-pin interface. Smaller microcomputer interfaces tend to require extensive multiplexing of interface signals, and that adds demultiplexing logic external to the microcomputer chip. This increases system cost.

An 8-bit parallel (or byte) architecture was chosen. This yields maximum performance consistent with interface pin constraints and is compatible with input/output requirements. One- and four-bit organizations unduly restrict the range of potential applications. Sixteen or more bits exceed single-chip pin constraints or impose the need for multiplexed word transfers. Since continued memory cost reduction is anticipated, heavy reliance is placed on techniques using memory to reduce hardwired logic complexity. It is also apparent that many microcomputer applications will fall into the intelligent buffer category. For these reasons, direct memory addressing capability of up to 64K bytes is provided. RAM and ROM can be mixed in any combination via a common memory interface. This is a distinct simplification over an architecture that provides separate RAM and ROM interfaces. The common RAM/ROM interface also enhances flexibility. A single LSI chip containing both ROM and RAM segments will suffice for many applications – and that results in system simplicity.

While low memory costs can be expected, very low cost systems will only result from minimizing memory capacity requirements. A unique architecture was devised which uses an 8-bit instruction format. This permits compact programs and subroutines. Useful systems requiring 1024 bytes of memory or less are possible with this format.

Random control logic uses chip area less efficiently than register/memory arrays. For this reason a very simple, fixed cycle, microinstruction set was developed to reduce required control logic. The user has the option of programming directly in microcode, using a set of subroutines stored in memory (ROM/RAM), or employing a combination of these approaches. Sets of subroutines stored in memory are equivalent to applications-oriented macroinstructions and can readily be provided where ease of programming is important. On the other hand, many systems will utilize the microcomputer as a substitute for special-purpose logic and can be programmed directly and efficiently in microcode. This approach retains most of the advantages of a microprogrammed computer but eliminates much of the specialized, hardwired, sequencing and control logic usually associated with microprogrammed systems.<sup>6</sup> Simple, short subroutine-calling byte sequences provide flexible macroinstruction definition.

Whether used as a component of larger systems or as a free-standing computer, the microcomputer architecture requires efficient, flexible, input/output capability. This is provided via programmed byte transfers and a built-in direct memory access channel. Programmed I/O byte transfer instructions provide maximum flexibility for I/O selection, control, and data transfer. The direct memory access channel facilitates high-speed 1/O block transfer, TV display refresh, and initial program loading with a minimum of external logic. While the inclusion of a direct memory access channel adds negligible complexity to the microcomputer architecture, it greatly simplifies system design, and that leads to reduced overall cost. In addition to the two basic I/O modes, four uncommitted flag lines are provided for activation by external devices. These flags can be tested as required by program. A flexible program interrupt capability also exists. Individual reset and load lines minimize external initializing logic.

The overall design philosophy consisted of developing a simple, flexible, microcomputer architecture which satisfies a wide range of potential applications at minimum cost. Performance levels were chosen to satisfy large volume applications without overkill. The resulting architecture can be implemented initially on one or two chips using slow MOS technology. Instruction execution times in the range of 4 to 8 microseconds are anticipated with LSI technologies that approach current TTL speeds. Experimental work has demonstrated that this performance level is adequate for most anticipated applications.

### **Microcomputer Architecture**

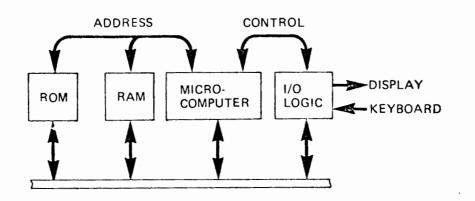

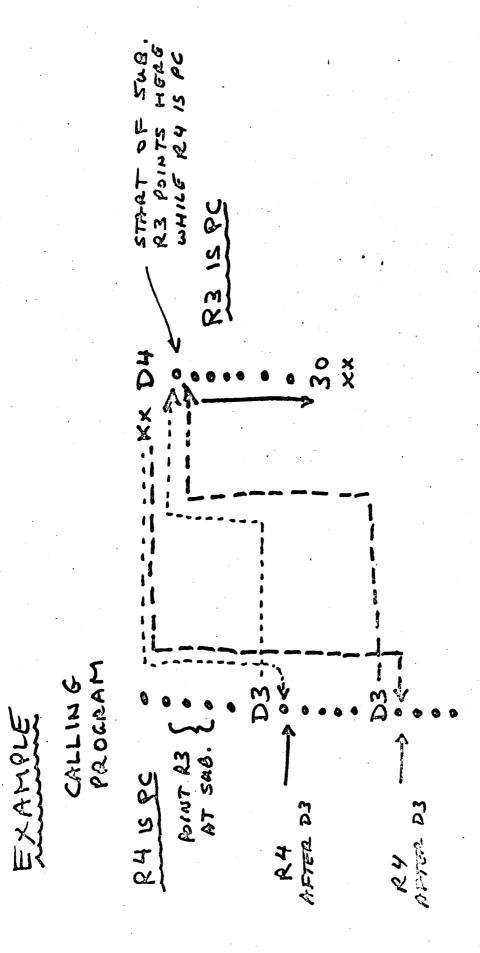

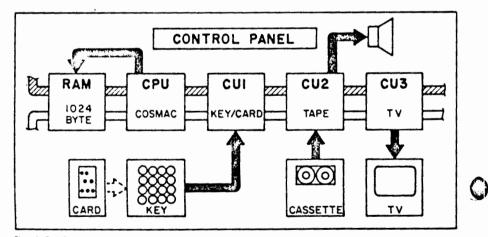

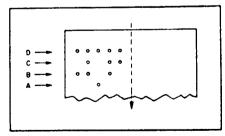

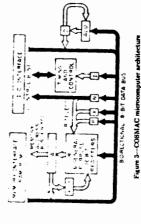

Figure 1 illustrates the microcomputer architecture. "R" represents an array of sixteen 16-bit general-purpose registers. (This is essentially a 16x16 bit RAM.)

### Figure 1 here.

P, X, and N are three 4-bit registers. The contents of P, X, or N select one of the 16 R registers. R(N) will be used to denote the specific R register selected by the 4-bit hex digit contained in the N register. RO(N) denotes the low-order 8 bits (byte) of the R register selected by N. R1(N) denotes the high-order byte. The contents of a selected R register (2 bytes) can be transferred to the A register. The 16 bits in A are used to address an external memory byte via an 8-bit multiplexed memory address bus. The 16-bit word in A can be incremented or decremented by "1" and written back into a selected R register.

M[R(N)] refers to a 1-byte memory location addressed by the contents of R(N). This indirect addressing system is basic to the simplicity and flexibility of the architecture.

D is an 8-bit register that functions as an accumulator. The ALU is an 8-bit logic network for performing binary add, subtract, logical "and", "or" and "exclusive or" on two 8-bit operands. One operand is the bus byte and the other is contained in the D register. The D register can also be shifted right one bit position. Add, subtract, and shift operations set a 1-bit overflow register (not shown) which can be tested by branch instructions.

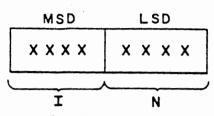

I is a 4-bit instruction register. Four-bit operation codes are placed in I and decoded to control instruction execution. Bytes can be read onto the common data bus from any of the registers, external memory, or I/O devices. A data bus byte can, in turn, be transferred to a register, memory, or I/O device.

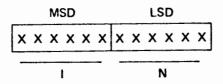

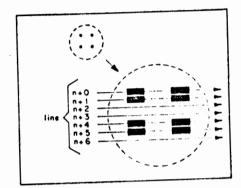

The operation of the microcomputer is best described in terms of its instruction set. A 1-byte instruction format is used as shown in Figure 2.

Each instruction requires two machine cycles. The first cycle causes an 8-bit instruction to be fetched from external memory and placed in the I and N registers. This is written as  $M[R(P)] \rightarrow I, N$ . The 4-bit digit in P selects R. R(P) is then transferred to A and used to address memory. While waiting for the memory access, A is incremented by "1" and replaces the original contents of R(P). The most significant digit of M[R(P)] is placed in I and the least significant digit is placed in N. At the end of an instruction fetch cycle, I and N always contain the 8-bit instruction originally addressed by the current program counter [R(P)], and this program counter has been incremented to point to the next memory byte in sequence. It should be noted that any R register can be selected as the current program counter by merely changing the digit in register P. Multiple program counter systems and simple branch and link operations are readily achieved with this approach.

The next machine cycle always causes the instruction contained in I and N to be executed. This fixed 2-cycle, fetch-execute sequence simplifies control logic and permits program interruption or direct memory access cycle stealing to occur only between instructions. This results in even further control simplification. Since the operation code in I is limited to 4 bits, only 16 instruction types need be decoded. The 16 possible operations specified in the hex digit in I are listed below:

### **Register Operations**

- [1] Increment R(N) by 1

- [2] Decrement R(N) by 1

- [8] Transfer RO(N) to D

- [9] Transfer RI(N) to D

- [A] Transfer D to RO(N)

- [B] Transfer D to R1(N)

- [C] Transfer D0 to R00(N)

Figure 2. Eight-Bit Instruction Format

### **Memory Operations**

- [4] Load D from M(R(N)) and increment R(N)

- [5] Store D in M(R(N))

### **Miscellaneous Operations**

- [0] Idle

- [3] Branch

- [6] Input/output byte transfer

- [7] Interrupt control

- [D] Set P to value in N

- [E] Set X to value in N

- [F] ALU operations

The first group of instructions permits selecting any 16-bit general purpose register (R) and incrementing or decrementing it. Upper or lower halves of selected R registers can be copied into D or set from D by these instructions. Operation "C" permits the least significant 4 bits of D to be set into the least significant 4-bit positions of any R register. This facilitates table lookup operations using 4-bit digit arguments.

The two basic memory operations permit loading D from memory and storing D in memory. Used in combination with the register operations, selected general purpose registers can be set or stored. Instruction "4" is of particular interest. When N=P, this instruction permits a byte to be retrieved directly from the program stream and placed in D. Since R(N) is the program counter, incrementing it maintains program counter integrity. A 3-byte sequence serves to set a 1-byte constant into any R register. This technique is normally used for initialization of R registers.

The last group of operations provides a variety of functions. The idle state can be entered via program or a reset

line provided in the microprocessor interface. The idle state waits for externally generated program interrupts or direct memory access requests. The branch instruction performs a test specified by the value in N. As a result of this test the next byte in memory, as addressed by R(P), is either skipped or placed in the lower half of R(P). This latter action causes a branch within the current 256-byte memory segment. Tests specified by N include zero in D, the states of four externally activated flags, and the status of the ALU overflow register. Two instructions "D" and "E" permit the current digit in the P or X register to be modified. The "D" instruction provides the ability to change program counters at any point in a program. For example, "D4" would immediately change the current program counter to R(4). Branch and link operations are thereby facilitated. The "E" instruction permits changing the ALU operand or I/O byte address pointer. Instruction "F" permits 8-bit ALU operations. N designates the specific ALU operation to be performed. One of the operands comprises the byte contained in D. The other operand comes from memory. The second operand can be addressed by either R(P) or R(X) as specified by N. The result of ALU operations always replaces the original byte in D.

Instruction "6" permits byte transfers between memory and I/O devices via the common byte bus. The value of N specifies the direction of the byte transfer. M[R(X)] can be sent to an I/O device or an I/O device byte stored at M[R(X)]. In the former case R(X) is incremented, permitting X to be set equal to the current P value. The digit in N is made available externally during execution of the I/O byte transfer instruction. This digit code can be used by external I/O device logic to interpret the common bus byte. For example, specific N codes might specify that an output byte be interpreted as an I/O device selection code, a control code, or a data byte. Other N codes might cause status or data bytes to be supplied by an I/O device. In small systems the N code can directly select and control I/O devices.

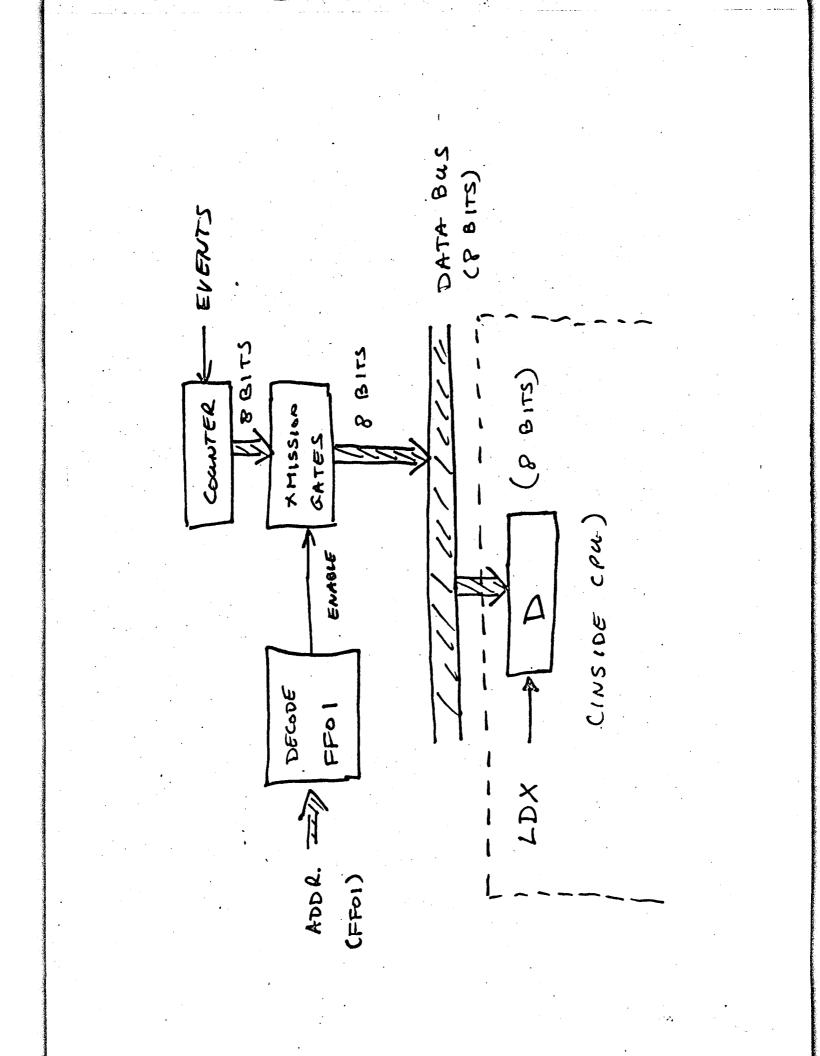

Four flag lines that can be activated by I/O devices are provided. These can be used as general purpose I/O device status indicators (byte ready, error, etc.). These flag lines are tested by the branch instruction. Two interface lines control the built-in direct memory access channel. An I/O device can activate either an input or an output byte request line. At the end of execution of the current instruction, a direct memory access channel cycle will occur, causing the requested memory-I/O device byte transfer to occur. Contiguous direct memory access cycles are permitted for fast-burst transfers. R(0) is used for addressing memory during direct memory access cycles and is automatically incremented by 1 following each byte transfer. Once initiated, blocks of data can be efficiently transferred between an I/O device and memory independent from normal program execution.

A program interrupt line can be activated at any time by external means. At the end of the current instruction an interrupt cycle will occur. During this cycle X and P are placed in an 8-bit temporary storage register (T). P is then set to 1 and X is set to 2. Normal fetching and execution are then resumed. Activation of the interrupt line therefore causes a branch to the instruction stream addressed by R(1). R(2) should point to a memory area used by the interrupt routine to store the state of the machine for subsequent return from interrupt. Instruction "7" with N equal to 8 stores the contents of T in the memory location specified by R(X). It is a "save state" type instruction. If N is 0, instruction "7" causes M[R(X)] to be placed in P and X. R(X) is incremented and an interrupt mask bit is reset. This instruction provides a "return after interrupt" function. The interrupt mask bit inhibits further responses to external activation of the interrupt line. This mask is always set by an interrupt, permitting multiple interrupts to be queued under program control.

### **Programming Considerations**

Since the instruction set of this microcomputer differs considerably from that normally encountered, some comments relative to programming are in order.

A major difference between this architecture and more conventional organizations lies in the complete separation of operation codes and memory addresses. Conventional instructions have one or more addresses associated with each operation code. This system utilizes a limited table of memory addresses contained in a set of general-purpose registers. These registers may also be used for program counters and data storage. Their use is entirely controlled by program [with the exception of R(0), R(1), and R(2)]. This structure is basic to the simplicity and flexibility of the architecture. It also permits the use of a short, 8-bit, instruction format, which in turn results in compact coding.

It has long been realized that storing a full memory address with each operation code is inefficient, since a small number of unique memory addresses are repeated many times throughout a program. Various abbreviated addressing schemes have been used to permit more compact programs. These are almost always offered as optional alternatives to providing a full address in each instruction. Here we must always obtain a memory address from the limited, current set in the 16 general-purpose registers. We might intuitively suspect that this would be an unduly restrictive approach. Surprisingly, it turns out to be relatively easy to write programs and highly efficient relative to memory usage. A variety of programmers, from those who have only used high-level languages to engineers with limited programming experience, have had little difficulty in adapting to this architecture.

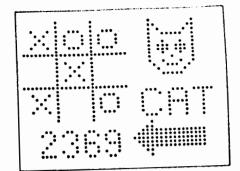

A number of programs have been written for a breadboard version of the microcomputer with a variety of I/O device attachments. This experience has validated the flexibility and efficiency of the architecture. For example, a four-function calculator program was found to require only 1024 bytes of memory, most of which could be ROM. This included provision for keyboard input, operands up to 30 digits, TV display refresh storage, 5x7 digit font conversion table, push-down stack, and algorithms for signed, n-digit decimal add, subtract, multiply, and divide. An interpreter for a simple, decimal, tutorial language was written in less than 600 bytes. A number of game and/or educational programs require well under 1000 bytes of memory. Many small business and communications systems programs are possible with 2000 to 4000 bytes of memory.

While the instruction set initially appears limited, it should be kept in mind that each operation requires only one byte of storage (ROM or RAM). Short sequences of these microinstructions readily provide macro-operations.

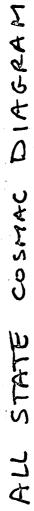

Apparent weaknesses in the architecture are the limited branch capability (within 256 bytes) and the lack of a hardwired program stack for multilevel nested subroutines. These apparent oversights are the result of a deliberate design philosophy which eliminates special-purpose logic for those functions which are performed easily by subroutines. The architecture permits a flexible subroutine "call" and "return" system requiring less than 70 bytes of memory. This includes a push-down stack for nested subroutines. If this system is provided in software (or firmware), it can be tailored to individual applications.

Where extensive programming effort is required, a set of applications-oriented subroutines is easily developed. These subroutines constitute a user-oriented macroinstruction set for minimum-effort programming. This technique has proved extremely useful in an experimental small business system.

For microcode programming, an assembly language has been developed. This approach considerably simplifies machine language coding. An interactive simulator greatly facilitates initial program debugging. Both of these microcomputer software support systems are readily modified to run on existing timesharing systems.

In general, the simplified microcomputer presents no difficulty in programming. It provides a simple set of short, easy-to-understand microinstructions that do not require high skill levels to use. For specific applications, tailored macroinstructions are readily provided via a flexible subroutine handling system.

### Typical Systems

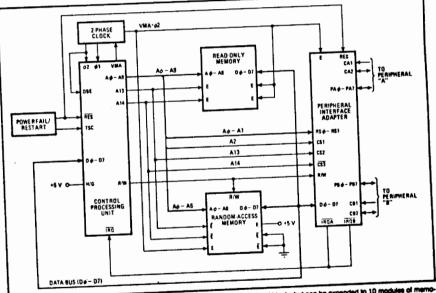

Several systems using the microcomputer can be outlined. Many others are of course possible. Figure 3 indicates a possible microcomputer-based calculator.

ROM and RAM might be provided on one chip, resulting in a basic 3-chip calculator. Functions could easily be added with ROM increments. This type of system could also provide a programmable calculator.

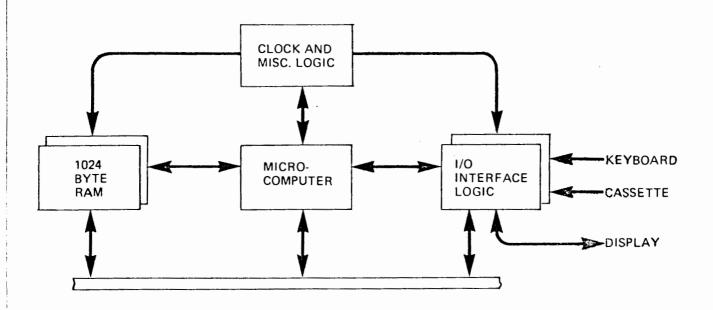

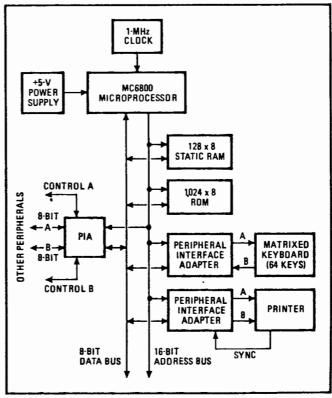

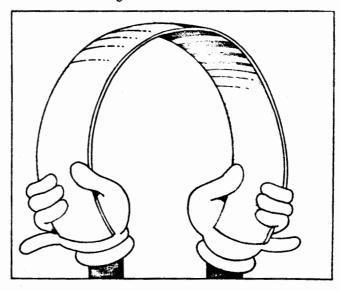

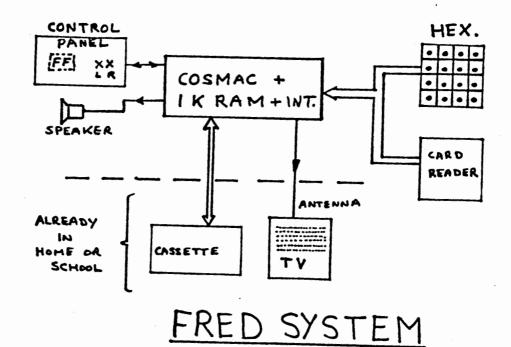

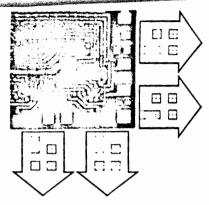

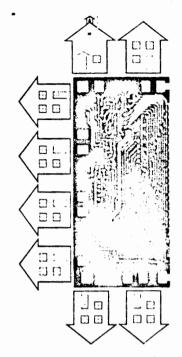

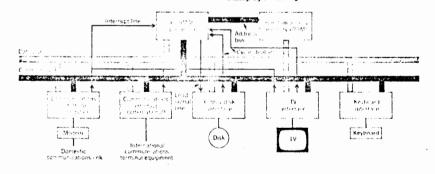

Figure 4 illustrates a stand-alone system which might require only 6 LSI chips total.

It is assumed that 4x1024 bit memory chips will be available within the next several years. Subsequent LSI improvements could further reduce the chip count. Use of a small keyboard, audio cassette<sup>10,11</sup> and CRT display might reduce system cost to a few hundred dollars. Such a system could have wide application in consumer and educational markets. With more memory, hardcopy output, and low cost floppy disk or magnetic bubble bulk storage, this system would provide the basis for a wide range of inexpensive, turnkey, small business systems.

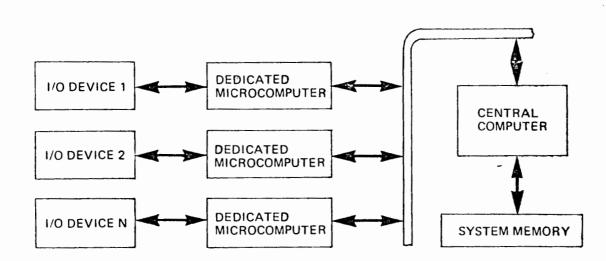

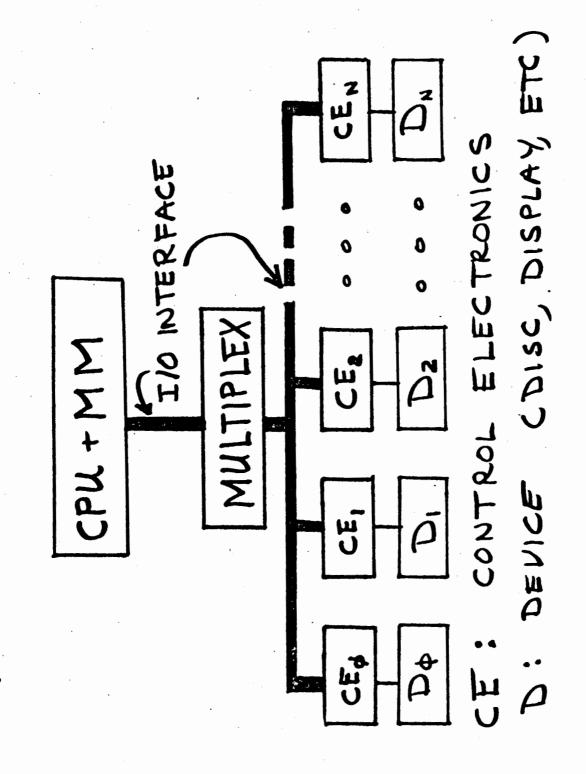

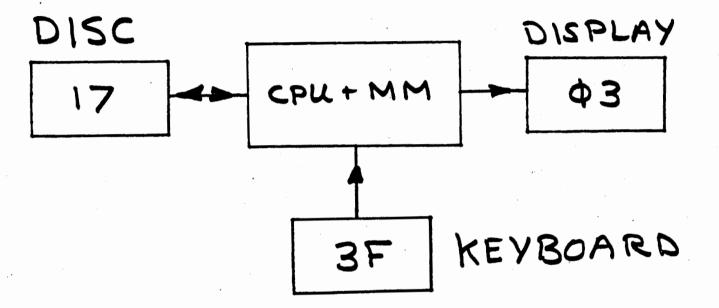

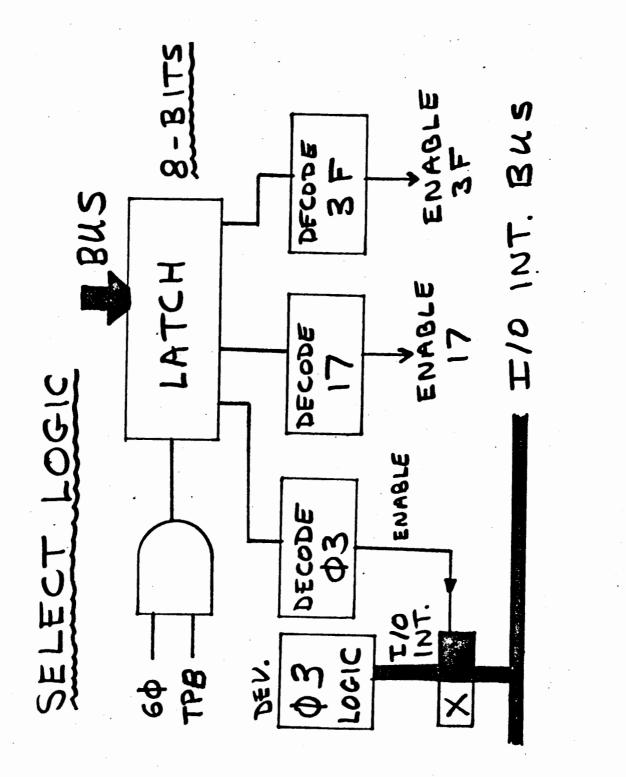

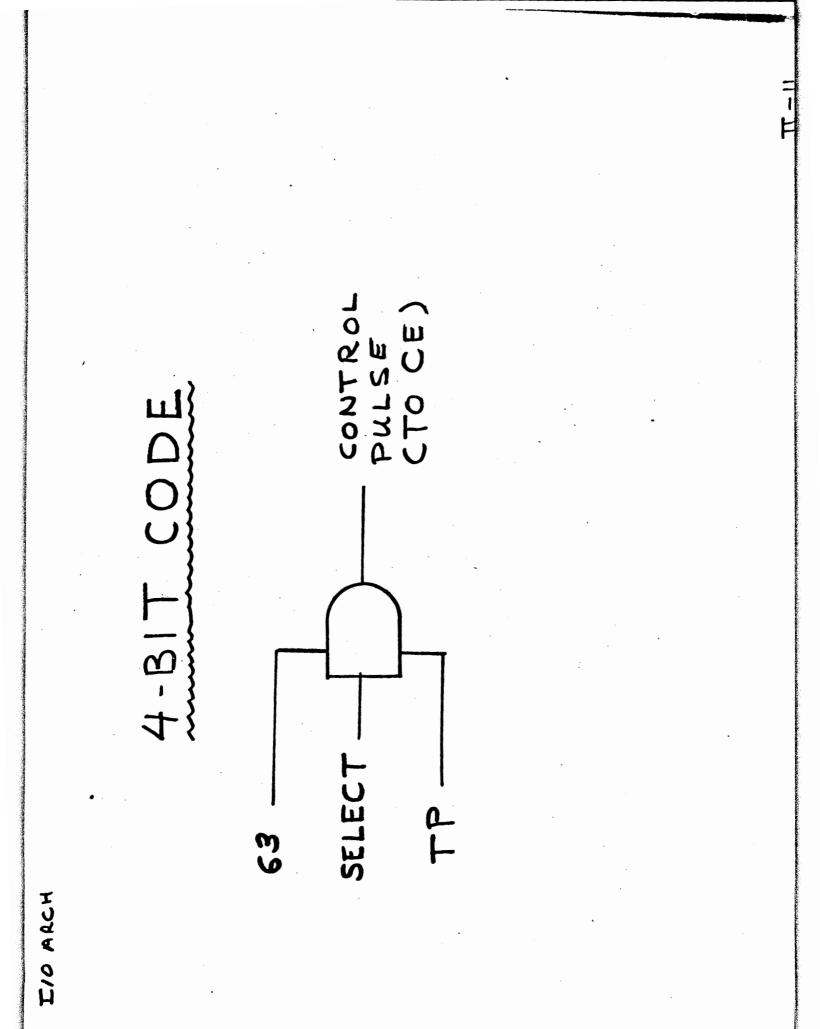

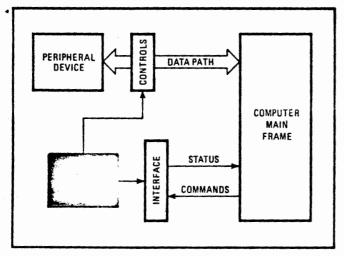

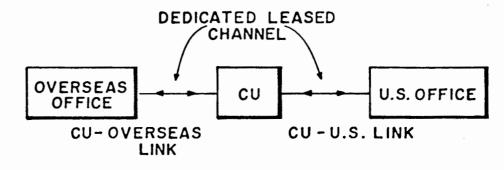

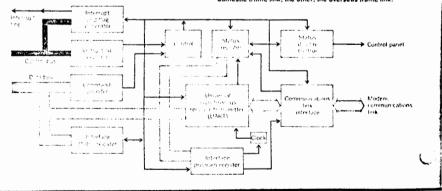

Figure 5 illustrates a large computer system in which each I/O device is controlled by a dedicated microcomputer, providing an intelligent buffer as well as a replacement for special-purpose logic. RAM, ROM, microcomputer, I/O device, and central computer interface circuits could readily be provided on a small set of LSI chips. The microcomputer direct memory access feature is extremely useful for highspeed block transfers in this type of system. Down-line loading of the microcomputer memory can immediately change its mode of operation. Off-line editing and maintenance are provided free. This type of large-scale system approach will become more popular in the future as microcomputer costs decrease.

The performance level of the simplified microcomputer described is more than adequate for the above types of systems as well as many others.

Figure 3. Calculator System

Figure 4. Six-Chip Stand-Alone System

### **Conclusions**

Much current microcomputer development effort appears to be directed toward improved performance. There is, however, a need for simple, minimum-cost structures that will satisfy large-volume applications which do not require minicomputer performance levels. These microcomputers must also be organized to reduce total system cost. One such microcomputer architecture has been developed. It promises low cost together with minimum external memory and system logic requirements. Hopefully, microcomputers of this class will accelerate the development of major new markets.

Today's high I/O device costs might be used as an argument against minimizing microcomputer cost. This is extremely shortsighted. The availability of ten-dollar microcomputer chips will, by itself, exert considerable pressure on the development of compatible low cost I/O and bulk storage devices. Even now there are many potential new products that demand minimum-cost microcomputers of the type described.

Because of its flexibility and potential for low-cost systems, a COS/MOS-LSI version of this microcomputer is currently being developed by RCA. SOS versions are also being investigated for applications requiring higher instruction execution rates. Both implementations are expected to find wide application in a variety of future products.

Acknowledgements. The following people have devoted considerable effort toward evaluating and developing software for the microcomputer described here: S. Heiss, A. R. Marcantonio, J. T. O'Neil, A. D. Robbi, P. M. Russo, R. O. Winder, and C. T. Wu. Without this effort, validation of the architecture would have been impossible.

Reprints of this article 0703041 are available at \$1.50 for the first copy and .50 for each additional copy. Send request and remittance, stating article number, to IEEE Computer Society, 5855 Naples Plaza, Suite 301, Long Beach, CA 90803.

### References

- G. Lapidus, "MOS/LSI Launches the Low Cost Processor," Spectrum, November 1972, pp. 33-40.

- 2. G. Sideris, "Microcomputers Muscle In," *Electronics*, March 1, 1973, pp. 63-64.

- M. E. Hoff, Jr., "Applications for Microcomputers in Instrumentation," 1973 IEEE Intercon Papers, Session 21/1.

- D. C. Hitt, G. H. Ottaway, and R. W. Shirk, "The Minicomputer - A New Approach to Computer Design," 1968 Fall Joint Computer Conference Proceedings, pp. 655-662.

- 5. R. W. Conn, "The Dinkiac 1," 1971 Spring Joint Computer Conference Proceedings, pp. 1-9.

- 6. G. Reyling, Jr., "LS1 Building Blocks for Parallel Digital Processors," 1973 IEEE Intercon Papers, Session 21/3.

- 7. "Backer Sought for Information Center," *Electronics*, March 29, 1973, pp. 33-34.

- "Personal Lifetime Computer Foreseen," *Electronics*, September 11, 1972, pp. 40-42.

- 9. KENBAK-1 Computer Programming Reference Manual, KENBAK Corporation, April 1971.

- "Putting Data on an Ordinary Audio Recorder," The Electronic Engineer, May 1972, p. DC-9.

- 11. E. Wolf, "Ratio Recording for Lower Cassette Recorder Cost," Computer Design, December 1972, p. 76.

Joe Weisbecker is with the RCA Laboratories in Princeton, New Jersey. Prior to joining the Lab in 1970, he was active in various engineering and product planning positions within RCA's Computer Systems Division. He has made major contributions to RCA computer development since 1953. During a three year sojourn with a smaller company, he developed a number of customized data communications terminals. Mr. Weisbecker is a graduate of Drexel University

and holds 19 patents with others pending. He is a member of IEEE and Eta Kappa Nu, and has received an RCA Laboratories Achievement Award.

His children have had a computer at home for several years which has reinforced his interest in low cost, widely available microcomputer systems.

# Primer on Microprocessors

PART I

Reprinted from ELECTRONIC PRODUCTS MAGA-ZINE, January 20, 1975 and February 17, 1975, 645 Stewart Avenue, Garden City, New York 11530, 1975 United Technical Publications, Inc., a division of Cox Broadcasting Corporation.

Not since the development of the transistor in 1948 has any product or technology offered such an exciting promise of things to come as has the microprocessor. Applications span the entire realm of electronics and extend into new areas where existing technologies had never before penetrated. Although much has been written about these MSI/LSI integrated circuits, Electronic Products Magazine felt it was time for an article that concentrated heavily on microprocessor basics. Both users and manufacturers agreed emphatically. The material that forms the basis for our two part feature was originally prepared by National Semiconductor to train its field engineers. We think you'll find the presentation interesting and informative.

| _ | <br> |  |  |

|---|------|--|--|

|   |      |  |  |

|   |      |  |  |

Since the microprocessor is a computer in IC form, a

ly carryi data exp tinuon so

good place to start is with computers. Simply put, a computer is a device capable of automatically carrying out a sequence of operations on data expressed in discrete (digital) or continuous (analog) form. Its purpose is to

> solve a problem or class of problems; it may be one of control, analysis, or a combination of the two. In digital computers, numbers are represented by the presence of voltage levels or pulses on given lines. A single line defines one bit (short for binary digit or a base-2 number). A group of lines considered together is called a "word"; a

word may represent a computational quantity (operand) or it may be a directive specifying how the machine is to operate on computational quantities.

To accomplish automated computation or control, the computer must perform various internal functions. The most obvious is to do arithmetic type of operations (add, subtract, etc.) on two operands. The section performing this function is the Arithmetic Unit (AU).

Something must control the arithmetic unit to make it follow the specific sequence of operations necessary to solve a given problem. In other words, a sequencing mechanism is required; furthermore, if the computer is to be programmed, the sequencer must also be programmable. Some storage is necessary in which to hold the required sequence of operations before beginning a computation. The sequencer can be separated into two functional units: program storage and control.

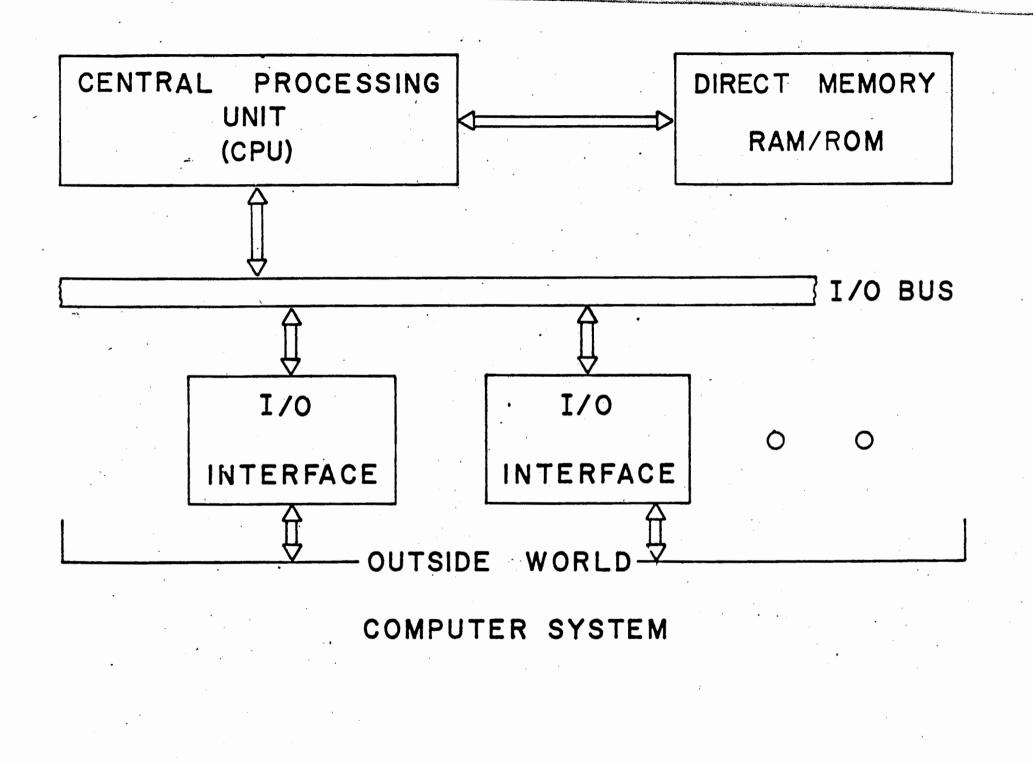

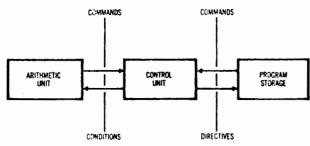

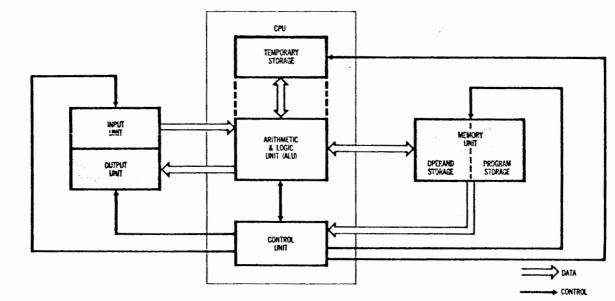

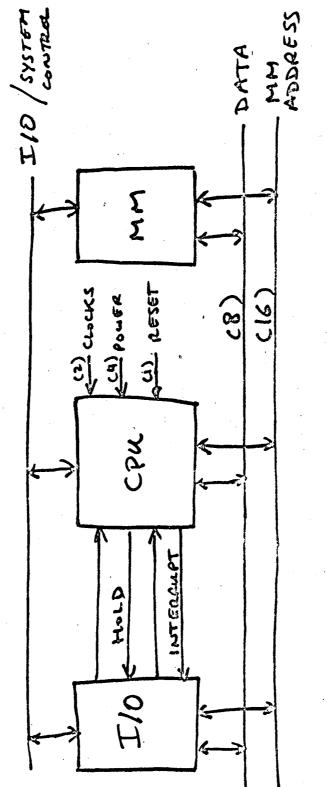

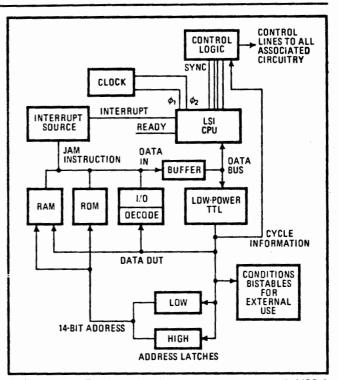

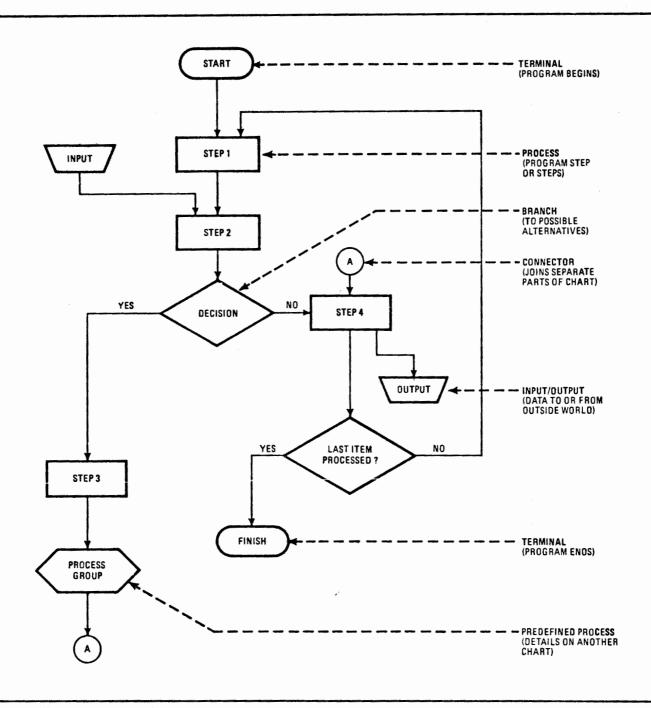

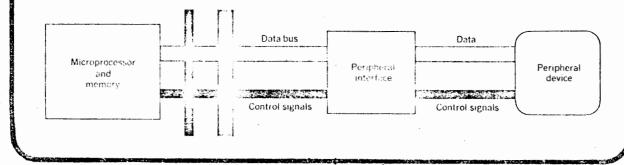

The control unit can be viewed as sensing external conditions and issuing commands to other machine elements. For example, the control unit sends commands to the arithmetic unit to initiate arithmetic operations, or sends commands to the program storage, which causes it to look-up the next program directive. The control unit senses such conditions as the completion of an arithmetic operation, the sign of a result, and the presence of stop/start signals from the computer operators. The machine just defined is represented in block diagram form in Fig. 1.

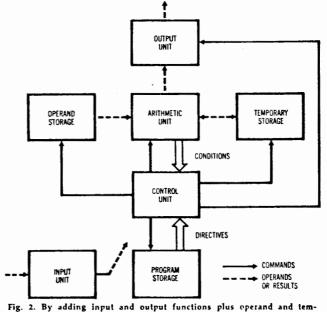

From the diagram, it is evident that no provision has been made to input data (operands) into the machine or to output the results of operations on these operands. Furthermore, no temporary storage has been provided to hold the intermediate or partial results of computations as well as the operands themselves. These items can now be added to complete the computer (Fig. 2). The input unit is indicated, but its connection is left unspecified until the interface is determined.

### Basic elements of a computer

When the completed machine is inspected, some potential redundancies are noted. There are three separate storage elements: operand, program and temporary. Could all three be combined into one storage unit or memory, and simply partitioned into three segments? Almost; but it will be more efficient if the temporary storage is maintained as a separate element and operand and program storage combined into one main memory unit. Such a simplification yields a more traditional looking representation of a computer (Fig. 3).

The four basic elements of all programmable computers emerge:

• Memory — A storage unit. In modern computers, memories are implemented with semiconductor or magnetic core systems. Memories can be read-only (ROM), for program storage, or read/write random access (RAM) for program, operand or temporary storage. Data is usually stored in binary form.

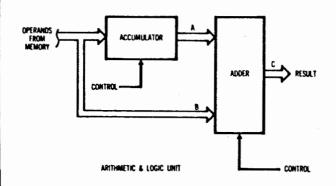

Fig. 1. In this rudimentary microprocessor, the control unit sends commands to the arithmetic unit to initiate arithmetic operations, or sends commands to program storage to look up the next instruction. • Arithmetic unit — Often referred to as the arithmetic and logic unit (ALU); it performs the arithmetic operations on operands or provides partial results within the computer.

• Control unit — Referred to as the brain of any computer because it coordinates all units of the computer in a timed, logical sequence. In fixed-instruction computers, this unit receives directives from the program memory (hereafter directives will be called "instructions" since they instruct the computer what actions to take and when to take them). These instructions are in sequences, called programs. They reside in the memory and are referred to as software. The control unit is closely synchronized to the memory cycle speed and the execution time of each fixed instruction is often a multiple of the memory speed.

• Input/Output — The means by which the computer communicates with a wide variety of devices, referred to as peripherals. They include switches, indicator lamps, teletypewriters, CRT's, magnetic or paper tape units, line printers, A/D or D/A converters, card readers and punches, communication modems, etc. The I/o lines can be connected to intermediate storage devices for use with mass memories, including magnetic discs, magnetic drums and large-scale RAM systems.

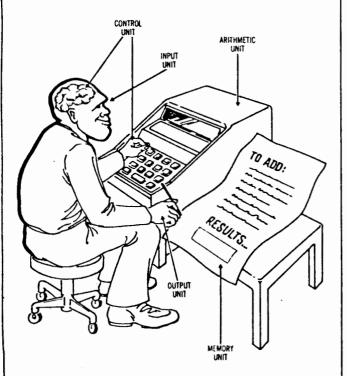

To illustrate the operation of this microprocessor, or digital computer, compare two systems for solving simple mathematical expressions, both composed of the classic elements of a computer: memory unit, arithmetic unit, control unit, and input/output unit.

The first such system (Fig. 4) is a man with a cal-

culator. The program and operand storage (memory) is the piece of paper containing a list of instructions for the man, the arithmetic unit is the calculator, the control unit is the man's brain and fingers, the input unit is his eyes and the output unit is his hand.

Examine the directions (program) that the man is to follow to solve a simple addition problem (note that this computer is externally programmed).

To add:

- 1. Clear calculator

- 2. Enter Operand #1 into calculator

- 3. Depress + key

- 4. Enter Operand #2 into calculator

- 5. Depress = key

- 6. Read and record result

- 7. Halt

This program would be applicable to any pair of operands to be added. But consider each step the man/calculator executes in solving the problem. For simplicity's sake, assume the problem to be solved is 6 + 2 = ?; therefore, Operand #1 = 6 and Operand #2 = 2:

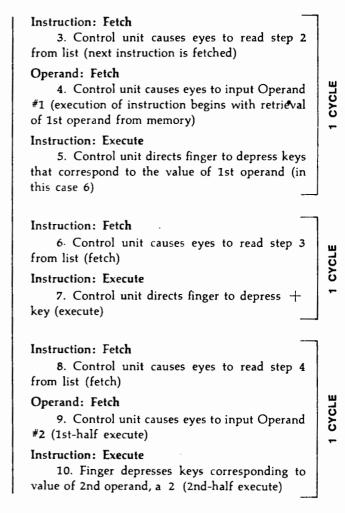

### Instruction: Fetch

1. Control unit (brain) causes eyes to read step 1 from list of directions (first instruction is fetched from memory)

### Instruction: Execute

2. Control unit directs fingers to depress "clear" key (first instruction is executed)

CYCLE

Fig. 3. By rearranging the elements shown in Fig. 2 the microprocessor reveals its conventional computer structure.

### IC Update

| Instruction: Fetch<br>11. Read step 5                                     | CLE    |

|---------------------------------------------------------------------------|--------|

| Instruction: Execute                                                      | ζ      |

| 12. Finger directed to depress $=$ key                                    | -      |

| Instruction: Fetch                                                        |        |

| 13. Read step 6                                                           | л<br>Ц |

| Instruction: Execute                                                      | CVCL   |

| 14. Hand outputs result by recording it in proper place on sheet of paper | -      |

|                                                                           |        |

| Instruction: Fetch                                                        | щ      |

| 15. Read step 7                                                           | ក្ម    |

| Instruction: Execute                                                      | S      |

| 16. Halt.                                                                 | -      |

The computer has executed its program, outputted the result and halted; the operation is complete. Note that each step is identified as being one of three types: instruction fetch, operand fetch or instruction execute. Also the cycles, the basic unit of machine timing, are identified. As a minimum, a cycle consists of one instruction fetch and one instruction execute; if a stored operand is involved, an operand fetch is required be-

Fig. 4. In this non-traditional representation of a computer, the man performs input/output and control functions, while the calculator serves as the arithmetic unit and the paper provides memory.

tween the instruction fetch and the execute subcycles.

A cycle is the time required by a computer to fetch, decode or execute one program step (instruction). Cycle times range from 200 nsec to several hundred microseconds. In minicomputers, machine cycle time is usually equal to memory cycle time, that is, a mini. that touts a 1.2  $\mu$ sec cycle time actually would have a 2.4 or 3.6  $\mu$ sec cycle instruction execution time.

### Microcomputer performance criteria

In microcomputers, the basic time interval is the microcycle. Since both the instruction fetch and instruction execute subcycles are each comprised of one or more microcycles, depending on the machine and instruction, the cycle time calculation becomes ambiguous and complex. To illustrate, consider a microcomputer that requires two microcycles to fetch an instruction, one microcycle to decode, and one microcycle to execute a "register add" instruction, two microcycles to execute a "jump to subroutine" instruction, etc. If we assume a 2  $\mu$ sec microcycle, this machine would require a cycle time of 6  $\mu$ sec to add two registers (3 microcycles) or 8  $\mu$ sec to jump to subroutine (4 microcycles). Confused? Don't feel bad; so is everyone else!

The point is: Cycle speed or cycle time alone is not a valid evaluation criterion for a computer, and especially not for a microcomputer. To provide a performance indicator, the efficiency of the instruction set must also be considered — what can an instruction really do and how long does it take to fetch it, execute it and be ready to fetch the next instruction?

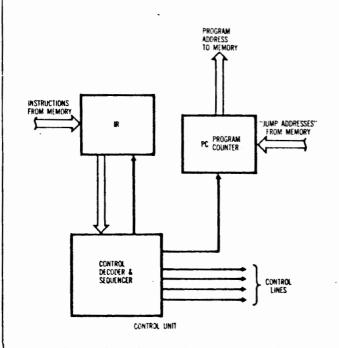

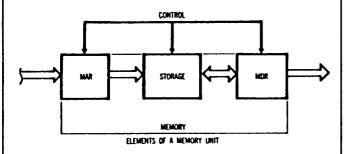

Now, look at a classic stored-program computer (Fig. 9) and see how it might be used to solve the same problem. The memory is composed of storage space for a large number of "words," with each storage space identified by a unique address. The word stored at a given address might be either computational data (operand) or an instruction (such as add, read from memory, etc.). Two temporary storage registers, each capable of containing one word, are included in the memory. These registers are designated as Memory Address Register (MAR) and Memory Data Register (MDR). The MAR contains the address where information is to be read from memory or written (stored) into memory, while the MDR contains the data being exchanged with memory.

The simplest ALU consists of an adder and an accumulator. The adder adds (or performs similar logical operations, e.g., OR) two inputs, A and B, and produces the output. The accumulator holds intermediate results of a computation or numbers for a pending computation. The accumulator is the temporary storage to which we've been referring, the storage that, for reasons of efficiency, was not included in the main memory. The remainder of the CPU, the control portion, is implemented using an instruction register (IR), a control decoder and sequencer, and a program counter (PC). A machine instruction is transferred from program storage memory into the IR and is subsequently interpreted by the decoder/sequencer, which issues the appropriate control pulses to the other computer elements. The PC contains, at any given time, the address in memory of the next instruction. This counter is normally incremented by one immediately following the reading of a new instruction. The PC contents can be replaced by the contents of a specified memory location if the last instruction was of the jump class. This causes the next instruction to be read from a program-specified location instead of from the next sequential location.

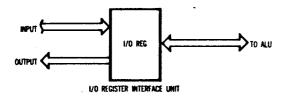

Finally, a means of input/output (I/O) is provided via an I/O register, through which data exchanges take place with external, or peripheral devices. Voila! A complete computer.

Let's continue the analysis by executing the program described below (note this is essentially the same problem used to illustrate the man/calculator):

"Read in an operand from the 1/0. Store it in memory location 50. Read in another operand from the 1/0. Store it in memory location 51. Add the two numbers together. Store the result in memory location 60, and halt."

Fig. 5. In the control unit, the instruction register receives the machine instructions from program storage. These are then interpreted by the decoder/sequencer, which controls the various microprocessor elements.

Here is a program to execute this task; it is stored in consectutive memory locations beginning at address location 100.

| Instruction (contents)      |

|-----------------------------|

| Input to accumulator        |

| Store accumulator at 50     |

| Input to accumulator        |

| Store accumulator at 51     |

| Add accum Loc. 50           |

| Place result in accumulator |

| Store accumulator at 60     |

| Halt                        |

|                             |

To execute the program, the program counter points to each instrument in turn, starting at 100. The processor fetches the instruction, decodes it, and finally executes it i none or more microcycles. When the microprocessor reaches 106, the operation is complete. No human intervention was required — every operation was automatic. All computers, regardless of their size or intended purpose, operate in a similar manner. It must be emphasized, however, that many variations are possible within this basic architectural frame-work.

### Variations on a theme

Common improvements, additions and/or alternations to the classic architecture described above include multiple accumulators, sophisticated I/O structures, index registers, indirect addressing, interrupts, pushdown stacks and microprogrammed control units. Such features can enhance a microprocessor's capabilities and are often the basis for comparisons between various machines, as well as providing a theme for competitive advertising and salesmanship. In view of these three facts, a discussion of basic computer variations follows: Accumulators, multiple — By definition, an accumulator provides a temporary storage medium. Temporary storage allows programs to execute faster and more efficiently by obviating the need to store partial or intermediate results in main memory and subsequently to retrieve them for use in additional computations. Multiple accumulator registers allow several partial results to be maintained at the computer's fingertips, thereby eliminating the many program steps that would otherwise be required to store and then retrieve data (shorter programs cost less to write, less to store and execute faster than longer. programs). Four accumulators are able to provide a great deal of programming and operational versatility, and it is often considered an optimum number.

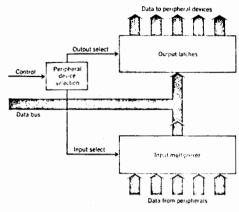

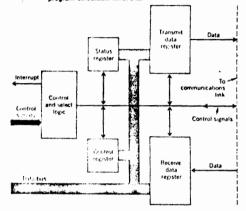

I/O structures — A basic input/output system provides a single input port and a single output port. A port allows transfer of one word of data across the computer's boundary. More sophisticated 1/0 units facilitate the use of multiple input and output ports, allowing virtually simultaneous communication with many peripheral devices. Another powerful I/O technique, referred to as DMA (for direct memory access), allows peripheral devices to transfer data directly into and out of memory, independent of the control unit and the operating program. This contrasts to the more conventional programmed I/O, where an explicit program instruction is required for any data transfer. The DMA technique facilitates faster data exchanges with memory, with fewer program steps, and is considered most applicable to bulk storage device (disc) interfaces and computer-to-computer connections. Contrary to occasional misuse of the term, DMA is not a uniquely defined off-the-shelf circuit, but can be implemented in a variety of ways in any general purpose computer.

Index registers — This feature provides programming flexibility by providing the user with more memory addressing modes. As a rule, when a programmer wishes to retrieve an operand from memory, he specifies its address in the instruction that calls for work to be performed on that operand (e.g., add it to an accumulator). The presence of an index register(s) allows the programmer to modify or index the operand address with the number contained in the register. Typically, the operand address from the instruction

Fig. 6. Input/output register interface unit. This component provides the data exchange link between the microprocessor and the outside world.

Fig. 7. Elements of a memory unit. In the operation of a memory, the MAR contains the address where information is to be stored or read. The MDR holds the data to be stored or receives the data as it is read. would be added to the content of the index register. Such a feature greatly simplifies the transfer of an array or field of data into or out of memory. Machines with two index registers offer enhanced programming versatility over machines with a single register.

Indirect addressing -- This is done when the address contained in the instruction specifies only the address of a memory word, which itself, specifies the operand address. An indirect address is an address in an instruction that indicates the location of the address of the referenced operand. Think of it as a computerized treasure hunt --- the instruction does not tell the location of the "treasure" (operand), but tells where to go to find a clue that gives its location. Multilevel indirection is possible, although not considered necessary. Here the system jumps through two or more clues until the operand is found. Indirect addressing provides great programming flexibility by allowing operand address to be continuously modified by the program. Interrupts - A machine operates under its own control but frequently it is desirable to have an external event cause the computer to shift its attention to another problem. This can be done in many ways:

- The computer program can include a section that causes it to look for possible external events each time it cycles. This may consume a lot of memory, make the computer operate its program more slowly and may not permit the computer to respond quickly to the external event.

- Interrupt signals may be forced into the computer. This requires extensive programming to insure that, when the external event has been serviced, the computer can return to its prior location.

- The computer can have interrupt capability built into its hardware, thus allowing the computer to service the interrupt quickly, with a minimum expenditure of program and memory storage space.

Push-down stack — Or "Push-down, pop-up" stack, LIFO (last-in, first-out) stack, etc. This is a useful feature for the "nesting" of interrupts and subroutines. Nesting refers to the entry into a second (or third) interrupt service program or subroutine prior to completion of service or execution of the first. The stack stores the current program execution address (contents of PC) each time the computer is directed to a new ancillary task, thereby allowing the computer to return and clean-up unfinished work in reverse order. The stack is also useful for storing partial results of computations. (Subroutine: A set of instructions necessary to direct the computer to carry out a well-defined mathematical, logical or analytical operation, usually arranged so that control can be transferred to it from the main program and so that, at the conclusion of the subroutine, control reverts to the main program.)

Microprogrammed control unit — In a computer with a microprogrammed control unit (MCU), three of the basic elements are nearly identical to our classic fixed-instruction computer; the significant difference is that the control unit has its own memory. This control memory contains the stored sequence of control functions that dictate the end-user architecture and the instruction repertoire of the microprogrammed computer. Thus, the instruction set can be modified or increased to adapt the microprocessor to system needs.

Instructions are machine directives and are the prime constituent of programs. They are fetched oneat-a-time by the control unit, which then carries out the operation(s) indicated in the instruction.

Instructions for most modern computers can be grouped into eight functional classes: load/store, arithmetic, logical, skip, shifts, transfer of control, register and I/O. A brief description and example of each class follows.

Load/store — This instruction class performs the function of exchanging data between main memory and temporary storage registers (accumulator, index, etc.). Load transfers contents of a selected memory location into a designated register. Store reverses the operation. Typical class members include load, load indirect, store and store indirect.

Arithmetic — Almost self-explanatory; these instructions perform an arithmetic operation upon two operands, one of which is in a register and the other in memory; the result usually replaces the operand in the register. Typical members include add, subtract, multiply and divide.

**Logical** — These perform a logical operation on two operands, one of which is in a register and the other in

Fig. 8. This simple ALU contains an adder and an accumulator. The accumulator provides temporary storage. For example, here it can hold one operand while another is obtained from memory in order to perform addition. memory; the result usually replaces the operand in the register. Included are AND, OR, EXCLUSIVE-OR.

Example: Logical OR

| Operand 1: | 01101011 | (Register) |

|------------|----------|------------|

| Operand 2: | 00110010 | (Memory)   |

|            | 01111011 |            |

Skip — These are usually 2-phase instructions; that is, an arithmetic or logical operation is performed on one or two operands and the result is tested for a specific condition (e.g., positive). If the condition is met, the next sequential instruction in the program is skipped. Class members include: increment and skip if zero, decrement and skip if zero, skip if greater, and skip if not equal.

Example: Decrement and skip if zero

A specified memory location has 1 subtracted from it; if the result is equal to zero, the next instruction is skipped.

Example: Skip if not equal

The contents of the specified register are compared to the contents of a specified memory location; if the two contents are not exactly identical, the next instruction is skipped.

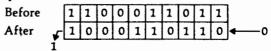

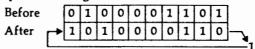

Shifts — The contents of a designated register are shifted one bit to the left or right. The bit position that is vacated can be filled with a zero (shift) or the bit that "fell off" the other end (rotate). Rotate is merely a circular shift.

Example: Shift left

Example: Rotate right

Transfer of control — This class of instruction causes the Program Counter (PC) to jump to an instruction — specified point in the program; that is, control of the computer is transferred to a new program element. Such transfers can be conditioned (based upon some operation and/or test) or unconditional. Conditional transfer includes Branch if Accumulator Positive, Branch if Condition, and Branch if Register = 0. Unconditional transfers include Jump, Jump to Subroutine, and Return From Interrupt. An immense amount of programming power is found or lost here.

Register --- Included here are instructions that per-

LEGENE DATA CONTROL (C) PROGRAM COUNTER (PC) NEMORY STORAGE MEMORY DATA ADDRESS OPERANDS PROGRAM RECISTER MOR RESID 6448 INSTRUCTION REGISTER (IR) MPUT 3 1/0 REG CONTROL ACCUMUS ATOR DECODER OUTPUT 🤇 AND SEDUENCER CONTROL LINES ADDER

Fig. 9. Combining Figures 5 through 8, the whole computer emerges. Memory is performed in various parts of this microprocessor. The memory register contains the address where information is to be read or stored, while the memory data register holds the data being exchanged with memory. The accumulator serves as a temporary storage unit.

form arithmetic or logical operations on the contents of two registers or after the content of a single register. Examples of two register instructions: Exchange Register and Stack, Register Add, Register Copy. Single Register instructions include Load Immediate, as well as Complement and Add Immediate. In an immediate instruction, the operand is inherently included.

Input/Output — An enormous variety of instructions are possible here; commoner instructions are those that transfer the content of a specific register to an output port (Register Out) or transfer the word appearing in an input port into a register (Register In).

There are as many instruction sets as there are computers, and it is quite difficult to say which are good and which are bad. The number of instructions is not a good indication of the power of a computer since each manufacturer counts differently. An instruction set that one manufacturer states has 43 instructions might be called 352, using another manufacturer's procedure (i.e., a register to register add might be counted as one instruction but in a machine with four registers it could be counted as sixteen).

One of the true measures of a machine is how many instructions it requires to execute a given "benchmark" program. It is important to note here that a computer with a microprogrammed control unit can be configured to execute any instruction; therefore the number of instructions required for a specific class of jobs can be minimized by tailoring the instruction set to the peculiar requirements of those jobs. Instruction efficiency is, in turn, related back to the architecture and word size of the individual computer.

The second part of this microprocessor primer covers such important topics as software, the advantages and disadvantages of microprocessors, and what to look for when choosing a microprocessor. Reprints of both Part 1 and Part 2 will be available next month. Check the February issue for further details.

# Primer on Microprocessors

### PART 2

Part 1 of this article described the basic elements of a microprocessor, told how a microprocessor functions and introduced the concept of instructions. It also concluded that microprocessors are computers in IC form, and that the terms "microprocessor" and "computer" can be used synonymously.

Taking this concept further, Part 2 deals with how to tell the microprocessor what to do. This, of course, can be implemented using hardware or software, but defining the solution is the most important and most difficult part.

Software is a term used to describe the programs that make a computer do a specific task. In fact, when used in the context of computers, the word software can be interchanged with the word program. In general, a program is a series of sequential steps that accomplish an objective. A list of directions to travel from Philadelphia to San Francisco is a program: Drive to Philadelphia airport, get parking ticket, park car, write parking section on back of ticket, take bus to terminal building, buy ticket at the United counter, check monitor to determine gate, go to gate, etc. If you followed such a list of instructions or program (and it was correct), you would end up in San Francisco. Note that the program asked you (the machine?) to pick up information in certain places and to act on it or to store information (writing down the parking section) to be retrieved and used later. Note also that the order of execution of each step is very important.

A computer is a device that can recognize and act on a predetermined set of instructions. Even though the specific set of instructions it can use is fixed by its design, a computer is general purpose because it can execute a list of these instructions (a program) to perform some functions, execute another list of instructions to perform some other function, and so on.

Since many applications for microcomputers can also accept a hardware solution, you should compare the design steps you would use for each. Since software is designed like hardware, it is interesting to note how similar the following steps are:

### Software:

- Define the problem and what data, inputs, and outputs are available and/or required for its solution.

- Determine the best form of the solution.

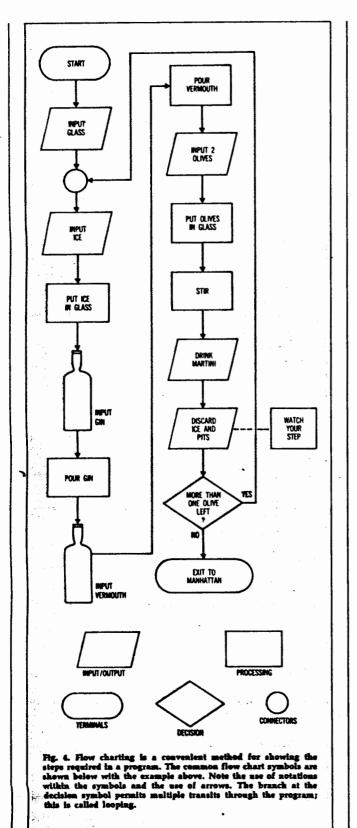

- Outline the method of solution on a flow chart.

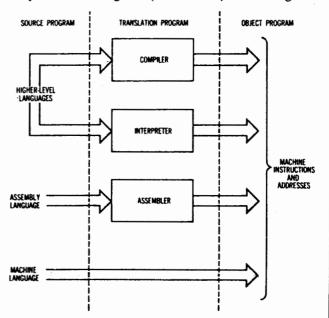

- Write the entire program, step by step, using the computer's instruction set. Assemble or compile the program (if necessary).

- Load the program into the computer memory and run it to test and debug.

Hardware:

- Define the program and what data, inputs and outputs are available and/or required for its solution.

- Determine the best form of the solution.

- Outline the method of solution on a flow chart. A static diagram can also be used.

- Draw up the detailed logic diagram using the available and compatible SSI, MSI and LSI functions.

Make wire lists, etc.

- Make wire lists, etc.

- Wire circuit boards; operate to test and debug.

Defining the program is the most important and probably the most difficult part of either solution. Step 2 depends largely on what resources the designer has at his disposal. This is the point where a decision will be made to go hardware or software. Note that for some design problems the flow chart for hardware and software may look the same.

Writing the program, Step 4, determines the incremental cost of the system, since it defines the amount of memory required to store the program. Since the number of instructions required to perform a certain function may be different for each computer on which the function is programmed, the cost of performing a given function will depend on the instruction set of the computer used.

The speed at which a given function may be performed depends on the instruction set of the computer as well as the actual time it takes the machine to cycle through a given instruction. Because of this, a machine that is considered fast may take much longer to perform a given function than a machine that is considered slow. This paradox is part of the reason why "proper CPU selection is not easy." One almost has to write his program for several machines before making an accurate comparison of cost and performance. These tests are sometimes referred to as benchmark tests.